## **LMV951**

# 1V, 2.7 MHz, Rail-to-Rail Input and Output Amplifier with Shutdown Option

# **General Description**

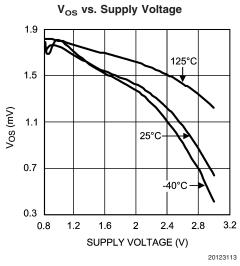

The LMV951 amplifier is capable of operating at supply voltages from 0.9V to 3V with guaranteed specs at 1V and 1.8V single supply.

The input common mode range extends to both power supply rails without the offset glitch and input bias current phase reversal inherent to most rail to rail input amplifiers.

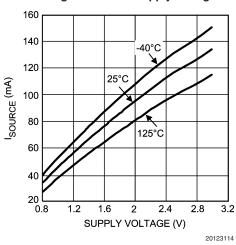

Contrary to a conventional rail to rail output amplifier the LMV951 has a buffered output stage providing an open loop gain which is relatively unaffected by resistive output loading. At 1V supply voltage, the LMV951 is able to source and sink in excess of 35 mA and offers a gain bandwidth product of 2.7 MHz.

In shutdown mode the LMV951 consumes less than 50 nA of supply current.

#### **Features**

(Typical 1.0V supply, unless otherwise noted)

- Guaranteed 1V single supply operation

- Wide bandwidth

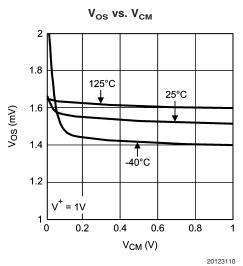

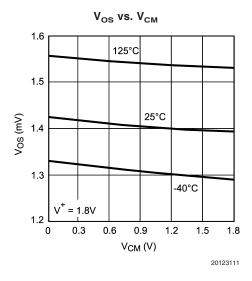

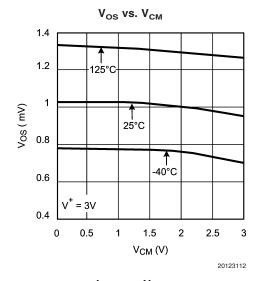

- No V<sub>OS</sub> glitch over the input CMVR

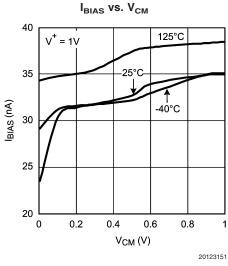

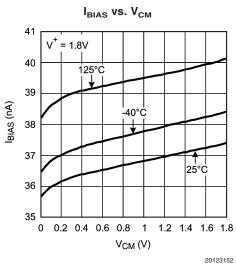

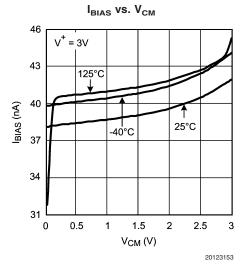

- No input I<sub>BIAS</sub> current reversal over V<sub>CM</sub> range

- Buffered output stage

- High output drive capability

- Output short circuit

- Sink current

Source current

35 mA 45 mA

■ Rail-to-rail buffered output

- @ 600 $\Omega$  load

- @ 2 k $\Omega$  load

32 mV from either rail 12 mV from either rail -40°C to 125°C

■ Temperature range -40°

# **Applications**

- Battery operated systems

- Battery monitoring

- Supply current monitoring

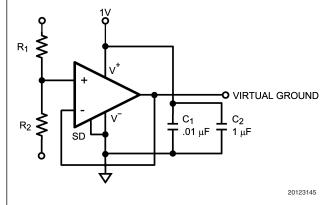

#### **Virtual Ground Circuit**

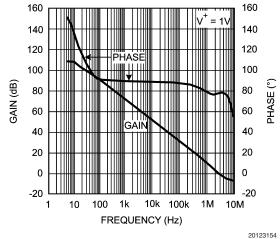

#### Open Loop Gain and Phase

20123134

Absolute Maximum Ratings (Note 1) please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2)

Voltage at Input/Output Pin

Human Body Model 2000V 200V Machine Model Supply Voltage (V<sup>+</sup> - V<sup>-</sup>) 3.1V V<sub>IN</sub> Differential ±0.3V Current at Input Pin ±10 mA +150°C Junction Temperature (Note 3) Mounting Temperature Infrared or Convection (20 sec) 235°C

## **Operating Ratings** (Note 1)

Temperature Range (Note 3) -40°C to +125°C 0.9V to 3V Supply Voltage Thermal Resistance  $(\theta_{JA})$  (Note 3) 170°C/W

## 1V Electrical Characteristics (Note 4)

Unless otherwise specified, all limits guaranteed for at  $T_A = 25$ °C,  $V^+ = 1$ ,  $V^- = 0$ V,  $V_{CM} = 0.5$ V, Shutdown = 0V, and  $R_L = 1 \text{ M}\Omega$ . **Boldface** limits apply at the temperature extremes.

$V^{+}$  +0.3V,  $V^{-}$  -0.3V

| Symbol             | Parameter                    | Conditions                                        | Min<br>(Note 5) | Typ<br>(Note 6) | Max<br>(Note 5) | Units   |

|--------------------|------------------------------|---------------------------------------------------|-----------------|-----------------|-----------------|---------|

| V <sub>OS</sub>    | Input Offset Voltage         |                                                   | (14010-3)       | 1.5             | 2.8             |         |

| VOS                | input officer voltage        |                                                   |                 | 1.0             | 3.0             | mV      |

| TC V <sub>os</sub> | Input Offset Average Drift   |                                                   |                 | 0.15            |                 | μV/°C   |

| I <sub>B</sub>     | Input Bias Current           |                                                   |                 | 32              | 80              | nA      |

|                    |                              |                                                   |                 |                 | 85              |         |

| los                | Input Offset Current         |                                                   |                 | 0.2             |                 | nA      |

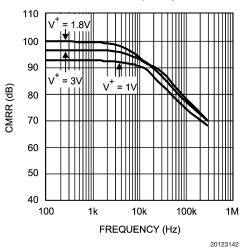

| CMRR               | Common Mode Rejection        | 0V ≤ V <sub>CM</sub> ≤ 1V                         | 67              | 77              |                 | dB      |

|                    | Ratio                        |                                                   | 55              |                 |                 |         |

|                    |                              | $0.1V \le V_{CM} \le 1V$                          | 76              | 85              |                 | u u u   |

|                    |                              |                                                   | 73              |                 |                 |         |

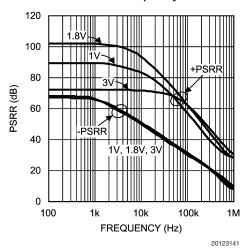

| PSRR               | Power Supply Rejection Ratio | $1V \le V^{+} \le 1.8V, V_{CM} = 0.5V$            | 70              | 92              |                 |         |

|                    |                              |                                                   | 67              |                 |                 | dB      |

|                    |                              | $1V \le V^+ \le 3V, V_{CM} = 0.5V$                | 68              | 85              |                 |         |

|                    |                              |                                                   | 65              |                 |                 |         |

| $V_{CM}$           | Input Common-Mode Voltage    | CMRR ≥ 67 dB                                      | 0               |                 | 1.2             | V       |

|                    | Range                        | CMRR ≥ 55 dB                                      | 0               |                 | 1.2             |         |

| A <sub>V</sub>     | Large Signal Voltage Gain    | $V_{OUT} = 0.1V \text{ to } 0.9V$                 | 90              | 106             |                 |         |

|                    |                              | $R_L = 600\Omega$ to 0.5V                         | 85              |                 |                 | - dB    |

|                    |                              | $V_{OUT} = 0.1V \text{ to } 0.9V$                 | 90              | 112             |                 |         |

| .,                 |                              | $R_L = 2 k\Omega$ to 0.5V                         | 86              |                 |                 |         |

| $V_{OUT}$          | Output Voltage Swing High    | $R_L = 600\Omega$ to 0.5V                         | 50<br><b>62</b> | 25              |                 |         |

|                    |                              | $R_L = 2 \text{ k}\Omega \text{ to } 0.5\text{V}$ |                 | 10              |                 |         |

|                    |                              | $H_{L} = 2 \text{ K} 10  0.5         $            | 25<br><b>36</b> | 12              |                 | mV from |

|                    | Output Voltage Swing Low     | $R_L = 600\Omega$ to 0.5V                         | 70              | 32              |                 | rail    |

|                    |                              | n <sub>L</sub> = 00052 to 0.37                    | 85              | 52              |                 | l lan   |

|                    |                              | $R_L = 2 \text{ k}\Omega \text{ to } 0.5\text{V}$ | 35              | 10              |                 |         |

|                    |                              |                                                   | 40              |                 |                 |         |

| I <sub>OUT</sub>   | Output Short Circuit Current | Sourcing                                          | 20              | 45              |                 |         |

| 001                | (Note 7)                     | $V_{O} = 0V, V_{IN(DIFF)} = \pm 0.2V$             | 15              |                 |                 | mA      |

|                    |                              | Sinking                                           | 20              | 35              |                 |         |

|                    |                              | $V_O = 1V$ , $V_{IN(DIFF)} = \pm 0.2V$            | 13              |                 |                 |         |

| I <sub>S</sub>     | Supply Current               | Active Mode V <sub>SD</sub> <0.4V                 |                 | 370             | 480             |         |

|                    |                              |                                                   |                 |                 | 520             |         |

|                    |                              | Shutdown Mode V <sub>SD</sub> >0.6V               |                 | 0.01            | 1.0             | μA      |

|                    |                              |                                                   |                 |                 | 3.0             |         |

| SR                 | Slew Rate                    | (Note 8)                                          |                 | 1.4             |                 | V/µs    |

# 1V Electrical Characteristics (Note 4) (Continued)

Uness otherwise specified, an imite guaranteed for at  $T_A = 25^{\circ}C$ ,  $V^+ = 1$ ,  $V^- = 0V$ ,  $V_{CM} = 0.5V$ , Shutdown = 0V, and  $R_L = 1$  M $\Omega$ . Boldface limits apply at the temperature extremes.

| Symbol          | Parameter                      | Conditions                                            | Min      | Тур      | Max      | Units   |

|-----------------|--------------------------------|-------------------------------------------------------|----------|----------|----------|---------|

|                 |                                |                                                       | (Note 5) | (Note 6) | (Note 5) |         |

| GBWP            | Gain Bandwidth Product         |                                                       |          | 2.7      |          | MHz     |

| e <sub>n</sub>  | Input - Referred Voltage Noise | f = 1 kHz                                             |          | 25       |          | nV/ √Hz |

| i <sub>n</sub>  | Input-Referred Current Noise   | f = 1 kHz                                             |          | 10       |          | pA/ √Hz |

| THD             | Total Harmonic Distortion      | $f = 1 \text{ kHz}, A_V = 1, R_L = 1 \text{ k}\Omega$ |          | 0.02     |          | %       |

| I <sub>SD</sub> | Shutdown Pin Current           | Active Mode, V <sub>SD</sub> = 0V                     |          | .001     | 1        |         |

|                 |                                | Shutdown Mode, V <sub>SD</sub> = 1V                   |          | .001     | 1        | μA      |

| V <sub>SD</sub> | Shutdown Pin Voltage Range     | Active Mode                                           | 0        |          | 0.4      | V       |

|                 |                                | Shutdown Mode                                         | 0.6      |          | 1        | V       |

# 1.8V Electrical Characteristics (Note 4)

Unless otherwise specified, all limits guaranteed for at  $T_A = 25^{\circ}C$ ,  $V^+ = 1.8V$ ,  $V^- = 0V$ ,  $V_{CM} = 0.9V$ , Shutdown = 0V, and  $R_L = 1~M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                             | Conditions                                                                     | Min<br>(Note 5)      | Typ<br>(Note 6) | Max<br>(Note 5)   | Units   |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------|----------------------|-----------------|-------------------|---------|

| V <sub>OS</sub>    | Input Offset Voltage                  |                                                                                | (1333 2)             | 1.5             | 2.8<br><b>3.0</b> | mV      |

| TC V <sub>os</sub> | Input Offset Average Drift            |                                                                                |                      | 0.15            | 0.0               | μV/°C   |

| Ів                 | Input Bias Current                    |                                                                                |                      | 36              | 80<br><b>85</b>   | nA      |

| l <sub>os</sub>    | Input Offset Current                  |                                                                                |                      | 0.2             |                   | nA      |

| CMRR               | Common Mode Rejection<br>Ratio        | $0V \le V_{CM} \le 1.8V$                                                       | 82<br><b>80</b>      | 93              |                   | dB      |

| PSRR               | Power Supply Rejection Ratio          | $1V \le V^+ \le 1.8V, V_{CM} = 0.5V$                                           | 70<br><b>67</b>      | 92              |                   | dB      |

|                    |                                       | $1V \le V^+ \le 3V, V_{CM} = 0.5V$                                             | 68<br><b>65</b>      | 85              |                   | uБ      |

| $V_{CM}$           | Input Common-Mode Voltage Range       | CMRR ≥ 82 dB  CMRR ≥ 80 dB                                                     | -0.2<br>- <b>0.2</b> |                 | 2<br><b>2</b>     | V       |

| A <sub>V</sub>     | Large Signal Voltage Gain             | $V_{OUT} = 0.2 \text{ to } 1.6V$<br>$R_L = 600\Omega \text{ to } 0.9V$         | 86<br><b>83</b>      | 110             |                   | - dB    |

|                    |                                       | $V_{OUT} = 0.2 \text{ to } 1.6V$<br>$R_L = 2 \text{ k}\Omega \text{ to } 0.9V$ | 86<br><b>83</b>      | 116             |                   |         |

| V <sub>OUT</sub>   | Output Voltage Swing High             | $R_L = 600\Omega$ to 0.9V                                                      | 50<br><b>60</b>      | 33              |                   |         |

|                    |                                       | $R_L = 2 \text{ k}\Omega \text{ to } 0.9\text{V}$                              | 25<br><b>34</b>      | 13              |                   | mV from |

|                    | Output Voltage Swing Low              | $R_L = 600\Omega$ to 0.9V                                                      | 80<br><b>105</b>     | 54              |                   | rail    |

|                    |                                       | $R_L = 2 \text{ k}\Omega \text{ to } 0.9 \text{V}$                             | 35<br><b>44</b>      | 17              |                   |         |

| I <sub>OUT</sub>   | Output Short Circuit Current (Note 7) | Sourcing $V_O = 0V$ , $V_{IN(DIFF)} = \pm 0.2V$                                | 50<br><b>35</b>      | 85              |                   | mA      |

|                    |                                       | Sinking $V_O = 1.8V, V_{IN(DIFF)} = \pm 0.2V$                                  | 45<br><b>25</b>      | 80              |                   | IIIA    |

| I <sub>S</sub>     | Supply Current                        | Active Mode V <sub>SD</sub> <0.5V                                              |                      | 570             | 780<br><b>880</b> | · μΑ    |

|                    |                                       | Shutdown Mode V <sub>SD</sub> >1.3V                                            |                      | 0.3             | 2.2<br><b>10</b>  | μΛ      |

1.8V Electrical Characteristics (Note 4) (Continued)

| Symbol          | Parameter                      | Conditions                                            | Min      | Тур      | Max      | Units   |

|-----------------|--------------------------------|-------------------------------------------------------|----------|----------|----------|---------|

|                 |                                |                                                       | (Note 5) | (Note 6) | (Note 5) |         |

| SR              | Slew Rate                      | (Note 8)                                              |          | 1.4      |          | V/µs    |

| GBWP            | Gain Bandwidth Product         |                                                       |          | 2.8      |          | MHz     |

| e <sub>n</sub>  | Input - Referred Voltage Noise | f = 1 kHz                                             |          | 25       |          | nV/ √Hz |

| i <sub>n</sub>  | Input-Referred Current Noise   | f = 1 kHz                                             |          | 10       |          | pA/ √Hz |

| THD             | Total Harmonic Distortion      | $f = 1 \text{ kHz}, A_V = 1, R_L = 1 \text{ k}\Omega$ |          | 0.02     |          | %       |

| I <sub>SD</sub> | Shutdown Pin Current           | Active Mode, V <sub>SD</sub> = 0V                     |          | .001     | 1        |         |

|                 |                                | Shutdown Mode, V <sub>SD</sub> = 1.8V                 |          | .001     | 1        | μΑ      |

| V <sub>SD</sub> | Shutdown Pin Voltage Range     | Active Mode                                           | 0        | ·        | 0.5      | V       |

|                 |                                | Shutdown Mode                                         | 1.3      |          | 1.8      | , v     |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

Note 3: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

Note 4: Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions is very limited self-heating of the

Note 5: All limits are guaranteed by testing or statistical analysis.

Note 6: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 7: The short circuit test is a momentary test, the short circuit duration is 1.5 ms

Note 8: Number specified is the average of the positive and negative slew rates.

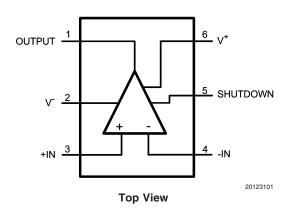

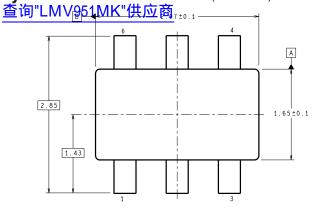

## Connection Diagram

#### 6-Pin SOT23

# **Ordering Information**

| Package      | Part Number | Package Marking | Transport Media        | NSC Drawing |  |

|--------------|-------------|-----------------|------------------------|-------------|--|

| 6-Pin SOT23  | LMV951MK    | AS3A            | 1k Units Tape and Reel | MK06A       |  |

| 0-FIII 30123 | LMV951MKX   | ASSA            | 3k Units Tape and Reel |             |  |

# Simplified Schematic 查询"LMV951MK"供应商 SHUTDOWN 5 GENERATOR IN+ BELOW V GENERATOR 20123104

Typical Performance Characteristics Unless otherwise specified, all limits are guaranteed for T<sub>A</sub> = 可"L2MO/95 HMK"以共政的V<sub>CM</sub> = V\*/2 = V<sub>O</sub>. Boldface limits apply at the temperature extremes.

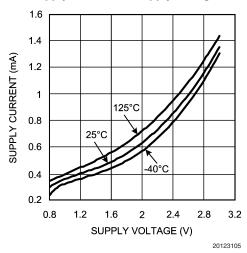

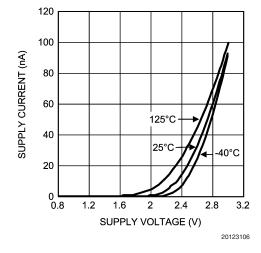

#### Supply Current vs. Supply Voltage

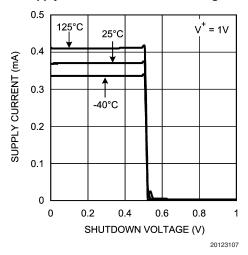

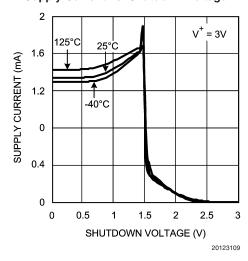

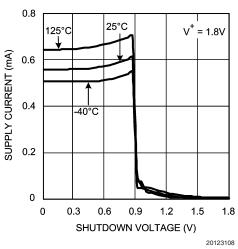

#### Supply Current vs. Shutdown Voltage

#### Supply Current vs. Shutdown Voltage

#### Supply Current vs. Supply Voltage in Shutdown Mode

#### Supply Current vs. Shutdown Voltage

Typical Performance Characteristics Unless otherwise specified, all limits are guaranteed for T<sub>A</sub> = 25 查询出MV95何MV。(出版 Boldface limits apply at the temperature extremes. (Continued)

#### Sourcing Current vs. Supply Voltage

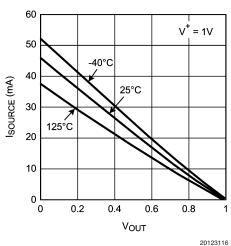

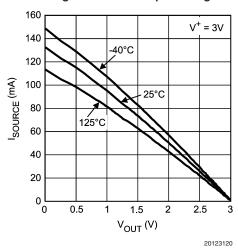

#### Sourcing Current vs. Output Voltage

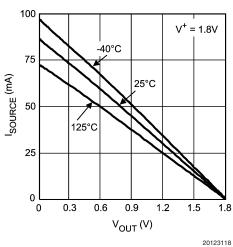

#### Sourcing Current vs. Output Voltage

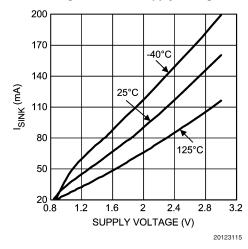

#### Sinking Current vs Supply Voltage

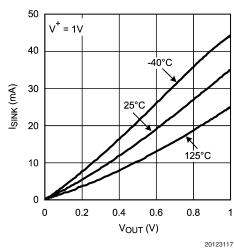

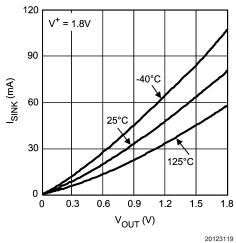

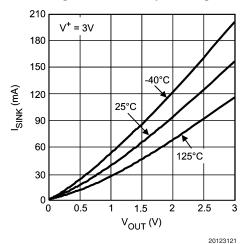

#### Sinking Current vs. Output Voltage

#### Sinking Current vs. Output Voltage

# Typical Performance Characteristics Unless otherwise specified, all limits are guaranteed for T<sub>A</sub> = 25 查询"上M V9510M K"。从为 富 = V<sub>O</sub>. Boldface limits apply at the temperature extremes. (Continued)

#### Sourcing Current vs. Output Voltage

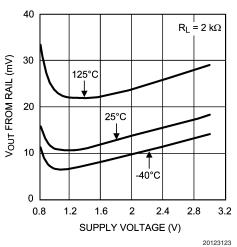

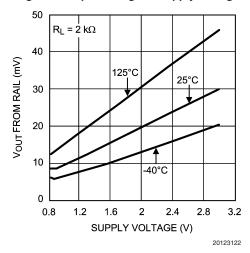

#### Positive Output Swing vs. Supply Voltage

#### Positive Output Swing vs. Supply Voltage

#### Sinking Current vs. Output Voltage

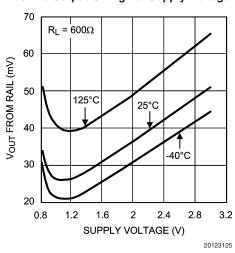

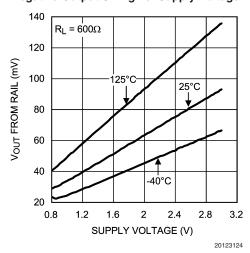

#### Negative Output Swing vs. Supply Voltage

#### Negative Output Swing vs. Supply Voltage

Typical Performance Characteristics Unless otherwise specified, all limits are guaranteed for T<sub>A</sub> = 间"L25/0/951/1/KV共政商/<sub>CM</sub> = V<sup>+</sup>/2 = V<sub>O</sub>. **Boldface** limits apply at the temperature extremes. (Continued)

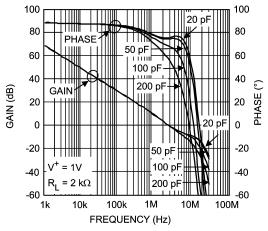

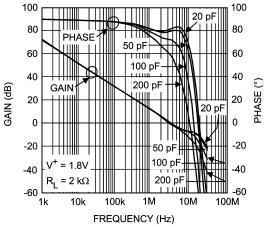

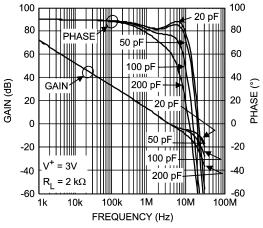

#### Open Loop Gain and Phase with Capacitive Load

#### Open Loop Gain and Phase with Capacitive Load

20123128

#### Open Loop Gain and Phase with Capacitive Load

20123130

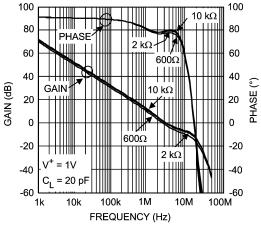

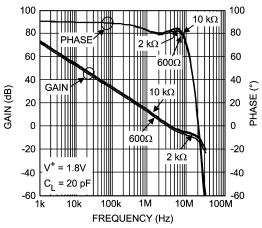

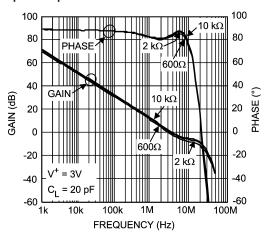

#### Open Loop Gain and Phase with Resistive Load

#### Open Loop Gain and Phase with Resistive Load

20123129

#### Open Loop Gain and Phase with Resistive Load

20123131

# Typical Performance Characteristics Unless otherwise specified, all limits are guaranteed for T<sub>A</sub> = 25 查询出MV95何MV5伊拉雷 = V<sub>O</sub>. Boldface limits apply at the temperature extremes. (Continued)

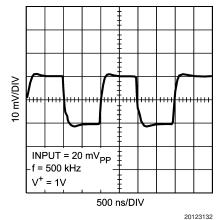

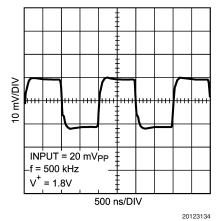

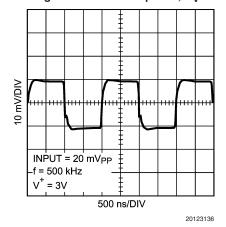

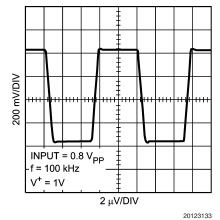

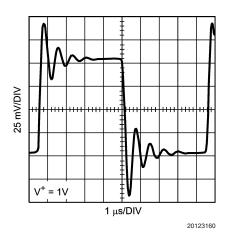

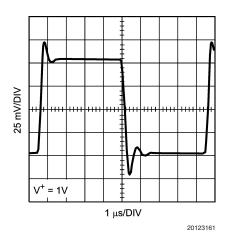

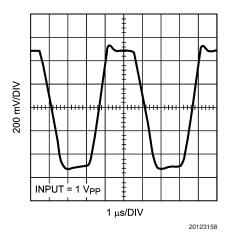

Small Signal Transient Response,  $A_V = +1$

Small Signal Transient Response,  $A_V = +1$

Small Signal Transient Response,  $A_V = +1$

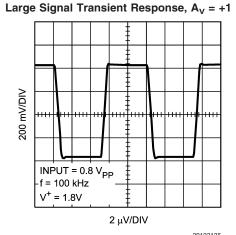

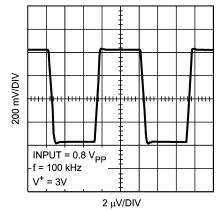

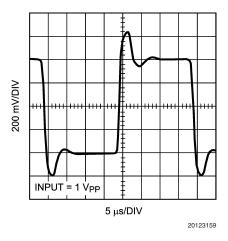

Large Signal Transient Response,  $A_V = +1$

Large Signal Transient Response,  $A_V = +1$

20123137

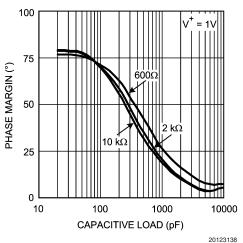

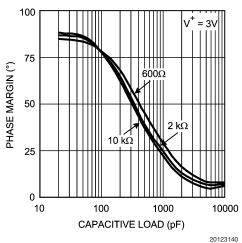

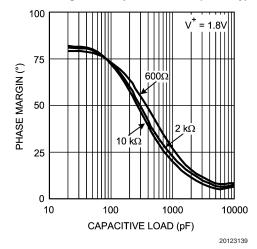

#### Phase Margin vs. Capacitive Load (stability)

#### Phase Margin vs. Capacitive Load (stability)

#### CMRR vs. Frequency

#### Phase Margin vs. Capacitive Load (stability)

PSRR vs. Frequency

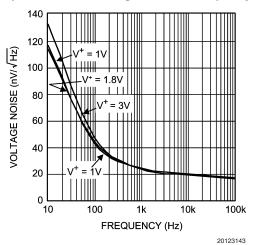

Input Referenced Voltage Noise vs. Frequency

Typical Performance Characteristics Unless otherwise specified, all limits are guaranteed for T<sub>A</sub> = 25 查询出MV95何MV5伊拉雷 = V<sub>O</sub>. Boldface limits apply at the temperature extremes. (Continued)

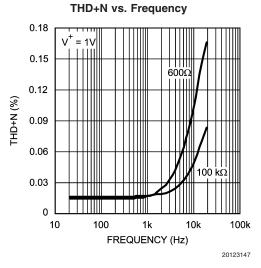

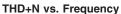

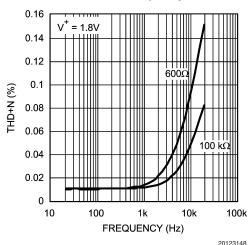

#### THD+N vs. Frequency

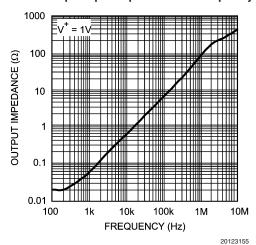

#### Closed Loop Output Impedance vs. Frequency

### **Application Information**

LMV951MK"供应商

# CIRCUIT DESCRIPTION AND ADVANTAGE OF THE LMV951

The LMV951 utilizes an internal voltage generator which allows for rail to rail input and output operation from 1 to 3V supplies. An internal switching frequency between 10 MHz and 15 MHz is used for generating the internal voltages.

The bipolar input stage provides rail to rail input operation with no input bias current phase reversal and a constant input offset voltage over the entire input common mode range.

The CMOS output stage provides a gain that is virtually independent of resistive loads and an output drive current in excess of 35 mA at 1V. A further benefit of the output stage is that the LMV951 is stable in positive unity gain at capacitive loads in excess of 1000 pF.

#### **Battery Operated Systems**

The maximum operating voltage is 3V and the operating characteristics are guaranteed down to 1V which makes the LMV951 an excellent choice for battery operated systems using one or two NiCd or NiMH cells. The LMV951 is also functional at 0.9V making it an appropriate choice for a single cell alkaline battery.

#### **Shutdown Capability**

While in shutdown mode, the LMV951 typically consumes less than 50 nA of supply current making it ideal for power conscious applications. Full functionality is restored within 3 µs of enable.

#### **Small Size**

The small footprint of the LMV951 package is ideal for high density board systems. By using the small 6-Pin SOT23 package, the amplifier can be placed closer to the signal source, reducing noise pickup and increasing signal integrity.

#### **Power Supply Bypassing**

As in any high performance IC, proper power supply bypassing is necessary for optimizing the performance of the LMV951. The internal voltage generator needs proper bypassing for optimum operation. A surface mount ceramic .01  $\mu F$  capacitor must be located as close as possible to the V $^+$  and V $^-$  pins (pins 2 and 6). This capacitor needs to have low ESR and a self resonant frequency above 15 MHz. A small tantalum or electrolytic capacitor with a value between 1  $\mu F$  and 10  $\mu F$  also needs to be located close to the LMV951.

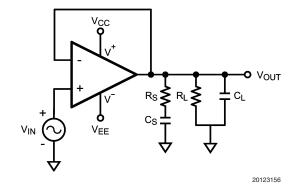

#### DRIVING CAPACITIVE LOAD

The unity gain follower is the most sensitive op amp configuration to capacitive loading; the LMV951 can drive up to 10,000 pF in this configuration without oscillation. If the application requires a phase margin greater than those shown in the datasheet graphs, a snubber network is recommended. The snubber offers the advantage of reducing the output signal ringing while maintaining the output swing which ensures a wider dynamic range; this is especially important at lower supply voltages.

FIGURE 1. Snubber Network to Improve Phase Margin

The chart below gives recommended values for some common values of large capacitors. For these values  $R_1 = 2 \text{ k}\Omega$ ;

| CL      | R <sub>s</sub> | Cs      |

|---------|----------------|---------|

| 500 pF  | 330Ω           | 6800 pF |

| 680 pF  | 270Ω           | 8200 pF |

| 1000 pF | 220Ω           | .015 μF |

FIGURE 2. 1000 pF and no Snubber

FIGURE 3. 1000 pF with Snubber

# Application Information (Continued)

# BRT TO WAY OF THE REPORT OF T

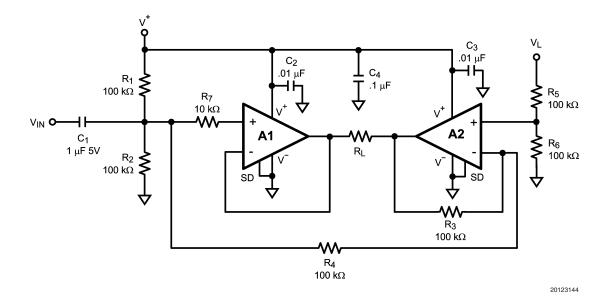

Some applications may benefit from doubling the voltage across the load. With V $^+$  = 1V a bridge configuration can provide a 2 V $_{PP}$  output to the load with a resistance as low as 300 $\Omega$ . The output stage of the LMV951 enables it to drive a load of 120 $\Omega$  and still swing at least 70% of the supply rails.

The bridge configuration shown in *Figure 4* enables the amplifier to maintain a low dropout voltage thus maximizing its dynamic range. It has been configured in a gain of 1 and uses the fewest number of parts.

Resistor values have been selected to keep the current consumption to a minimum and voltage errors due to bias currents negligible. Using the selected resistor values makes this circuit quite practical in a battery operated design.  $R_1,\,R_2$  and  $R_5,\,R_6$  set up a virtual ground that is half of V $^+$ . Note that the accuracy of the resistor values will establish how well the two virtual grounds match. Any errors in the virtual grounds will show as current across  $R_L$  when there is no input signal. AC coupling the input signal sets the DC bias point of this signal to the virtual ground of the circuit. Using the large resistor values with a 1  $\mu F$  capacitor (C<sub>1</sub>) sets the frequency rolloff of this circuit below 10 Hz.

FIGURE 4. Bridge Amplifier

- C<sub>2</sub> and C<sub>3</sub> are .01 μF ceramic capacitors that must be located as close as possible to pin 6, the V<sup>+</sup> pin. As covered in the power supply bypassing section these capacitors must have low ESR and a self resonant frequency above 15 MHz.

- C<sub>4</sub> is a 1 µF tantalum or electrolytic capacitor that should also be located close to the supply pin.

- To use the shutdown feature tie pin 5 of the two parts together and connect through a 470 kΩ resistor to V<sup>+</sup>.

Add a switch between pin 5 and ground. Closing the switch keeps the parts in the active mode, opening the switch sets the parts in the shutdown mode without adding any additional current to V<sup>+</sup>.

#### **VIRTUAL GROUND CIRCUIT**

The front page of this data sheet shows the LMV951 being used in a system establishing a virtual ground. Having a buffered output stage gives this part the ability to handle load currents higher than 35 mA at 1V.

$R_3$  and  $R_4$  are used to set the voltage of the virtual ground. To maintain low noise the values should be between 1  $k\Omega$  and 10  $k\Omega.$   $C_1$  and  $C_2$  provide the recommended bypassing for the LMV951. These caps must be placed as close as possible to pins 2 and 6.

#### TWO WIRE LINE TRANSMISSION

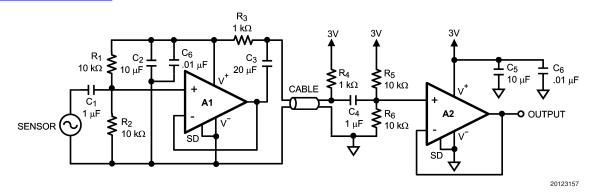

The robust output stage of the LMV951 makes it an excellent choice for driving long cables. The circuit shown below in *Figure 5* can drive a long cable using only two wires; power and ground.

When many sensors are located remotely from the control area the wiring becomes a significant expense. Using only two wires helps minimize the wiring expense in a large project such as an industrial plant. Figure 6 shows a 25 kHz signal after passing though 1000 ft. of twisted pair cable. Figure 7 shows a 200 kHz signal after passing through 50 ft. of twisted pair cable.

# Application Information (Continued) 询"LMV951MK"供应商

FIGURE 5. Two Wire Line Driver

FIGURE 6. 25 kHz Through 1000 ft.

FIGURE 7. 200 kHz Through 50 ft.

The power supply of 3V is recommended to power this system. A1 and A2 are set up as unity gain buffers. It is easy to configure A1 with the required gain if a gain of greater than one is required.  $C_1$  along with  $R_1$  and  $R_2$  are used to ensure

the correct DC operating point at the input of A1. C4 along with R<sub>5</sub> and R<sub>6</sub> are used to setup the correct DC operating point for A2.  $C_1$ ,  $C_3$ , and  $C_4$  have been selected to give about a 20% droop with a 1 kHz square wave input.

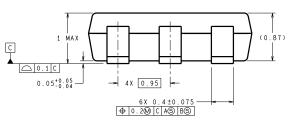

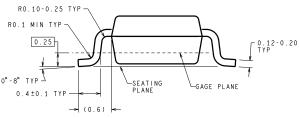

# Physical Dimensions inches (millimeters) unless otherwise noted

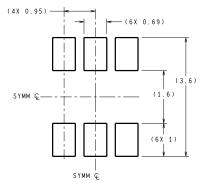

RECOMMENDED LAND PATTERN

**DIMENSIONS ARE IN MILLIMETERS**

MK06A (Rev D)

6-Pin SOT23 NS Package Number MK06A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe support@nec con

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560