The Infinite Bandwidth Company™

### MIC2551

### **USB Transceiver**

### **Final Information**

### **General Description**

The MIC2551 is a single chip transceiver that complies with the physical layer specifications of the Universal Serial Bus (USB) 2.0. It supports both full speed (12Mbps) and low speed (1.5Mbps) operation. It is also designed to operate down to 1.6V in order to be compatible with lower system voltages of most mobile systems.

### **Features**

- Compliant to USB Specification Revision 2.0 for full speed (12Mbs) and low speed (1.5Mbps) operation

- Compliant to IEC-61000-4.2 (Level 3)

- Separate I/O supply with operation down to 1.6V

- Integrated speed select termination supply

- Very-low power consumption to meet USB suspendcurrent requirements

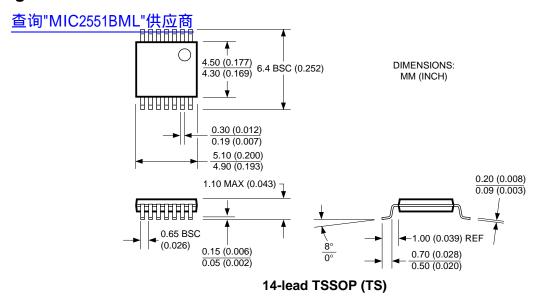

- Small TSSOP and MLF™ packages

- · No power supply sequencing requirements

- Software controlled re-enumeration

### **Applications**

- PDAs

- Palmtops

- · Cell phones

### **Ordering Information**

| Part Number | Package      |

|-------------|--------------|

| MIC2551BTS  | 14-Pin TSSOP |

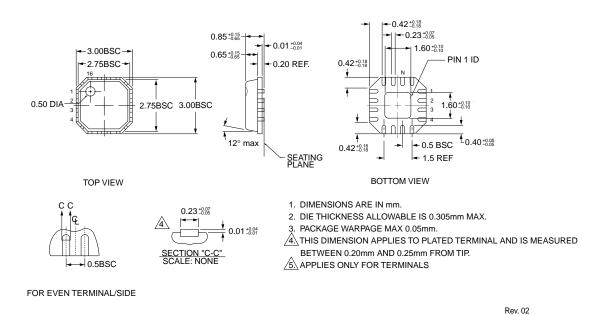

| MIC2551BML  | 16-Pin MLF™  |

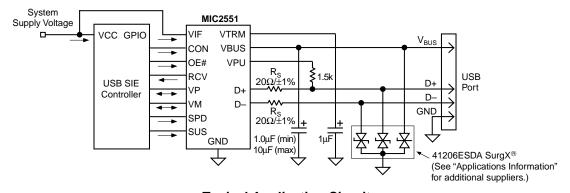

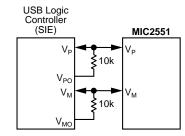

# **Typical Application**

**Typical Application Circuit**

MicroLeadFrame and MLF are trademarks of Amkor Technology. SurgX is a registered trademark of Cooper Electronics Technologies.

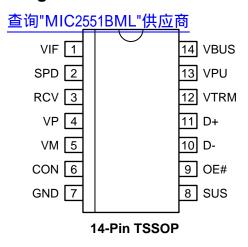

# **Pin Configuration**

# **Pin Description**

| Pin Number<br>MIC2551BTS | Pin Number<br>MIC2551BML | Pin Name | I/O                                                                   | Pin Function                                                                                                                                          |

|--------------------------|--------------------------|----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | 15                       | VIF      | I                                                                     | System Interface Supply Voltage: Used to provide reference supply voltage for system I/O interface signaling.                                         |

| 2                        | 1                        | SPD      | I                                                                     | Edge Rate Control: A logic HIGH operates at edge rates for "full speed" operation. A logic LOW operates edge rates for "low speed" operation.         |

| 3                        | 2                        | RCV*     | 0                                                                     | Receive Data: Output for USB differential data.                                                                                                       |

| 4                        | 3                        | VP*      | I/O                                                                   | If OE# = 1, VP = Receiver output (+) If OE# = 0, VP = Driver input (+)                                                                                |

| 5                        | 4                        | VM*      | I/O                                                                   | If OE# = 1 VM, = Receiver output (-) If OE# = 0, VM = Driver input (-)                                                                                |

| 6                        | 5                        | CON      | I                                                                     | CONNECT (Input): Controls state of VPU. Refer to VPU pin description for detail.                                                                      |

| 7                        | 6                        | GND      | Ground Reference.                                                     |                                                                                                                                                       |

| 8                        | 7                        | SUS      | I Suspend: Active-High. Turns off internal circuits to reduc current. |                                                                                                                                                       |

| 9                        | 9                        | OE#*     | I                                                                     | Output Enable: Active-Low. Enables the transceiver to transmit data onto the bus. When not active, the transceiver is in the receive mode.            |

| 10/11                    | 10/11                    | D-, D+*  | I/O                                                                   | Differential data lines conforming to the USB standard.                                                                                               |

| 12                       | 12                       | VTRM     | 0                                                                     | 3.3V Reference Supply Output: Requires a minimum 0.1µF decoupling capacitor for stability, 1µF recommended.4                                          |

| 13                       | 13                       | VPU      | 0                                                                     | Pull-up Supply Voltage Output: Used to connect $1.5k\Omega$ pull-up speed detect resistor. If CON = 1, VPU is high impedance. If CON = 0, VPU = 3.3V. |

| 14                       | 14                       | VBUS     | I                                                                     | USB Bus Supply Voltage: Used to power USB transceiver and internal circuitry.                                                                         |

|                          | 8,16                     | NC       |                                                                       | No connect.                                                                                                                                           |

|                          |                          |          |                                                                       |                                                                                                                                                       |

<sup>\*</sup> See Table 1 for description of logic states.

| SUS     | OE# | D+, D-    | RCV    | VP/VM      | Function                                            |

|---------|-----|-----------|--------|------------|-----------------------------------------------------|

| 查询"MIC2 |     | Driving   | Active | Active     | Normal transmit mode                                |

| 0       | 1   | Receiving | Active | Active     | Normal receive mode                                 |

| 1       | 0   | Hi-Z      | 0      | Not active | Low power state                                     |

| 1       | 1   | Hi-Z      | 0      | Active     | Receiving during suspend (low power state) (Note 1) |

Note 1. During suspend VP and VM are active in order to detect out of band signaling conditions.

**Table 1. Function Selection**

| OE# = 0: |     |        |        |     |           |

|----------|-----|--------|--------|-----|-----------|

| Inp      | out |        | Output |     |           |

| VP       | VM  | D+     | D-     | RCV | Result    |

| 0        | 0   | 0      | 0      | Х   | SE0       |

| 0        | 1   | 0      | 1      | 0   | Logic 0   |

| 1        | 0   | 1      | 0      | 1   | Logic 1   |

| 1        | 1   | 1      | 1      | Х   | Undefined |

| OE# = 1: |     |        |        |     |           |

| Int      | out | Output |        |     | Desuit    |

| D+       | D-  | VP     | VM     | RCV | Result    |

| 0        | 0   | 0      | 0      | Х   | SE0       |

| 0        | 1   | 0      | 1      | 0   | Logic 0   |

| 1        | 0   | 1      | 0      | 1   | Logic 1   |

| 1        | 1   | 1      | 1      | Х   | Undefined |

X - Undefined

**Table 2. Truth Table During Normal Mode**

# **Absolute Maximum Ratings (Note 1)**

| Supply Yeltage (YBOS) 18MI "供应商.                      | 6.5V            |

|-------------------------------------------------------|-----------------|

| Supply <b>宣問外 We2s</b> 51BML"供应商·<br>All Other Inputs | 0.5V to 5.5V    |

| Ambient Storage Temperature                           | –65°C to +150°C |

| Output Current (D+, D-)                               | ± 50mA          |

| Output Current (all others)                           | ±15mA           |

| Input Current                                         | ±50mA           |

| ESD, Note 3                                           |                 |

| V <sub>BUS</sub> , D+, D                              | ±11KV           |

| All other pins                                        | ±2KV            |

# **Operating Ratings (Note 2)**

| Ambient Operating Temperature40°C to + | -85°( |

|----------------------------------------|-------|

| Package Thermal Resistance             |       |

| TSSOP ( $\theta_{JA}$ )100             |       |

| MLF $(\theta_{JA})$                    | °C/V  |

# DC Electrical Characteristics (System and USB Interface) (Note 7)

$V_{IF} = 3.6V$ ,  $V_{BUS} = 5V$  unless otherwise noted;  $T_A = 25^{\circ}C$ . **Bold** indicates specifications over temperature,  $-40^{\circ}C$  to  $85^{\circ}C$ .

| Symbol                             | Parameter                         | Conditions                                                                                                              | Min                  | Тур | Max                  | Units |

|------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|-----|----------------------|-------|

| V <sub>BUS</sub>                   | USB Supply Voltage                |                                                                                                                         | 4.0                  |     | 5.25                 | V     |

| V <sub>IF</sub>                    | System I/F Supply Voltage         |                                                                                                                         | 1.6                  |     | 3.6                  | V     |

| $V_{IL}$                           | LOW-Level Input Voltage, Note 4   |                                                                                                                         | V <sub>IF</sub> -0.3 |     | 0.15V <sub>IF</sub>  | V     |

| $\overline{V_{IH}}$                | HIGH-Level Input Voltage, Note 4  |                                                                                                                         | 0.85V <sub>IF</sub>  |     | V <sub>IF</sub> +0.3 | V     |

| $V_{OH}$                           | HIGH-Level Output Voltage, Note 4 | I <sub>OH</sub> = 20μA                                                                                                  | 0.9V <sub>IF</sub>   |     |                      | V     |

| $V_{OL}$                           | LOW-Level Output Voltage, Note 4  | I <sub>OL</sub> = 20μA                                                                                                  |                      |     | 0.1                  | V     |

| I <sub>IL</sub>                    | Input Leakage Current, Note 4     |                                                                                                                         | -5                   |     | 5                    | μΑ    |

| I <sub>IF</sub>                    | VIF Supply Current                | D+, D- are idle, OE# = SUS = 0                                                                                          |                      |     | 5                    | μΑ    |

|                                    |                                   | D+, D- are idle, OE# = 0, SUS = 1                                                                                       |                      |     | 5                    | μΑ    |

|                                    |                                   | D+, D- active, C <sub>LOAD</sub> = 50pF,<br>SPD = 1, f = 6MHz, <b>Note 5</b>                                            |                      | 450 | 650                  | μΑ    |

|                                    |                                   | D+, D- active, C <sub>LOAD</sub> = 600pF<br>SPD = 0, f = 750kHz, <b>Note 5</b>                                          |                      | 50  | 75                   | μА    |

| I <sub>BUS</sub>                   | VBUS Supply Current               | V <sub>BUS</sub> = 5.25V, D+, D– are idle<br>Suspend Mode (SUS = 1)                                                     |                      | 65  | 100                  | μΑ    |

|                                    |                                   | V <sub>BUS</sub> = 5.25V, D+, D– are idle, SPD = 1<br>SUS = OE# = 0                                                     |                      | 3.3 | 5                    | mA    |

|                                    |                                   | V <sub>BUS</sub> = 5.25V, D+, D– are idle<br>SUS = OE# = SPD = 0                                                        |                      | 500 | 700                  | μΑ    |

|                                    |                                   | V <sub>BUS</sub> = 5.25V, D+, D– are idle, OE# = 1<br>SUS = SPD = 0                                                     |                      | 250 | 350                  | μΑ    |

|                                    |                                   | V <sub>BUS</sub> = 5.25V, D+, D– active,<br>C <sub>LOAD</sub> = 50pF, SPD = 1<br>SUS = OE# = 0, f = 6MHz, <b>Note 5</b> |                      | 7.3 | 10                   | mA    |

|                                    |                                   | V <sub>BUS</sub> = 5.25V, D+, D– active, C <sub>LOAD</sub> = 600pF<br>SPD = SUS = OE# = 0, f = 750kHz, <b>Note 5</b>    |                      | 3.6 | 5                    | mA    |

| I <sub>VPULEAK</sub>               | VPU Leakage Current               | CON = 1, V <sub>PU</sub> = 0V                                                                                           | -5                   |     | 5                    | μΑ    |

| I <sub>VIFLEAK</sub>               | VIF Leakage Current               | V <sub>IF</sub> = 3.6V, V <sub>BUS</sub> = 0V                                                                           | -5                   |     | 5                    | μΑ    |

| $\overline{V_{PU}}$                | Pull-Up Output Voltage            | I <sub>TERM</sub> = 200μA, V <sub>BUS</sub> = 4.0 to 5.25V                                                              | 3.0                  | 3.3 | 3.6                  | V     |

| R <sub>SW</sub>                    | Internal Pull-Up Termination      | I <sub>TERM</sub> = 10mA, V <sub>BUS</sub> = 4.0 to 5.25V                                                               |                      | 10  |                      | Ω     |

| ESD Protecti                       | on                                |                                                                                                                         | •                    |     | •                    |       |

| IEC-1000-4-2                       | Air Discharge                     | 10 pulses                                                                                                               |                      | ±8  |                      | kV    |

| (D+, D–,<br>V <sub>BUS</sub> only) | Contact Discharge                 | 10 pulses                                                                                                               |                      | ±9  |                      | kV    |

| DC                         | Electrical | Characteristics  | (Transceiver)       | (Note 7)                |

|----------------------------|------------|------------------|---------------------|-------------------------|

| $\boldsymbol{\mathcal{L}}$ |            | Onal actoristics | ( I I al ISCCIVCI ) | , (1401 <del>6</del> 7) |

| Symboh "M           | C25518191C"供应商                                              | Conditions                                                | Min                                   | Тур | Max    | Units    |

|---------------------|-------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------|-----|--------|----------|

| Leakage Cu          | rrent                                                       |                                                           | •                                     | •   | •      |          |

| I <sub>LO</sub>     | Hi-Z State Data Line Leakage<br>(Suspend Mode)              | 0V < V <sub>IN</sub> < 3.3V, SUS = 1                      | -10                                   |     | 10     | μА       |

| Input Levels        |                                                             |                                                           |                                       |     |        |          |

| $\overline{V_{DI}}$ | Differential Input Sensitivity                              | (D+) - (D-)                                               | 0.2                                   |     |        | V        |

| $V_{CM}$            | Differential Common Mode Range                              | Includes V <sub>DI</sub> range                            | 0.8                                   |     | 2.5    | V        |

| V <sub>SE</sub>     | Single Ended Receiver Threshold                             |                                                           | 0.8                                   |     | 2.0    | V        |

|                     | Receiver Hysteresis                                         |                                                           |                                       | 200 |        | mV       |

| Output Leve         | els                                                         |                                                           | •                                     |     |        |          |

| $\overline{V_{OL}}$ | Static Output Low                                           | $R_{L} = 1.5 k\Omega$ to 3.6V                             |                                       |     | 0.3    | V        |

| V <sub>OH</sub>     | Static Output High                                          | $R_L = 15k\Omega$ to GND                                  | 2.8                                   |     | 3.6    | V        |

| Capacitance         | •                                                           |                                                           | <u>'</u>                              |     | 1      |          |

| C <sub>IN</sub>     | Transceiver Capacitance                                     | Pin to GND                                                |                                       | 10  |        | pF       |

| Z <sub>DRV</sub>    | Driver Output Resistance                                    | Steady state drive                                        | 8                                     | 16  | 24     | Ω        |

|                     | trical Characteristics (Notes                               | s 6. 7)                                                   | · · · · · · · · · · · · · · · · · · · |     | 1      |          |

|                     | acteristics (Low Speed)                                     | ,                                                         |                                       |     |        |          |

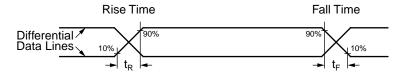

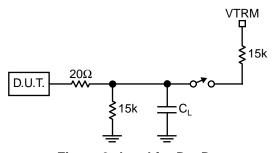

| T <sub>R</sub>      | Transition Rise Time                                        | C <sub>L</sub> = 50pF, Figure 2<br>C <sub>1</sub> = 600pF | 75                                    |     | 300    | ns       |

| T <sub>F</sub>      | Transition Fall Time                                        | C <sub>L</sub> = 50pF, Figure 2<br>C <sub>1</sub> = 600pF | 75                                    |     | 300    | ns       |

| $T_R, T_F$          | Rise/Fall Time Matching                                     | (T <sub>R</sub> , T <sub>F</sub> )                        | 80                                    |     | 125    | %        |

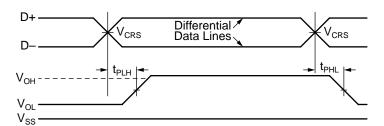

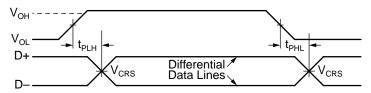

| V <sub>CRS</sub>    | Output Signal Crossover Voltage                             | X I                                                       | 1.3                                   |     | 2.0    | V        |

|                     | acteristics (Full Speed)                                    |                                                           | <u> </u>                              |     | ı      |          |

| $T_R$               | Transition Rise Time                                        | C <sub>I</sub> = 50pF, Figure 2                           | 4                                     |     | 20     | ns       |

| T <sub>F</sub>      | Transition Fall Time                                        | C <sub>L</sub> = 50pF, Figure 2                           | 4                                     |     | 20     | ns       |

| $T_R, T_F$          | Rise/Fall Time Matching                                     | (T <sub>R</sub> , T <sub>F</sub> )                        | 90                                    |     | 111.11 | %        |

| V <sub>CRS</sub>    | Output Signal Crossover Voltage                             | X I                                                       | 1.3                                   |     | 2.0    | V        |

| Transceiver         |                                                             |                                                           | I                                     |     | 1      | <u> </u> |

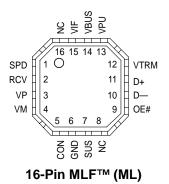

| t <sub>PVZ</sub>    | OE# to RCVR Tri-State Delay                                 | Figure 1                                                  |                                       |     | 15     | ns       |

| t <sub>PZD</sub>    | Receiver Tri-State to Transmit Delay                        | Figure 1                                                  | 15                                    |     |        | ns       |

| t <sub>PDZ</sub>    | OE# to DRVR Tri-State Delay                                 | Figure 1                                                  |                                       |     | 15     | ns       |

| t <sub>PZV</sub>    | Driver Tri-State to Receive Delay                           | Figure 1                                                  | 15                                    |     |        | ns       |

| t <sub>PLH</sub>    | VP, VM to D+, D– Propagation Delay                          | Figure 4                                                  |                                       |     | 15     | ns       |

| t <sub>PLH</sub>    | D+, D- to RCV Propagation Delay                             | Figure 3                                                  |                                       |     | 15     | ns       |

| t <sub>PLH</sub>    | D+, D– to V <sub>P</sub> , V <sub>M</sub> Propagation Delay | Figure 3                                                  |                                       |     | 8      | ns       |

- Note 1. Exceeding the absolute maximum rating may damage the device.

- **Note 2.** The device is not guaranteed to function outside its operating rating.

- Note 3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

- Note 4. Specification applies to the following pins: SUS, SPD, RCV, CON, RCV, VP, VM, OE#.

- Note 5. Characterized specification(s), but not production tested.

- Note 6. All AC parameters guaranteed by design but not production tested.

- Note 7. Specification for packaged product only.

# **Timing Diagrams**

Figure 1. Enable and Disable Times

Figure 2. Rise and Fall Times

Figure 3. Receiver Propagation Delay

Figure 4. Driver Propagation Delay

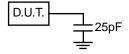

### **Test Circuits**

Figure 5. Load for  $V_P$ ,  $V_M$ , RCV

Figure 6. Load for D+, D-

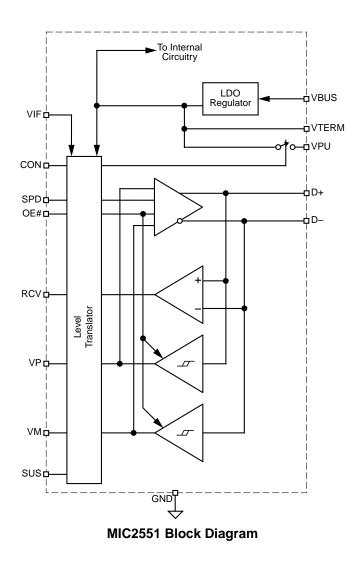

### **Functional Diagram**

查询"MIC2551BML"供应商

# **Functional Description**

The MIC2551 is designed to provide USB connectivity in mobile systems where available system supply voltages are not able to satisfy USB requirements. The MIC2551 can operate down to supply voltages of 1.6V and still meet USB physical layer specifications. As shown in the circuit above, the MIC2551 takes advantage of the USB supply voltage,  $V_{BUS},$  to operate the transceiver. The system voltage,  $V_{IF},$  is used to set the reference voltage used by the digital I/O lines interfacing to the system controller. Internal circuitry provides translation between the USB and system voltage domains.  $V_{IF}$  will typically be the main supply voltage rail for the controller.

In addition, a 3.3V, 10% termination supply voltage,  $V_{PU}$ , is provided to support speed selection.  $V_{PU}$  can be disabled or enabled under software control via the CON input. This allows for software-controlled connect or disconnect states. A 1.5k resistor is required to be connected between this pin and the D+ or D– lines to respectively specify high speed or low speed operation.

The use of ESD transient protection devices is not required for operation, but is recommended. The MIC2551 is ESD rated for 11kV at the VBUS and D+, D– pins and 2kV for all other pins.

### **Application Information**

# Power Supply Gention 供应商

The MIC2551 can be set up for different power supply configurations which modify the behavior of the device. Both  $V_{BUS}$  and  $V_{IF}$  have special thresholds that detect when they are either removed or grounded. Table 3 depicts the behavior under the different power supply configuration scenarios that are explained below.

#### Normal Mode

$V_{BUS}$  is connected to the 5.0V USB bus voltage and  $V_{IF}$  is connected to a supply voltage in the range of 1.6V to 3.6V. In this case  $V_{TRM}$  supplies a 3.3V voltage for powering the speed select resistor via  $V_{PU}$  depending on the state of the CON pin.

#### Disconnect Mode

$\rm V_{IF}$  is connected to a supply in a range of 1.6V to 3.6V and  $\rm V_{BUS}$  is open or grounded. If  $\rm V_{BUS}$  is opened while transmitting, the data lines (D+, D–) have sharing capability and may be driven with external devices up to approximately 3.6V if, and only if, SUSPEND is enabled (SUS = 1). With  $\rm V_{BUS}$  ground, D+, D– sharing mode is not permitted.

#### Disable Mode

$V_{BUS}$  is connected to the 5.0V USB bus voltage and  $V_{IF}$  is open. All logic controlled inputs become high impedances, thus minimal current will be supplied by  $V_{IF}$  if the input pins are pulled up to an external source.

# **Alternate Power Supply Configuration Options**

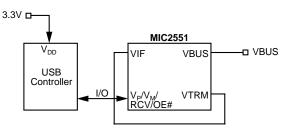

#### I/O Interface Using 3.3V

In systems where the I/O interface utilizes a 3.3V USB controller, an alternate solution is shown in Figure 7. No extra components are required; however, the load on  $V_{TRM}$  must not exceed 10mA.

Figure 7. I/O Interface Uses 3.3V

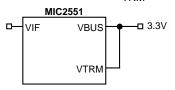

#### Bypass Input

$V_{BUS}$  and  $V_{TRM}$  are tied together to a supply voltage in the range of 3.0V to 3.6V. The internal regulator is bypassed and the internal circuitry is run from the  $V_{TRM}$  input. See Figure 8.

Figure 8. Powering Chip from Internal 3.3V Source

### Signal Amplitude Respective to VIF

When operating the MIC2551, it is necessary to provide input signals which do not exceed  $V_{\rm IF}$  + 0.3V.

#### **External ESD Protection**

The use of ESD transient protection devices is not required for operation, but is recommended. We recommend the following devices or the equivalent:

Cooper Electronic Technologies (www.cooperet.com)

41206ESDA SurgX<sup>®</sup> 0805ESDA SurgX<sup>®</sup>

Littelfuse (www.littelfuse.com)

V0402MHS05 SP0503BAHT

#### Non-Multiplexed Bus

In order to save pin count for the USB logic controller interface, the MIC2551 was designed with  $V_{\rm P}$  and  $V_{\rm M}$  as bidirectional pins. To interface the MIC2551 with a non-multiplexed data bus, resistors can be used for low cost isolation as shown in Figure 9.

Figure 9. MIC2551 Interface to Non-Multiplexed Data Bus

| Configuration Mode            | VBUS/VTRM | VIF       | Notes                                                                                                                                                                               |

|-------------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal                        | Connected | Connected | Normal supply configuration and operation.                                                                                                                                          |

| Disconnect<br>(D+/D- sharing) | Open      | Connected | VP/VM are HIGH outputs, RCV is LOW. With OE# = 0 and SUS = 1, data lines may be driven with external devices up to 3.6V. With D+, D– floating, I <sub>IF</sub> draws less than 1μA. |

| Disconnect                    | Ground    | Connected | VP/VM are HIGH outputs, RCV is LOW.<br>With D+, D– floating, I <sub>IF</sub> draws less than 1μA.                                                                                   |

| Disable Mode                  | Connected | Open      | Logic controlled inputs pins are Hi-Z.                                                                                                                                              |

| Prohibited                    | Connected | Ground    | Prohibited condition.                                                                                                                                                               |

Table 3. Power Supply Configuration

## **PCB Layout Recommendations**

Although the USB standard and applications are not based in an impedance controlled environment, a properly designed PCB layout is recommended for optimal transceiver performance. The suggested PCB layout hints are as follows:

- Match signal line traces (VP/VM, D+, D-) to 40ps, approximately <sup>1</sup>/<sub>3</sub> inch if possible. FR-4 PCB material propagation is about 150ps/inch, so to minimize skew try to keep VP/VM, D+/Dtraces as short as possible.

- For every signal line trace width (w), separate the signal lines by 1.5–2 widths. Place all other traces at >2 widths from all signal line traces.

- Maintain the same number of vias on each differential trace, keeping traces approximately at same separation distance along the line.

- Control signal line impedances to ±10%.

- Keep R<sub>S</sub> as close to the IC as possible, with equal distance between R<sub>S</sub> and the IC for both D+ and D-.

### **Package Information**

16-Pin MLF™ (ML)

### MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel, Inc.