# **SCAN12100**

# 1228.8 and 614.4 Mbps CPRI SerDes with Auto RE Sync and Precision Delay Calibration Measurement

# **General Description**

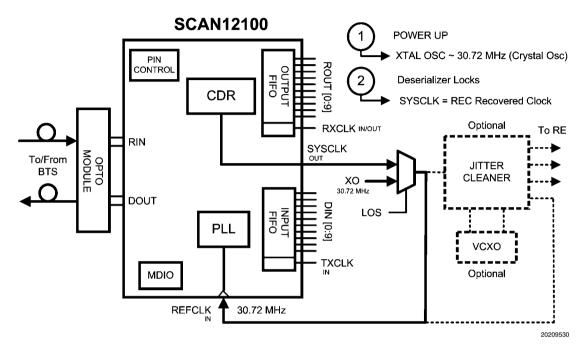

The SCAN12100 is a 1228.8 and 614.4 Mbps serializer/deseralizer (SerDes) for high-speed bidirectional serial data transmission over FR-4 printed circuit board backplanes, balanced cables, and optical fiber. The SCAN12100 integrates precision delay calibration measurement (DCM) circuitry that measures link delay components to better than  $\pm$  800 ps accuracy.

The SCAN12100 features independent transmit and receive PLLs, on-chip oscillator, and intelligent clock management circuitry to automatically perform remote radio head synchronization and reduce the cost and complexity of external clock networks.

The SCAN12100 is programmable though an MDIO interface as well as through pins, featuring configurable transmitter deemphasis, receiver equalization, speed rate selection, internal pattern generation/verification, and loop back modes. In addition to at-speed BIST, the SCAN12100 includes IEEE 1149.1 and 1149.6 testability.

#### **Features**

- Exceeds LV and HV CPRI voltage and jitter requirements

- 1228.8, and 614.4 Mbps operation

- Pin and package compatibility with the SCAN25100

- Integrated delay calibration measurement (DCM) directly measures T14 and Toffset delays to ≤ ± 800 ps

- DCM also measures chip and other delays to ≤ ± 1200 ps accuracy

- Deterministic chip latency

- Independent transmit and receive PLLs for seamless RE synchronization

- Low noise recovered clock output

- Requires no jitter cleaning in single-hop applications

- >8 kV ESD on the CML IO, >7 kV on all other pins, >2 kV CDM

- Hot plug protection

- LOS, LOF, 8b/10b line code violation, comma, and receiver PLL lock reporting

- Programmable hyperframe length and start of hyperframe character

- Programmable transmit de-emphasis and receive equalization with on-chip termination

- Advanced testability features

- IEEE 1149.1 and 1149.6

- At-speed BIST pattern generator/verifier

- Multiple loopback modes

- 1.8V or 3.3V compatible parallel bus interface

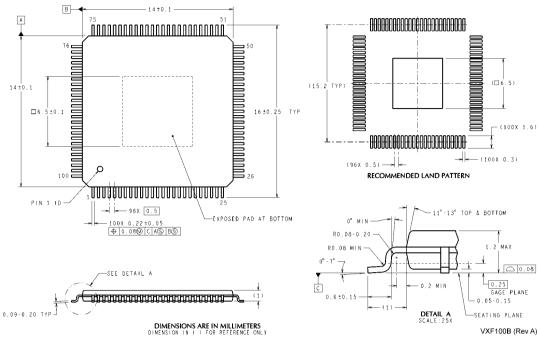

- 100-pin TQFP package with exposed dap

- Industrial –40 to +85° C temperature range

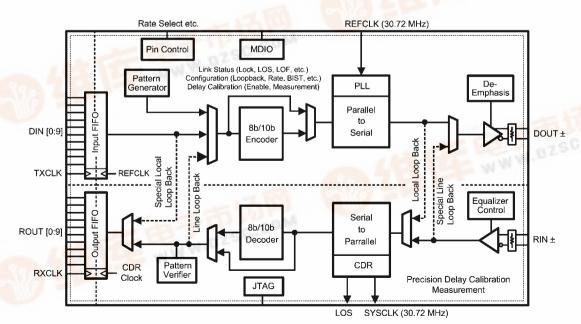

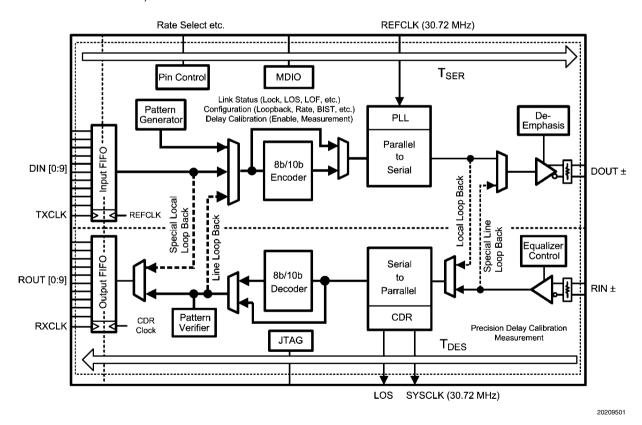

# **Block Diagram**

20209542

df.dzsc.com

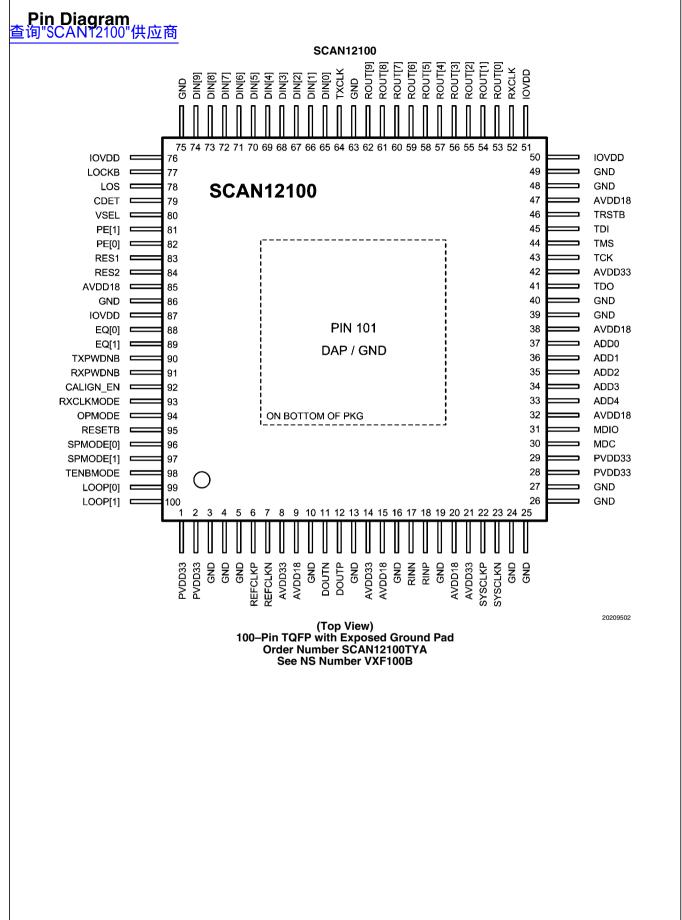

| Pin #    | Pin Name     | I/O, Type          | Description                                                                              |

|----------|--------------|--------------------|------------------------------------------------------------------------------------------|

|          | ED DIFFERENT |                    | Безеприон                                                                                |

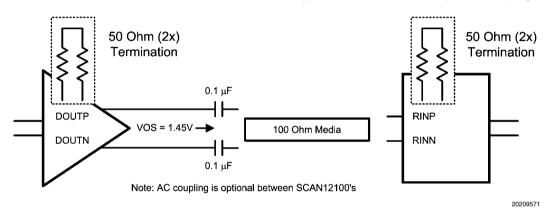

|          | DOUTP        | O, CML             | Investing and non-investing high annual CML differential outputs of the parializer. On   |

| 12       | DOUTN        | O, CIVIL           | Inverting and non-inverting high speed CML differential outputs of the serializer. Or    |

| 11       | +            |                    | chip termination resistors connect from DO+ and DO- to an internal reference             |

| 18       | RINP         | I, CML             | Inverting and non-inverting high speed differential inputs of the deseralizer. On-chip   |

| 17       | RINN         |                    | termination resistors connect from RI+ and RI- to an internal reference. On-chip         |

|          |              |                    | termination resistors are configured for AC-coupled applications.                        |

| PARALLE  | L DATA BUS   |                    |                                                                                          |

| 65       | DIN [0]      | I, LVTTL or 1.8V   | Transmit data word.                                                                      |

| 66       | DIN [1]      | LVCMOS Internal    |                                                                                          |

| 67       | DIN [2]      | pull down          | In 10-bit mode, the 10-bit code-group at DIN [0-9] is serialized with the internal 8b    |

| 68       | DIN [3]      |                    | 10b encoder disabled. Bit 9 is the msb.                                                  |

| 69       | DIN [4]      |                    |                                                                                          |

| 70       | DIN [5]      |                    | In 8-bit mode, DIN [0-7] is first converted into 10-bit code-group by the internal 8b/10 |

| 71       | DIN [6]      |                    | encoder before it is serialized. Bit 7 is the msb. DIN [8] is used as K-code select pi   |

| 72       | DIN [7]      |                    | and DIN[9] should be tied Low. When DIN [8] is low, DIN [0-7] is mapped to the           |

| 73       | DIN [8]      |                    | corresponding 10-bit D-group. When DIN [8] is high, DIN [0-7] is mapped to the           |

| 74       | DIN [9]      |                    | corresponding 10-bit K-group.                                                            |

| , ,      | 5(0)         |                    | The 8B/10B specification is defined in IEEE 802.3-2000 section 36.2.2                    |

|          |              |                    |                                                                                          |

| 53       | ROUT [0]     | O, LVTTL or 1.8V   | Deserialized receive data word.                                                          |

| 54       | ROUT [1]     | LVCMOS Internal    |                                                                                          |

| 55       | ROUT [2]     | pull down          | In 10-bit mode, ROUT [0-9] is the deserialized received data word in 10-bit code grou    |

| 56       | ROUT [3]     |                    | Bit 9 is the msb.                                                                        |

| 57       | ROUT [4]     |                    |                                                                                          |

| 58       | ROUT [5]     |                    | In 8-bit mode, ROUT [0-7] is the deserialized received data byte. Bit 7 is the msb.      |

| 59       | ROUT [6]     |                    | ROUT [8] is the K-group indicator. A low at ROUT [8] indicates ROUT [0-7] belongs        |

| 60       | ROUT [7]     |                    | to the D-group, while a high indicates it belongs to the K-group. ROUT [9] is the line   |

| 61       | ROUT [8]     |                    | code violation (LCV) indicator. ROUT [9] is high for one ROUT cycle when a line cod      |

| 62       | ROUT [9]     |                    | violation occurs.                                                                        |

|          |              |                    | The 8B/10B specification is defined in IEEE 802.3-2000 section 36.2.2                    |

| CLOCK S  | IGNALS       |                    | •                                                                                        |

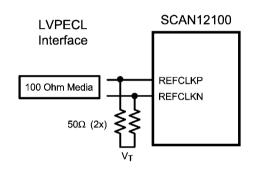

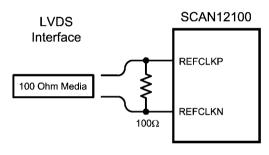

| 6        | REFCLKP      | I, LVDS or         | Inverting and non-inverting differential serializer reference clock. A low jitter clock  |

| 7        | REFCLKN      | LVPECL             | source should be connected to REFCLKP & REFCLKN.                                         |

|          |              |                    |                                                                                          |

| 64       | TXCLK        | I, LVTTL or 1.8V   | Transmit clock. TXCLK must be synchronous to REFCLK to avoid FIFO under/                 |

|          |              |                    | overflow though it may differ in phase.                                                  |

|          |              | pull down          |                                                                                          |

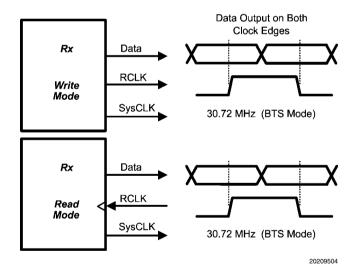

| 52       | RXCLK        | I/O, LVTTL or 1.8V | Write mode: RXCLK is recovered clock output pin.                                         |

|          |              | LVCMOS             |                                                                                          |

|          |              |                    | Read mode: RXCLK is an input pin. ROUT [9:0] are latched out on RXCLK rising an          |

|          |              |                    | falling edges. RXCLK must be synchronous to the incoming serial data to avoid FIF        |

|          |              |                    | over/underflow, though it may differ in phase. See RXCLKMODE pin description fo          |

|          |              |                    | more details.                                                                            |

| 22       | SYSCLKP      | O, LVDS            | 30.72 MHz output clock. (OPMODE must be low.)                                            |

| 23       | SYSCLKN      | 0,2150             | out I mine output clock. (Of mode much so form)                                          |

| LINE STA |              |                    |                                                                                          |

|          | 1            | 0.1777             | D : ODDII (: 1/100)   1 (01);   1 1)                                                     |

| 78       | LOS          | O, LVTTL or 1.8V   | Receiver CPRI loss of signal (LOS) status (8-bit mode only).                             |

|          |              | LVCMOS             |                                                                                          |

|          |              |                    | 0 = signal detected (per CPRI standard)                                                  |

|          |              |                    | 1 = signal lost (per CPRI standard)                                                      |

|          |              |                    |                                                                                          |

|          |              |                    | See "LOS Detection" under "Functional Description" for more details.                     |

| 77       | LOCKB        | O, LVTTL or 1.8V   | Receiver PLL lock status                                                                 |

|          |              | LVCMOS             | 0 = Receiver PLL locked                                                                  |

|          |              |                    | 1 = Receiver PLL not locked                                                              |

|          |              |                    |                                                                                          |

3

| Pin #   | Pin Name        | I/O, Type                           |                                                                                                            |                                       | Description                                                                                |  |  |  |  |

|---------|-----------------|-------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| 查询%CA   | <b>M</b> 台00"供应 | <mark>位</mark> 算LVTTL or 1.8V       | Comma Detect.                                                                                              |                                       |                                                                                            |  |  |  |  |

|         |                 | LVCMOS                              | 0 = no comma yet detected in the incoming serial stream or receiver PLL not locked.                        |                                       |                                                                                            |  |  |  |  |

|         |                 |                                     | 1 = the receiver F                                                                                         | PLL is locked an                      | d a positive or negative comma bit sequence detected                                       |  |  |  |  |

|         |                 |                                     | in the incoming bit stream. The serial to parallel converter is aligned to the proper 10-                  |                                       |                                                                                            |  |  |  |  |

|         |                 |                                     | bit word boundary when comma alignment is enabled (CALIGN_EN = 1).                                         |                                       |                                                                                            |  |  |  |  |

| CONTROL | PINS            |                                     |                                                                                                            |                                       |                                                                                            |  |  |  |  |

|         | PE [0]          | I, LVTTL or 1.8V                    | Transmitter de-emphasis configuration.                                                                     |                                       |                                                                                            |  |  |  |  |

| 81      | PE [1]          | LVCMOS Internal                     | <del> </del>                                                                                               | low enables M                         | DIO control, default is no de-emphasis.                                                    |  |  |  |  |

|         |                 | pull down                           | PE1                                                                                                        | PE0                                   |                                                                                            |  |  |  |  |

|         |                 |                                     | 0                                                                                                          | 0                                     | No de-emphasis                                                                             |  |  |  |  |

|         |                 |                                     | 0                                                                                                          | 1                                     | Low de-emphasis                                                                            |  |  |  |  |

|         |                 |                                     | 1                                                                                                          | 0                                     | Medium de-emphasis                                                                         |  |  |  |  |

|         |                 |                                     | 1                                                                                                          | 1                                     | Maximum de-emphasis                                                                        |  |  |  |  |

| 88      | EQ [0]          | I, LVTTL or 1.8V                    | Receive input ed                                                                                           |                                       |                                                                                            |  |  |  |  |

| 89      | EQ [1]          | LVCMOS Internal                     |                                                                                                            | low enables M                         | DIO control, default is no receive equalization.                                           |  |  |  |  |

|         |                 | pull down                           | EQ1                                                                                                        | EQ0                                   |                                                                                            |  |  |  |  |

|         |                 |                                     | 0                                                                                                          | 0                                     | No receive equalization                                                                    |  |  |  |  |

|         |                 |                                     | 0                                                                                                          | 1                                     | Low receive equalization                                                                   |  |  |  |  |

|         |                 |                                     | 1                                                                                                          | 0                                     | Medium receive equalization                                                                |  |  |  |  |

|         |                 |                                     | 1                                                                                                          | 1                                     | Maximum receive equalization                                                               |  |  |  |  |

| 90      | TXPWDNB         | I, LVTTL or 1.8V                    | Power down con                                                                                             | itrol signals.                        |                                                                                            |  |  |  |  |

| 91      | RXPWDNB         | LVCMOS Internal                     | TXPWDNB                                                                                                    |                                       |                                                                                            |  |  |  |  |

|         |                 | pull down                           | 0 = Transmitter is powered down and DOUT± pins are high impedance. 1 = Transmitter is powered up.  RXPWDNB |                                       |                                                                                            |  |  |  |  |

|         |                 |                                     |                                                                                                            |                                       | and ROUT [9:0] as well as LOS, LOCKB, CDET, impedance.                                     |  |  |  |  |

|         |                 |                                     | 1 = Receiver is p                                                                                          | owered up.                            |                                                                                            |  |  |  |  |

| 92      | CALIGN_EN       | I, LVTTL or 1.8V                    | Comma alignme                                                                                              |                                       |                                                                                            |  |  |  |  |

|         |                 | LVCMOS Internal                     | _                                                                                                          | -                                     | isabled. Receiver will not realign 10-bit data based on                                    |  |  |  |  |

|         |                 | pull down                           | _                                                                                                          |                                       | DET pin still flags comma detection.  nt circuitry enabled. Receiver aligns 10-bit data to |  |  |  |  |

|         |                 |                                     |                                                                                                            | _                                     | flags comma detect through CDET pin.                                                       |  |  |  |  |

| 93      | RXCLKMODE       | I, LVTTL or 1.8V                    | Receiver recove                                                                                            |                                       | <u> </u>                                                                                   |  |  |  |  |

|         | TO COLIMODE     | LVCMOS Internal                     |                                                                                                            |                                       | recovered clock output.                                                                    |  |  |  |  |

|         |                 | pull down                           | (RXCLK = outpu                                                                                             | · · · · · · · · · · · · · · · · · · · | ·                                                                                          |  |  |  |  |

|         |                 |                                     | 1 = Read mode.                                                                                             | RXCLK pin is F                        | ROUT [9:0] bus read input strobe.                                                          |  |  |  |  |

|         |                 |                                     | (RXCLK = input                                                                                             | ' '                                   |                                                                                            |  |  |  |  |

| 80      | VSEL            | I, LVTTL or 1.8V                    | 1                                                                                                          | •                                     | ata and control pins are 3.3V LVTTL or 1.8V LVCMOS.                                        |  |  |  |  |

|         |                 | LVCMOS Internal                     |                                                                                                            |                                       | ground and power IOVDD at 1.8 V.                                                           |  |  |  |  |

|         | ODMODE          | pull down                           |                                                                                                            |                                       | OVDD supply and power IOVDD at 3.3 V.                                                      |  |  |  |  |

| 94      | OPMODE          | I, LVTTL or 1.8V<br>LVCMOS Internal | Selects SerDes                                                                                             | mode.                                 |                                                                                            |  |  |  |  |

|         |                 | pull down                           | 0 = Base station                                                                                           | mode                                  |                                                                                            |  |  |  |  |

|         |                 | Pan 40411                           | 1 = Reserved for                                                                                           |                                       |                                                                                            |  |  |  |  |

| 95      | RESETB          | I, LVTTL or 1.8V                    | -                                                                                                          |                                       | PLLs and MDIO registers.                                                                   |  |  |  |  |

|         |                 | LVCMOS Internal                     |                                                                                                            |                                       | aa                                                                                         |  |  |  |  |

|         |                 | l                                   | 0 = Hardware SerDes reset                                                                                  |                                       |                                                                                            |  |  |  |  |

|         |                 | pull down                           | 0 = Hardware Se                                                                                            | erDes reset                           |                                                                                            |  |  |  |  |

| Pin #                     | Pin Name        | I/O, Type           |                                                                          |                     |                                                |  |  |  |

|---------------------------|-----------------|---------------------|--------------------------------------------------------------------------|---------------------|------------------------------------------------|--|--|--|

| 96 🇯                      | <b>銅版66AN12</b> |                     | Speed mode con                                                           | figuration. (OPMC   | DDE must be low)                               |  |  |  |

| 97                        | SPMODE [1]      | LVCMOS Internal     | Pulling both pins                                                        |                     |                                                |  |  |  |

|                           |                 | pull down           | SPMODE [1]                                                               | SPMODE [0]          |                                                |  |  |  |

|                           |                 | F                   | 0                                                                        | 0                   | Rate selected via MDIO                         |  |  |  |

|                           |                 |                     |                                                                          | <b>-</b>            |                                                |  |  |  |

|                           |                 |                     | 0                                                                        | 1                   | 614.4 Mbps rate mode                           |  |  |  |

|                           |                 |                     | 1                                                                        | 0                   | 1228.8 Mbps rate mode                          |  |  |  |

|                           |                 |                     | 1                                                                        | [1                  | Reserved                                       |  |  |  |

| 98                        | TENBMODE        | I, LVTTL or 1.8V    | Enable 10-bit mo                                                         |                     |                                                |  |  |  |

|                           |                 | LVCMOS, Internal    | -                                                                        |                     | ned in IEEE 802.3-2000 section 36.2.2          |  |  |  |

|                           |                 | pull down           | 0 = Selects 8-bit mode. Enables the internal 8b/10b encoder and decoder. |                     |                                                |  |  |  |

|                           |                 |                     | 1 = Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder.   |                     |                                                |  |  |  |

| 99                        | LOOP [0]        | I, LVTTL or 1.8V    | Loop back config                                                         |                     |                                                |  |  |  |

| 100                       | LOOP [1]        | LVCMOS, Internal    | Pulling both pins                                                        |                     |                                                |  |  |  |

|                           |                 | pull down           |                                                                          | cial line (remote)  | loop back mode, the output de-emphasis control |  |  |  |

|                           |                 |                     | is disabled.                                                             |                     |                                                |  |  |  |

|                           |                 |                     | LOOP [1]                                                                 | LOOP [0]            |                                                |  |  |  |

|                           |                 |                     | 0                                                                        | 0                   | Normal mode—no loop back                       |  |  |  |

|                           |                 |                     | 0                                                                        | 1                   | Line (remote) loop back mode                   |  |  |  |

|                           |                 |                     | 1                                                                        | 0                   | Local loop back mode                           |  |  |  |

|                           |                 |                     | 1                                                                        | 1                   | Special line (remote) loop back mode           |  |  |  |

| MDC/MDIO                  |                 |                     | <u>.</u>                                                                 | 1.                  | Toposia: iiiio (ioiiioto) toop baast meac      |  |  |  |

| 30                        | MDC             | 3.3V LVTTL          | MDC/MDIO confi                                                           | guration bus        |                                                |  |  |  |

| 31                        | MDIO            | Internal pull up on |                                                                          |                     | IDC/MDIO Clause 45. These pins are 3.3V LVTTL  |  |  |  |

| 37                        | ADD0            | ADDR pins           | compatible, not 1                                                        |                     |                                                |  |  |  |

| 36                        | ADD1            | ADDIT PINS          | Compatible, not i                                                        | .zv signai compa    | uibio.                                         |  |  |  |

| 35                        | ADD2            |                     |                                                                          |                     |                                                |  |  |  |

| 34                        | ADD3            |                     |                                                                          |                     |                                                |  |  |  |

| 33                        | ADD4            |                     |                                                                          |                     |                                                |  |  |  |

| IEEE 1149.                | 1 (JTAG)        |                     |                                                                          |                     |                                                |  |  |  |

| 45                        | TDI             | 3.3V LVTTL          | .ITAG test bus fo                                                        | r IFFF 1149 1 and   | d 1149.6 support.                              |  |  |  |

| 41                        | TDO             | Internal pull up on | 01710 1001 000 10                                                        | riele risori an     | а т 140.0 баррота                              |  |  |  |

| 44                        | TMS             | TDI, TMS, and       |                                                                          |                     |                                                |  |  |  |

| 43                        | TCK             | TRSTB               |                                                                          |                     |                                                |  |  |  |

| 46                        | TRSTB           |                     |                                                                          |                     |                                                |  |  |  |

| RESERVE                   | PINS            |                     | <u> </u>                                                                 |                     |                                                |  |  |  |

| 83                        | RES1            |                     | Reserved.                                                                |                     |                                                |  |  |  |

| 84                        | RES2            |                     | Tie with 5 KΩ res                                                        | sistor to ground.   |                                                |  |  |  |

| POWER                     |                 |                     | 1.0 0 1.02 100                                                           | to ground.          |                                                |  |  |  |

| 9, 15, 20,                | AVDD18          | I, Power            | 1.8V analog supp                                                         | alv.                |                                                |  |  |  |

| 9, 15, 20,<br>32, 38, 47, | וסוממאי         | i, Fower            | i.ov analog supp                                                         | лу.                 |                                                |  |  |  |

| 85                        |                 |                     |                                                                          |                     |                                                |  |  |  |

|                           | AVDDOO          | I Dawar             | 0.01/ 0.00/0.00                                                          | .l.,                |                                                |  |  |  |

| 8, 14, 21,<br>42          | AVDD33          | I, Power            | 3.3V analog supp                                                         | DIY.                |                                                |  |  |  |

|                           | DVDD00          | L Danier            | 0.01/ DL L                                                               | /                   | residents (100 m)/ modules moduly              |  |  |  |

| 1, 2, 28, 29              |                 | I, Power            |                                                                          |                     | noise to < 100 mV peak-to-peak).               |  |  |  |

| 50, 51, 76,               | טטעטון          | I, Power            |                                                                          |                     | control pin supply.                            |  |  |  |

| 87                        |                 |                     | See VSEL pin de                                                          | scription for addit | tional information.                            |  |  |  |

| GROUND                    | F2:.2           |                     | <u></u>                                                                  |                     |                                                |  |  |  |

|                           | GND             | I, Ground           | Device ground.                                                           |                     |                                                |  |  |  |

| 13, 16, 19,               |                 |                     |                                                                          |                     |                                                |  |  |  |

| 24, 25, 26,               |                 |                     |                                                                          |                     |                                                |  |  |  |

| 27, 39, 40,               |                 |                     |                                                                          |                     |                                                |  |  |  |

| 48, 49, 63,               |                 |                     |                                                                          |                     |                                                |  |  |  |

| 75, 86                    |                 |                     |                                                                          |                     |                                                |  |  |  |

|                           |                 |                     |                                                                          |                     |                                                |  |  |  |

| Pin #                     | Pin Name | I/O, Type | Description                                                                   |  |  |

|---------------------------|----------|-----------|-------------------------------------------------------------------------------|--|--|

| <b>全的UNG/bAH</b> 2100"供应商 |          |           |                                                                               |  |  |

| 101                       | GND      | I, Ground | Device ground. Pad must be soldered and contected to GND plane with a minimum |  |  |

|                           |          |           | of 8 thermal vias to achieve specified thermal performance.                   |  |  |

Note: I= input O = output Internal pull down = input pin is pulled low by an internal resistor Internal pull up = input pin is pulled high by an internal resistor

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (AV $_{\rm DD18}$ ) -0.3 V to +2.0 VSupply Voltage (PV $_{\rm DD}$ , IOV $_{\rm DD}$ ) -0.3 V to +3.6 VSupply Voltage (AV $_{\rm DD33}$ ) -0.3 V to +3.6 VLVCMOS Input Voltage  $-0.3 \text{V to } (\text{IOV}_{\rm DD} + \text{VCMOS Output Voltage})$

LVCMOS Output Voltage  $$-0.3$\rm V$  to (IOV  $_{\rm DD}$  +  $0.5\rm V)$

MDC/MDIO/ADD[0:4], VSEL Input Voltage

-0.3V to  $(AV_{DD33} + 0.5V)$

MDIO Output Voltage  $\begin{array}{c} -0.3 \text{V to (AV}_{\text{DD33}} + \\ 0.5 \text{V)} \end{array}$

CML Receiver Input Voltage  $$-0.3$\mbox{V to } (\mbox{AV}_{\mbox{\scriptsize DD}}\mbox{ +} \\ 0.3\mbox{V})$

CML Receiver Output Voltage -0.3V to (AV<sub>DD</sub> +

0.3V)

Junction Temperature +125°C

Storage Temperature -65°C to +150°C Lead Temperature

Soldering, 10–20 sec 235 °C

Lead-free +260°C flow is available

Maximum Package Power Dissipation at 25°C 100-pin TQFP with Exposed Pad 4.16 W

Note: This is the maximum TQFP-100 package power dissipation capability. For SCAN12100 power dissipation, see the information in the Electrical Characteristics section.

| Derating above 25°C                            | 41.6 mW/°C |

|------------------------------------------------|------------|

| Thermal Resistance , $\theta_{JA}$ (0 airflow) | 24.0°C/W   |

| ESD Rating<br>CML RIN/DOUT Pins                |            |

| HBM, 1.5 kΩ, 100 pF                            | >8 kV      |

| EIAJ, 0Ω, 200 pF                               | >250V      |

| CDM                                            | >2 kV      |

| All Other Pins                                 |            |

| HBM, 1.5 kΩ, 100 pF                            | >7 kV      |

| EIAJ, 0Ω, 200 pF                               | >250V      |

| CDM                                            | >2 kV      |

# Recommended Operating Conditions

|                                | Min   | Тур | Max   | Unit |

|--------------------------------|-------|-----|-------|------|

| Supply Voltage                 |       |     |       |      |

| AV <sub>DD18</sub>             | 1.7   | 1.8 | 1.9   | V    |

| $AV_{DD33}$ , $PV_{DD33}$      | 3.135 | 3.3 | 3.465 | V    |

| IOV <sub>DD</sub> (1.8V Mode)  | 1.7   | 1.8 | 1.9   | V    |

| IOV <sub>DD</sub> (3.3V Mode)  | 3.135 | 3.3 | 3.465 | V    |

| Temperature                    | -40   | 25  | 85    | °C   |

| Junction temperature           |       |     | 125   | °C   |

| Supply Noise<br>(Peak-to-Peak) |       |     | <100  | mV   |

## **Electrical Characteristics** Over recommended operating supply and temperature ranges unless other specified.

| Symbol          | Parameter                   | Condition                      | Min                 | Typ<br>(Note 2) | Max                 | Units |

|-----------------|-----------------------------|--------------------------------|---------------------|-----------------|---------------------|-------|

| LVCMOS D        | C SPECIFICATIONS (1.8V I/O) | •                              | •                   |                 |                     |       |

| V <sub>IH</sub> | High level input voltage    |                                | 0.65V <sub>DD</sub> |                 |                     | V     |

| V <sub>IL</sub> | Low level input voltage     |                                |                     |                 | 0.35V <sub>DD</sub> | V     |

| I <sub>IN</sub> | Input Current               | V <sub>IN</sub> = 0V or 1.9V   | -10                 |                 | +50                 | μA    |

| V <sub>OH</sub> | High level output voltage   | I <sub>OH</sub> = -2 mA        | 1.2                 |                 |                     | V     |

| V <sub>OL</sub> | Low level output voltage    | I <sub>OL</sub> = 2 mA         |                     |                 | 0.45                | V     |

| l <sub>oz</sub> | Power Down Output Current   | Power down                     | -20                 |                 | +20                 | μA    |

| C <sub>IO</sub> | Input/Output Capacitance    | Typical                        |                     | 2.8             |                     | pF    |

| LVCMOS D        | C SPECIFICATIONS (3.3V I/O) | •                              |                     |                 |                     |       |

| V <sub>IH</sub> | High level input voltage    |                                | 2                   |                 |                     | V     |

| $V_{IL}$        | Low level input voltage     |                                |                     |                 | 0.8                 | V     |

| I <sub>IN</sub> | Input Current               | V <sub>IN</sub> = 0V or 3.465V | -10                 |                 | +50                 | μA    |

| V <sub>OH</sub> | High level output voltage   | $I_{OH} = -2 \text{ mA}$       | 2.4                 |                 |                     | V     |

| V <sub>OL</sub> | Low level output voltage    | I <sub>OL</sub> = 2 mA         |                     |                 | 0.4                 | V     |

| l <sub>oz</sub> | Power Down Output Current   | Power down                     | -20                 |                 | +20                 | μA    |

| C <sub>IO</sub> | Input/Output Capacitance    | Typical                        |                     | 2.8             |                     | pF    |

| JTAG DC S       | PECIFICATIONS (3.3V I/O)    |                                |                     |                 |                     |       |

| V <sub>IH</sub> | High level input voltage    |                                | 2                   |                 |                     | V     |

| V <sub>IL</sub> | Low level input voltage     |                                |                     |                 | 0.8                 | V     |

| I <sub>IN</sub> | Input Current               | V <sub>IN</sub> = 0V or 3.465V | -35                 |                 | +50                 | μA    |

| V <sub>OH</sub> | High level output voltage   | I <sub>OH</sub> = -2 mA        | 2.4                 |                 |                     | V     |

| Symbol<br>A                  | N12100"供 <mark>Parameter</mark>   | Condition                                                                                  | Min   | Typ<br>(Note 2) | Max   | Units             |

|------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------|-------|-----------------|-------|-------------------|

| V <sub>OL</sub>              | Low level output voltage          | I <sub>OL</sub> = 2 mA                                                                     |       |                 | 0.4   | V                 |

| 210                          | Input/Output Capacitance          | Typical                                                                                    |       | 2.8             |       | pF                |

|                              | /ADD0-4 DC SPECIFICATIONS         |                                                                                            |       |                 |       | <u> </u>          |

| / <sub>IH</sub>              | High level input voltage          |                                                                                            | 2.0   |                 | 3.465 | V                 |

| / <sub>IL</sub>              | Low level input voltage           |                                                                                            | GND   |                 | 0.8   | V                 |

| IN                           | Input Current                     | V <sub>IN</sub> = 0 or 3.465V                                                              | -150  |                 | +150  | μA                |

| / <sub>OH</sub>              | High level output voltage         | $I_{OH} = -2 \text{ mA}$                                                                   | 2.4   |                 |       | v                 |

| <u>он</u><br>/ <sub>OL</sub> | Low level output voltage          | I <sub>OL</sub> = 2 mA                                                                     |       |                 | 0.4   | V                 |

| OZ                           | Power Down Output Current         | Power down                                                                                 | -100  |                 | +100  | μA                |

| 2 <sub>10</sub>              | Input/Output Capacitance          | Typical                                                                                    |       | 2.8             |       | pF                |

|                              | ONSUMPTION                        | Typical                                                                                    |       | 2.0             |       | P.                |

| P <sub>D</sub>               | Max total power consumption       | 614.4 Mbps                                                                                 |       |                 |       |                   |

| D                            | max total power concemption       | Parallel I/O at 1.9V                                                                       |       | 920             | 1040  | mW                |

|                              |                                   | Parallel I/O at 3.465V                                                                     |       | 1040            | 1150  | mW                |

|                              | PRWS pattern embedded in          | 1228.8 Mbps                                                                                |       | 1               |       | 1                 |

|                              | hyperframe                        | Parallel I/O at 1.9V                                                                       |       | 950             | 1100  | mW                |

|                              | Output loading:                   | Parallel I/O at 3.465V                                                                     |       | 1110            | 1250  | mW                |

|                              | CML: AC-coupled                   |                                                                                            |       |                 |       |                   |

|                              | CMOS: 50Ω transmission line       |                                                                                            |       |                 |       |                   |

|                              | ONSUMPTION (Powerdown)            |                                                                                            |       | 1               |       | 1                 |

| PDN                          | Powerdown Mode                    | Rx and Tx Powerdown                                                                        |       | 25              | 40    | mW                |

|                              | OWER CONSUMPTION (By Suppl        |                                                                                            |       |                 |       | 1                 |

| $P_{DS}$                     | PVDD33                            | 1228.8 Mbps operation                                                                      |       | 285             |       | mW                |

|                              | AVDD33                            | Parallel I/O at 3.3V PRWS pattern embedded in                                              |       | 160             |       | mW                |

|                              | IOVDD                             | hyperframe                                                                                 |       | 230             |       | mW                |

|                              | AVDD18                            | 1                                                                                          |       | 435             |       | mW                |

|                              | NDED REFCLK INPUT SPECIFICA       | TIONS                                                                                      |       | 1               |       | 1                 |

| IDSREFCLK                    | Differential input voltage        |                                                                                            | ± 100 |                 |       | mV <sub>P-I</sub> |

| / <sub>ICM</sub>             | Common mode voltage               |                                                                                            | 0.05V |                 | 2.4V  | V                 |

| REF                          | REFCLK frequency                  | OPMODE = 0 (BTS SerDes Mode)                                                               | 30    | 30.72           | 31.5  | MHz               |

| df <sub>REF</sub>            | REFCLK frequency variation        | Variation from nominal frequency                                                           | -100  |                 | +100  | ppm               |

| REF-DC                       | REFCLK duty cycle                 | Between 50% of the differential voltage across REFCLKP and REFCLKN                         | 45    |                 | 55    | %                 |

| REF-X                        | REFCLK transition time            | Transition time between 20% and 80% of the differential voltage across REFCLKP and REFCLKN |       | 300             |       | pS                |

| SYSCLK D                     | C OUTPUT SPECIFICATIONS           |                                                                                            |       |                 |       |                   |

| / <sub>OD</sub>              | Differential Output Voltage       | $R_L = 100\Omega$                                                                          | ± 250 | ± 330           | ± 450 | mV                |

| / <sub>os</sub>              | Offset Voltage                    |                                                                                            | 1.125 | 1.20            | 1.375 | V                 |

| os                           | Output Short Circuit Current      | Output pair shorted together and tied to GND                                               |       |                 | 35    | mA                |

| OZ                           | Power Down Output Current         | Power down                                                                                 | -30   |                 | +30   | μA                |

|                              | TER SERIAL TIMING SPECIFICAT      | IONS                                                                                       |       | •               |       | •                 |

| / <sub>OD</sub>              | Output differential voltage swing | PE[1]=0, PE[0]=0                                                                           | ± 550 | ± 700           | ± 800 | mVp-p             |

| - =                          |                                   | PE[1]=0, PE[0]=1                                                                           |       | ± 630           |       | mVp-p             |

|                              |                                   | PE[1]=1, PE[0]=0                                                                           |       | ± 500           |       | mVp-p             |

|                              |                                   | PE[1]=1, PE[0]=1                                                                           | ± 200 | ± 360           | ± 450 | mVp-p             |

|                              |                                   |                                                                                            |       |                 |       |                   |

| Symbo                       | 宣询"SCAN P21000年底                                      | Condition                                                        | Min   | Typ<br>(Note 2) | Max    | Units |

|-----------------------------|-------------------------------------------------------|------------------------------------------------------------------|-------|-----------------|--------|-------|

| ન <sub>૦</sub>              | Output Return Loss                                    | Frequency = 1.229 GHz                                            |       | -13.4           |        | dB    |

| R, t <sub>F</sub>           | Serial data output transition time (Notes 11, 15)     | Measured between 20% and 80%                                     | 80    | 100             | 130    | ps    |

| IT <sub>T-DJ</sub>          | Serial data output deterministic jitter (Notes 3, 11) | Output CJPAT with BER of 10 <sup>-12</sup> (Note 4)              |       |                 | 0.14   | Ulp-p |

| IT <sub>T-TJ</sub>          | Serial data output total jitter (Notes 3, 11)         | Output CJPAT pattern with BER of 10 <sup>-12</sup> (Note 4)      |       |                 | 0.279  | Ulp-p |

| AT-ACC-T                    | Transmit latency variation at start                   | 614.4 Mbps                                                       |       |                 | 36     | ns    |

|                             | up (Notes 11, 6, 8)                                   | 1.228 Gbps                                                       |       |                 | 18     |       |

| AT-T                        | Transmit latency (Note 8)                             | 614.4 Mbps                                                       |       | 310             |        | ns    |

|                             |                                                       | 1.228 Gbps                                                       |       | 155             |        |       |

| DO-LOCK                     | Maximum lock time                                     | K28.5 pattern at 1228.8 Mbps                                     |       | 110             | 130    | us    |

|                             | R SERIAL TIMING SPECIFICATIONS                        |                                                                  |       |                 |        |       |

| / <sub>ID</sub>             | Input voltage                                         | RINP - RINN                                                      | ± 100 |                 | ± 1100 | mVp-p |

| CMR                         | Receiver common mode voltage                          |                                                                  |       | 0.9             |        | V     |

| R <sub>R</sub>              | Differential Input Terminations                       |                                                                  | 80    | 100             | 120    | Ω     |

| RLR <sub>I</sub>            | Input Return Loss (Note 11)                           | Frequency = 1.229 GHz                                            |       | -20             | -15    | dB    |

| · ·                         | Receive latency (Note 9)                              | 614.4 Mbps                                                       |       | 280             |        | ns    |

| AT-R                        | (Note 5)                                              | 1.228 Gbps                                                       |       | 140             |        | ns    |

|                             | Receive latency variation at start up                 | ·                                                                |       | 140             | 36     | ns    |

| AT-R                        | (Notes 11, 6, 9)                                      | 1.228 Gbps                                                       |       |                 | 18     | ns    |

| IT <sub>R-TOL</sub>         | Total input jitter tolerance (Note 11)                | Input CJPAT with BER of 10-12                                    |       |                 | 0.66   | Ulp-p |

| R-LOCK                      | Receiver lock range                                   | (Note 4) Input data rate reference to local transmit data rate.  | -200  |                 | +200   | ppm   |

| R-LOCK                      | Maximum lock time                                     | K28.5 pattern at 1228.8 Mbps                                     |       |                 | 1      | ms    |

|                             | TTER INPUT TIMING SPECIFICATION                       |                                                                  |       |                 |        |       |

| S-T                         | Setup Time                                            | DIN [9:0] valid to TXCLK rising or falling edge                  | 0.5   |                 |        | ns    |

| H-T                         | Hold Time                                             | TXCLK rising or falling edge to DIN [9:0] valid                  | 0.5   |                 |        | ns    |

| DC                          | Duty cycle                                            | TXCLK duty cycle                                                 | 45    |                 | 55     | %     |

| TXCLK                       | TXCLK frequency                                       |                                                                  | 30    |                 | 62.5   | MHz   |

|                             | R OUTPUT TIMING SPECIFICATIONS                        | I                                                                |       |                 |        |       |

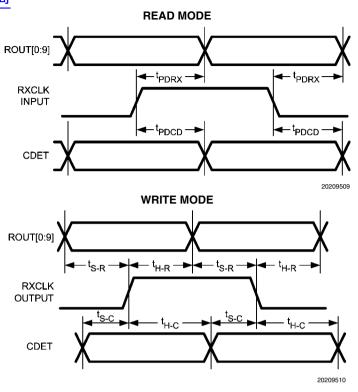

| PDRX                        | RXCLK Propagation Delay                               | RXCLK rising or falling edge to ROUT [9:0] valid                 | 2     | 4               | 6      | ns    |

| DC                          | Duty cycle                                            | RXCLK input duty cycle                                           | 45    |                 | 55     | %     |

| RXCLKR                      | RXCLK input frequency                                 | RXCLK input frequency                                            | 30    |                 | 62.5   | MHz   |

| RXCLKH<br>R, t <sub>F</sub> | Output data transition time                           | For ROUT [0-9], LOCK, etc. pins.<br>Measured between 20% and 80% |       | 0.35            | 02.0   | ns    |

| RECEIVER                    | <br>                                                  | levels 6 (Write Mode RXCLKMODE=0)                                |       |                 |        |       |

| S-R                         | Setup Time                                            | ROUT [9:0] valid to RXCLK rising or falling edge (Note 10)       | 2.2   |                 |        | ns    |

|                             |                                                       | RXCLK rising or falling edge to                                  | 2.4   |                 |        | ns    |

| H-R                         | Hold Time                                             |                                                                  |       |                 |        |       |

| H-R<br>DC                   | Hold Time  Duty cycle                                 | ROUT [9:0] valid (Note 10)  RXCLK duty cycle                     | 45    |                 | 55     | %     |

9

| 查 <b>Symbel</b> A                    | N12100"供 <mark>Parameter</mark>       | Condition                                                            | Min | Typ<br>(Note 2) | Max    | Units  |

|--------------------------------------|---------------------------------------|----------------------------------------------------------------------|-----|-----------------|--------|--------|

| t <sub>R</sub> , t <sub>F</sub>      | Output data transition time           | For ROUT [0-9], LOCK, etc. pins. Measured between 20% and 80% levels |     | 0.35            |        | ns     |

| CDET OUT                             | <br>  PUT TIMING SPECIFICATIONS (Rea  |                                                                      |     |                 |        |        |

| t <sub>PDCD</sub>                    | CDET Propagation Delay                | RXCLK rising or falling edge to CDET                                 | 2   | 4               | 6      | ns     |

| CDET OUT                             | PUT TIMING SPECIFICATIONS (Wri        | ļ                                                                    |     |                 |        |        |

| t <sub>S-C</sub>                     | Setup Time                            | CDET valid to RXCLK rising or falling edge                           | 2.6 |                 |        | ns     |

| t <sub>H-C</sub>                     | Hold Time                             | RXCLK rising or falling edge to CDET valid                           | 2.6 |                 |        | ns     |

| SYSCLK L                             | VDS OUTPUT TIMING SPECIFICATI         | ONS                                                                  |     | ,               |        |        |

| t <sub>SYSCLKNDC</sub>               | Duty cycle                            |                                                                      | 40  |                 | 60     | %      |

| JIT <sub>SYSCLK</sub>                | Cycle to cycle jitter                 | (Note 11)                                                            |     | 40              | 65     | ps p-p |

| t <sub>R</sub> , t <sub>F</sub>      | Output transition time                | Between 20% and 80% levels (Note 11)                                 | 0.1 |                 | 0.3    | ns     |

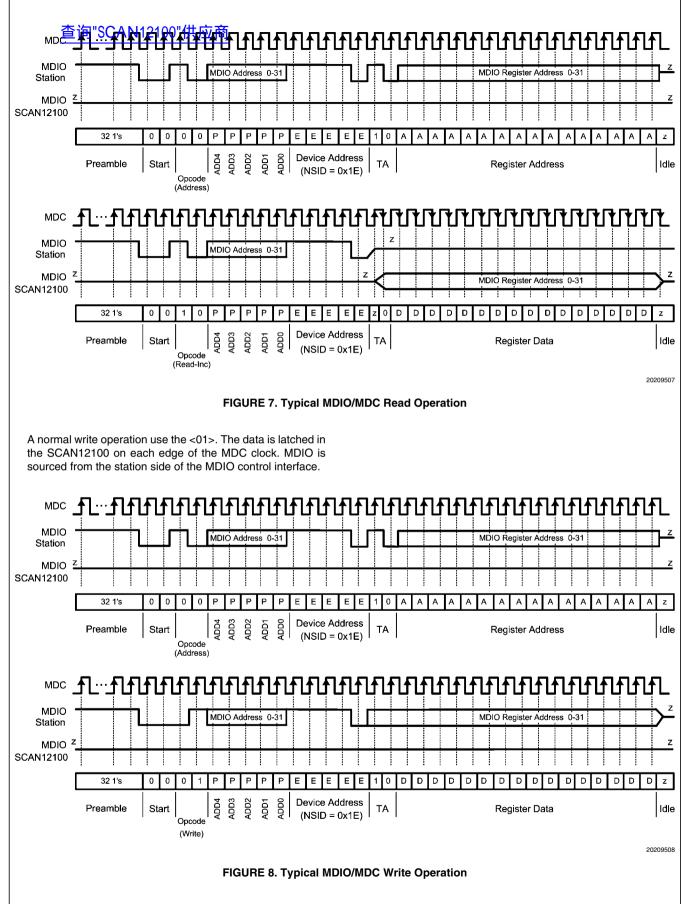

| MDC/MDIO                             | TIMING SPECIFICATIONS (Clause         | 45)                                                                  |     |                 |        |        |

| f <sub>MDC</sub>                     | MDC Frequency                         |                                                                      | 0   |                 | 2.5    | MHz    |

| t <sub>S-MDIO</sub>                  | Setup Time                            | MDIO (input) valid to MDC rising clock                               | 10  |                 |        | ns     |

| t <sub>H-MDIO</sub>                  | Hold Time                             | MDC rising edge to MDIO (input) invalid                              | 10  |                 |        | ns     |

| t <sub>D-MDIO</sub>                  | Delay Time                            | MDIO (output) delay from MDC rising edge                             | 0   |                 | 300    | ns     |

| t <sub>X-MDIO</sub>                  | Transition Time                       | Measured at MDIO when used as output, CL = 470 pF                    |     | 1               |        | ns     |

| MINIMUM F                            | PULSE WIDTH, Hardware Reset (No       | te 12)                                                               |     |                 |        |        |

| t <sub>TX-RST</sub>                  | Transmiter Reset                      | TXPWDNB = 0                                                          |     | 1               |        | us     |

| t <sub>RX-RST</sub>                  | Receiver Reset                        | RXPWDNB = 0                                                          |     | 1               |        | us     |

| t <sub>RST</sub>                     | SerDes Reset                          | RESETB = 0                                                           |     | 1               |        | us     |

| JTAG TIMI                            | NG SPECIFICATIONS                     |                                                                      |     |                 |        |        |

| f <sub>JTAG</sub>                    | JTAG TCK Frequency                    | $R_L = 1000\Omega, C_L = 15 pF$                                      | 25  |                 |        | MHz    |

| t <sub>R-J</sub><br>t <sub>F-J</sub> | TDO data transition time (20% to 80%) |                                                                      |     | 2               |        | ns     |

| t <sub>S-TDI</sub>                   | Setup Time TDI to TCK High or Low     |                                                                      | 2   |                 |        | ns     |

| t <sub>H-TDI</sub>                   | Hold Time TDI to TCK High or Low      |                                                                      | 2   |                 |        | ns     |

| t <sub>s-TMS</sub>                   | Setup Time TMS to TCK High or Low     |                                                                      | 2   |                 |        | ns     |

| t <sub>H-TMS</sub>                   | Hold Time TMS to TCK High or Low      |                                                                      | 2   |                 |        | ns     |

| t <sub>w-TCK</sub>                   | TCK Pulse Width                       |                                                                      | 10  |                 |        | ns     |

| t <sub>w-TRST</sub>                  | TRSTB Pulse Width                     |                                                                      | 2.5 |                 |        | ns     |

| t <sub>REC</sub>                     | Recovery Time TRSTB to TCK            |                                                                      | 14  |                 |        | ns     |

|                                      | LIBRATION MEASUREMENT (DCM)           | (Notes 11, 13, 14)                                                   |     |                 |        |        |

| T <sub>14</sub>                      | T <sub>14</sub> Delay Accuracy        | Receive and Transmit PLLs locked                                     |     |                 | ± 800  | ps     |

| T <sub>offset</sub>                  | T <sub>offset</sub> Delay Accuracy    | to valid hyperframe data.                                            |     |                 | ± 800  | ps     |

| T <sub>ser</sub>                     | Serializer Delay Accuracy             |                                                                      |     |                 | ± 1200 | ps     |

| T <sub>des</sub>                     | Deserializer Delay Accuracy           |                                                                      |     |                 | ± 1200 | ps     |

| T <sub>in-out</sub>                  | T <sub>in-out</sub> Delay Accuracy    |                                                                      |     |                 | ± 1200 | ps     |

| T <sub>out-in</sub>                  | T <sub>out-in</sub> Delay Accuracy    | [                                                                    |     |                 | ± 1200 | ps     |

- Note 1: "Absolute Maximum Ratings" are the ratings beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device

- should be operated at these limits 00"供应商 Note 2: Typical parameters are measured at nominal supply levels and T<sub>A</sub> = 25°C. They are for reference purposes and are not production-tested.

- Note 3: Transmit Jitter testing methodology is defined in Appendix 48B of IEEE 802.2ae-2002. The SCAN12100 transmit output jitter is constant for all valid CPRI datarates. The transmit jitter is significantly less than the specified limits in terms of UI.

- Note 4: CJPAT is a stress pattern defined in IEEE 802.2ae-2002 Appendix 48A

- Note 5: CDET nominal valid duration is determined by the CPRI data rate. CDET timing is similar to the ROUT[0:9] timing.

- Note 6: Transmit or Receive K28.5 pattern. Assumes TXCLK is stable and toggles only after all SerDes clocks become synchronous.

- Note 7: Conditions: The TX PLL is locked, the TXCLK is stable and the TXCLK is synchronous.

- Note 8: Transmit latency is fixed once the link is established and is guaranteed by the Tser specification.

- Note 9: Receive latency is fixed once the link is established and is guaranteed by the Tdes specification.

- Note 10: Receiver output timing specifications for TS-R and TH-R are tested at the CPRI rate of 1.2288 Gbps.

- Note 11: Limits are guaranteed by design and characterization over process, supply voltage, and temperature variations.

- Note 12: Limits are guaranteed by design.

- Note 13: Serial side DCM readings are referenced to the first bit of the K28.5 pattern (110000 0101 001111 1010). Parallel side DCM readings are referenced to the TXCLK or RXCLK edge (not the data edge) that registers the K character as an input or output.

- Note 14: DCM readings are valid when the RXCLK pin on the SCAN12100 is used as an output in "WRITE" mode (RXCLKMODE = 0) and IOVDD = 3.3V.

- Note 15: Edge rate characterization includes the loading effects of 1.0 uF AC-coupling capacitors and 4 inches of 100 ohm differential microstrip.

# AC Timing Diagrams 查询"SCAN12100"供应商

#### Functional Description 查询"SCAN12100"供应商

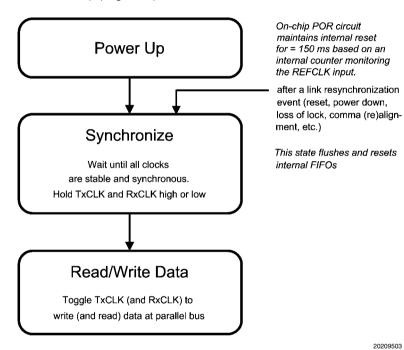

#### POWER UP AND LINK SYNCHRONIZATION

An internal power on reset (POR) circuit disables the transmitter output and sets receiver ROUT[9:0], LOS, LOCKB, and CDET in static high state for approximately 150 ms (150ms is based on an internal counter monitoring the 30.72 MHz Ref-CLK) to allow external clock sources to stabilize. A special power up sequence is not required. Once the transmitter powers up and TXCLK becomes active, the transmitter starts sending valid data. Once the receiver is powered up and RE-FCLK exists, the receiver is ready to receive data. When comma alignment is enabled (CALIGN\_EN = 1), the receiver searches for a valid comma in the incoming stream. When a comma is detected, the receiver performs code group (comma) alignment and presents data on ROUT.

To ensure the parallel bus FIFO read/write pointer distance is half of the total FIFO depth, the following procedure should be followed (e.g., after reset or comma (re)alignment):

- Power up SCAN12100 while holding TXCLK and RXCLK (in read mode) input clocks static low or high. The SCAN12100 will hold both transmitter and receiver FIFO's in reset until the TXCLK and RXCLK start toggling.

- 2. Wait for all clock sources to become synchronous and stable based on the CPRI timing specification.

- Toggle TXCLK and RXCLK input clocks to latch data into and out of the parallel DIN/ROUT buses.

- If at any time the clock requires a resynchronization, such as switching 30.72 MHz system clock. Holding TXCLK and RXCLK (in read mode) static high or low resets the SCAN12100 internal FIFO pointers.

FIGURE 1. Power up State Diagram

#### **POWER DOWN**

When the transmitter is powered down by pulling pin TXP-WDNB down, DOUT is put into a high impedance state. When the receiver is powered down by pulling RXPWDNB down, ROUT[9:0], LOS, LOCKB, CDET, RXCLK, and SYSCLK are high impedance. The MDC/MDIO signal pins are not powered down when TXPWDNB and/or RXPWDNB are low.

#### Resetting the SCAN12100

The SCAN12100 has a rich set of hardware and software reset functions. When performing hardware pin resets, TXP-WDNB and RXPWDNB pins or the RESETB pin must be held low for at least 1 us.

### 查询"SCAN12100"供应商

#### **TABLE 1. Reset Conditions**

| Reset Type                               | What is Reset                                                                   |

|------------------------------------------|---------------------------------------------------------------------------------|

| Initial power up                         | All internal states and registers held at reset for 150 ms after power on. This |

|                                          | reset period is based on an internal counter monitoring the 30.72 MHz           |

|                                          | REFCLK input signal.                                                            |

| TXPWDNB and RXPWDNB low for ≥ 1 us       | All internal states and registers are reset                                     |

| RESETB low for ≥ 1 us                    | Logic reset (including MDIO)                                                    |

| Write "0" to MDIO RESETB register        | Logic reset (excluding MDIO)                                                    |

| SPMODE change                            | Logic reset (excluding MDIO)                                                    |

| TXCLK missing for ≥ 7 cycles             | Transmit FIFO flushed, transmit read/write pointers reset                       |

| RXCLK missing for ≥ 7 cycles (Read Mode) | Receive FIFO flushed, receive read/write pointers reset                         |

| TRSTB (IEEE 1149.1 interface)            | Only IEEE 1149.1 state machine is reset                                         |

#### **Deterministic FIFO Delay at Start Up**

To ensure synchronous operation, REFCLK, TXCLK, and RXCLK should be stable and the receiver synchronized before data is sent into or out of the parallel buses.

#### SCAN12100 CLOCK DOMAINS

Most SerDes have only two clocks: a reference clock (that also acts as a transmit clock) and a receive recovered clock.

The sharing of clocks in these architectures, however, can cause loss of lock issues during RE synchronization. To provide seamless base station synchronization, the SCAN12100 features independent transmit and receive PLLs and four clock signals.

FIGURE 2. SCAN12100 Clock Domains