Mav 2008

<del>和19"供应真</del> Semiconductor

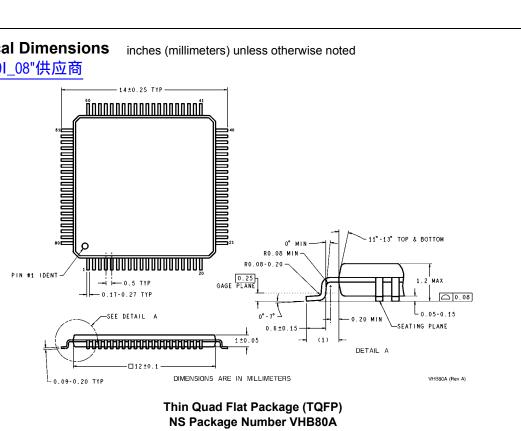

## DP83849I PHYTER® DUAL Industrial Temperature with Flexible Port Switching Dual Port 10/100 Mb/s Ethernet Physical Layer Transceiver

## **General Description**

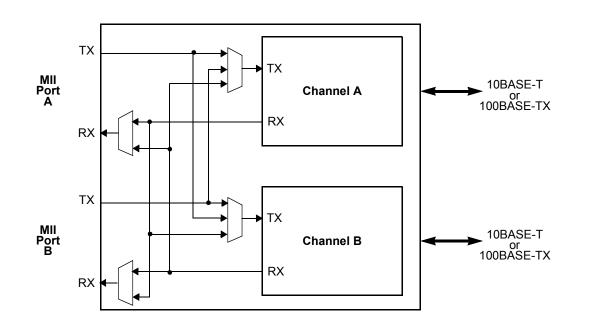

The number of applications requiring Ethernet Connectivity continues to expand. Along with this increased market demand is a change in application requirements. Where single channel Ethernet used to be sufficient, many applications such as wireless remote base stations and industrial networking now require DUAL Port functionality for redundancy or system management.

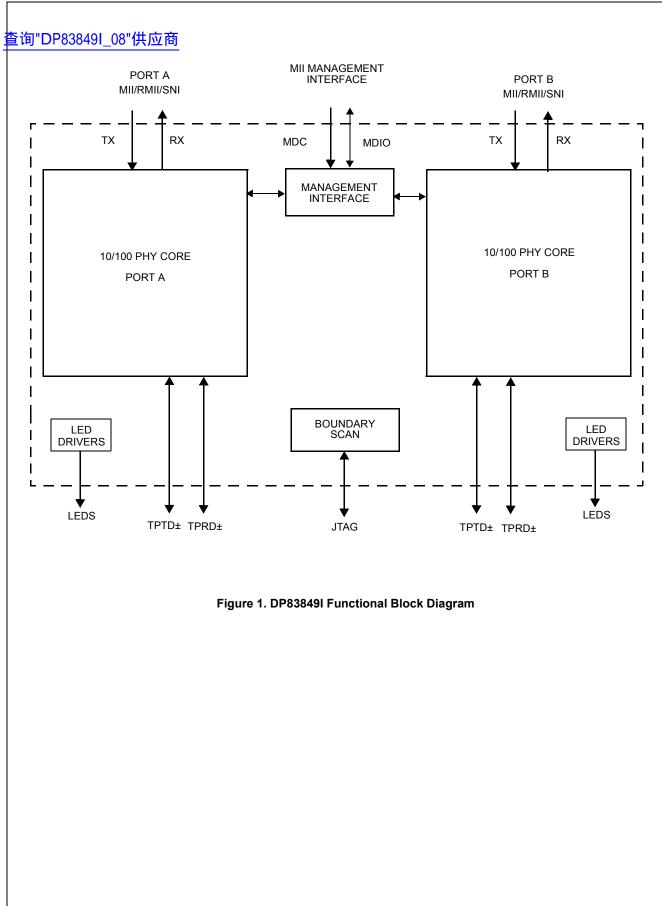

The DP83849I is a highly reliable, feature rich device perfectly suited for industrial applications enabling Ethernet on the factory floor. The DP83849I features two fully independent 10/100 ports for multi-port applications. NATIONAL's unique port switching capability also allows the two ports to be configured to provide fully integrated range extension, media conversion, hardware based failover and port monitoring.

The DP83849I provides optimum flexibility in MPU selection by supporting both MII and RMII interfaces. In addition this device includes a powerful new diagnostics tool to ensure initial network operation and maintenance.

In addition to the TDR scheme, commonly used for detecting faults during installation, NATIONAL's innovative cable diagnostics provides for real time continuous monitoring of the link quality. This allows the system designer to implement a fault prediction mechanism to detect and warn of changing or deteriorating link conditions.

With the DP83849I, National Semiconductor continues to build on its Ethernet expertise and leadership position by providing a powerful combination of features and flexibility, easing Ethernet implementation for the system designer.

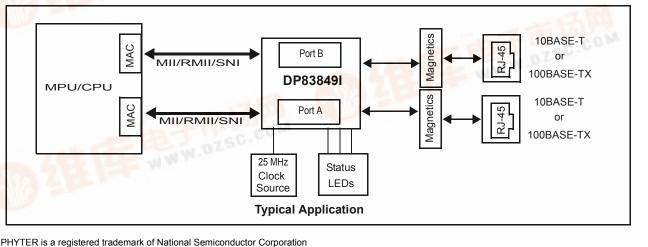

System Diagram

dzsc.com

#### Features

- Low-power 3.3V, 0.18µm CMOS technology

- Low power consumption <600mW Typical

- 3.3V MAC Interface

- Auto-MDIX for 10/100 Mb/s

- **Energy Detection Mode**

- Flexible MII Port Assignment

- **Dynamic Integrity Utility**

- **Dynamic Link Quality Monitoring**

- **TDR based Cable Diagnostic and Cable Length Detection**

DI

- **Optimized Latency for Real Time Ethernet Operation**

- Reference Clock out

- RMII Rev. 1.2 Interface (configurable)

- SNI Interface (configurable)

- MII Serial Management Interface (MDC and MDIO)

- IEEE 802.3u MII

- IEEE 802.3u Auto-Negotiation and Parallel Detection

- IEEE 802.3u ENDEC, 10BASE-T transceivers and filters

- IEEE 802.3u PCS, 100BASE-TX transceivers and filters

- **IEEE 1149.1 JTAG**

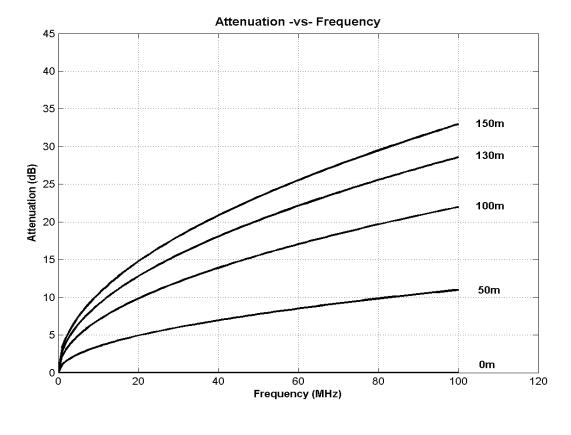

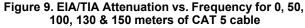

- Integrated ANSI X3.263 compliant TP-PMD physical sub-layer with adaptive equalization and Baseline Wander compensation

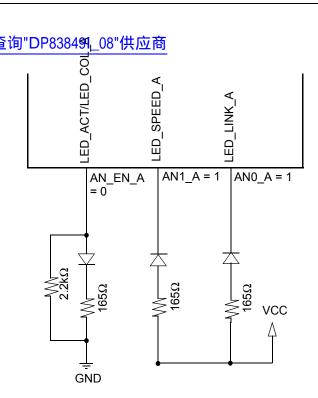

- Programmable LED support for Link, 10 /100 Mb/s Mode, Activity, Duplex and Collision Detect

- Single register access for complete PHY status

- 10/100 Mb/s packet BIST (Built in Self Test)

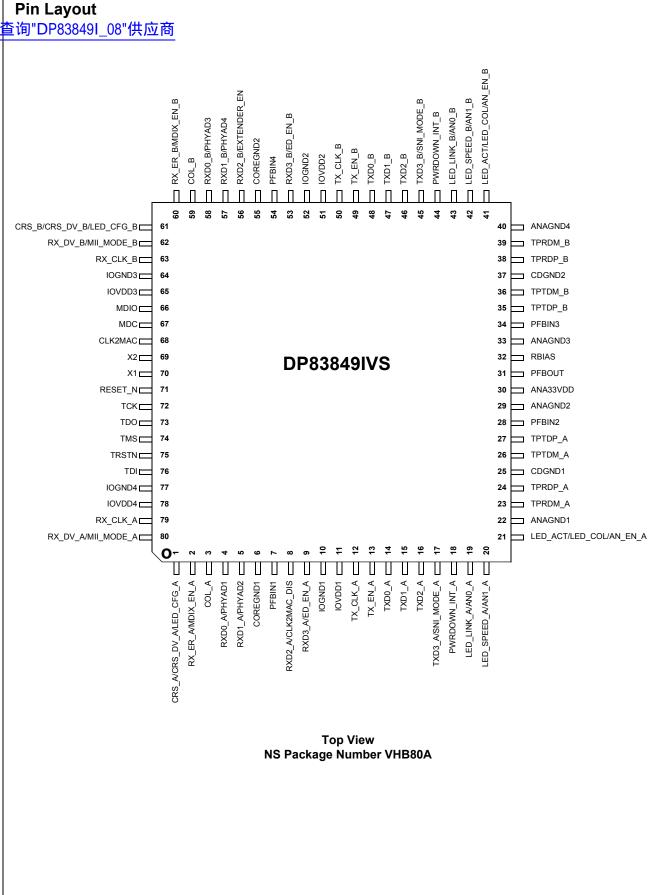

- 80-pin TQFP package (12mm x 12mm) WWW.DZSC.COM

### Applications

- Medical Instrumentation

- Factory Automation

- Motor & Motion Control

- Wireless Remote Base Station

- General Embedded Applications

108 National Semiconductor Corporation

| 1 | 查询"[     | DP83849I_08"供应商 I able of Contents                                                                      |

|---|----------|---------------------------------------------------------------------------------------------------------|

|   |          | Pin Descriptions                                                                                        |

|   | 1.0      | 1.1 Serial Management Interface                                                                         |

|   |          | 1.2 MAC Data Interface       10                                                                         |

|   |          | 1.3 Clock Interface                                                                                     |

|   |          | 1.4 LED Interface                                                                                       |

|   |          | 1.5 JTAG Interface                                                                                      |

|   |          | 1.6 Reset and Power Down                                                                                |

|   |          | 1.7 Strap Options                                                                                       |

|   |          | 1.8 10 Mb/s and 100 Mb/s PMD Interface                                                                  |

|   |          | 1.9 Special Connections                                                                                 |

|   |          | 1.10 Power Supply Pins                                                                                  |

|   |          | 1.11 Package Pin Assignments                                                                            |

|   | 2.0      | Configuration                                                                                           |

|   |          | 2.1 Auto-Negotiation                                                                                    |

|   |          | 2.1.1 Auto-Negotiation Pin Control                                                                      |

|   |          | 2.1.2 Auto-Negotiation Register Control                                                                 |

|   |          | 2.1.3 Auto-Negotiation Parallel Detection                                                               |

|   |          | 2.1.4 Auto-Negotiation Restart       19         2.1.5 Enabling Auto-Negotiation via Software       19   |

|   |          | 2.1.6 Auto-Negotiation Complete Time                                                                    |

|   |          | 2.2 Auto-MDIX                                                                                           |

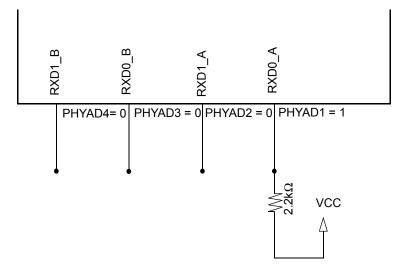

|   |          | 2.3 PHY Address                                                                                         |

|   |          | 2.3.1 MII Isolate Mode                                                                                  |

|   |          | 2.4 LED Interface                                                                                       |

|   |          | 2.4.1 LEDs                                                                                              |

|   |          | 2.4.2 LED Direct Control                                                                                |

|   |          | 2.5 Half Duplex vs. Full Duplex                                                                         |

|   |          | 2.6 Internal Loopback         .22           2.7 BIST         .22                                        |

|   | 20       | MAC Interface                                                                                           |

|   | 3.0      |                                                                                                         |

|   |          | 3.1 MII Interface                                                                                       |

|   |          | 3.1.2 Collision Detect                                                                                  |

|   |          | 3.1.3 Carrier Sense                                                                                     |

|   |          | 3.2 Reduced MII Interface                                                                               |

|   |          | 3.3 10 Mb Serial Network Interface (SNI)                                                                |

|   |          | 3.4 Single Clock MII Mode                                                                               |

|   |          | 3.5 Flexible MII Port Assignment                                                                        |

|   |          | 3.5.1 RX MII Port Mapping                                                                               |

|   |          | 3.5.2 TX MII Port Mapping         28           3.5.3 Common Flexible MII Port Configurations         28 |

|   |          | 3.5.4 Strapped Extender Mode                                                                            |

|   |          | 3.5.5 Notes and Restrictions                                                                            |

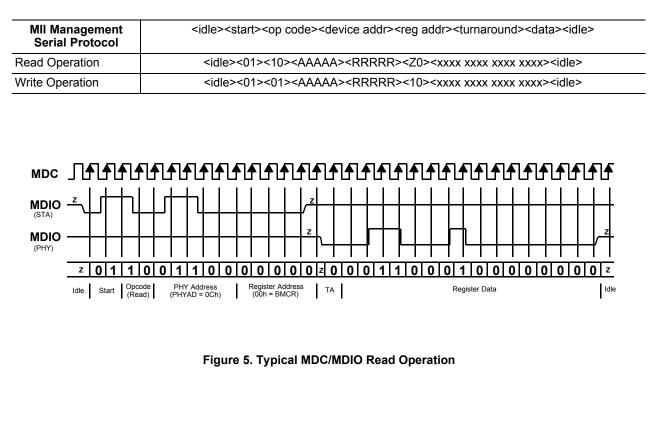

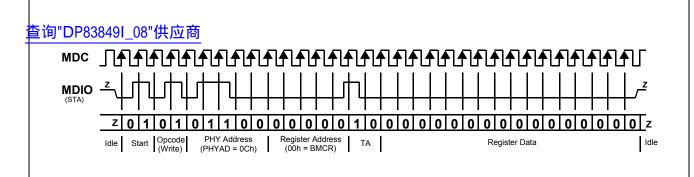

|   |          | 3.6 802.3u MII Serial Management Interface                                                              |

|   |          | 3.6.1 Serial Management Register Access                                                                 |

|   |          | 3.6.2 Serial Management Access Protocol                                                                 |

|   |          | 3.6.3 Serial Management Preamble Suppression                                                            |

|   | <u> </u> | 3.6.4 Simultaneous Register Write                                                                       |

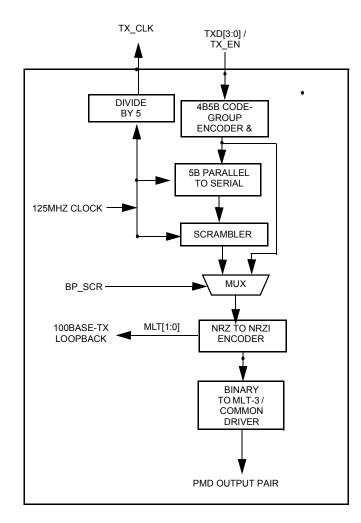

|   | 4.0      | Architecture.         32           4.1.100DASE TV TRANSMITTER         32                                |

| ļ |          | 4.1 100BASE-TX TRANSMITTER                                                                              |

| ļ |          | 4.1.1 Code-group Encoding and Injection         34           4.1.2 Scrambler         34                 |

| ļ |          | 4.1.3 NRZ to NRZI Encoder                                                                               |

|   |          | 4.1.4 Binary to MLT-3 Convertor                                                                         |

| ļ |          | 4.2 100BASE-TX RECEIVER                                                                                 |

|   |          |                                                                                                         |

| <b>4</b> 9 |

|------------|

| Õ          |

| က          |

| ω          |

| ር በ        |

| <b>n</b>   |

|   |        |        | 21 Analog Fr    | ront End                                   |  |

|---|--------|--------|-----------------|--------------------------------------------|--|

|   | *<br>* |        |                 |                                            |  |

| 1 | 当'印"L  | JP8384 | 1-08-1-57-16    | anal Processor                             |  |

|   |        |        |                 | se Line Wander Compensation                |  |

|   |        |        |                 | etect                                      |  |

|   |        |        |                 | NRZI Decoder                               |  |

|   |        |        |                 | IRZ                                        |  |

|   |        |        |                 | Parallel                                   |  |

|   |        |        |                 | bler                                       |  |

|   |        |        |                 | up Alignment                               |  |

|   |        |        |                 | coder                                      |  |

|   |        |        |                 |                                            |  |

|   |        |        |                 | E-TX Link Integrity Monitor                |  |

|   |        | 4.0    |                 | D Detection                                |  |

|   |        | 4.3    |                 | ANSCEIVER MODULE                           |  |

|   |        |        |                 | nal Modes                                  |  |

|   |        |        |                 | uelch                                      |  |

|   |        |        |                 | Detection and SQE                          |  |

|   |        |        |                 | ense                                       |  |

|   |        |        |                 | ink Pulse Detection/Generation             |  |

|   |        |        |                 | unction                                    |  |

|   |        |        |                 | c Link Polarity Detection and Correction   |  |

|   |        |        |                 | and Receive Filtering                      |  |

|   |        |        |                 | er                                         |  |

|   |        |        |                 | r                                          |  |

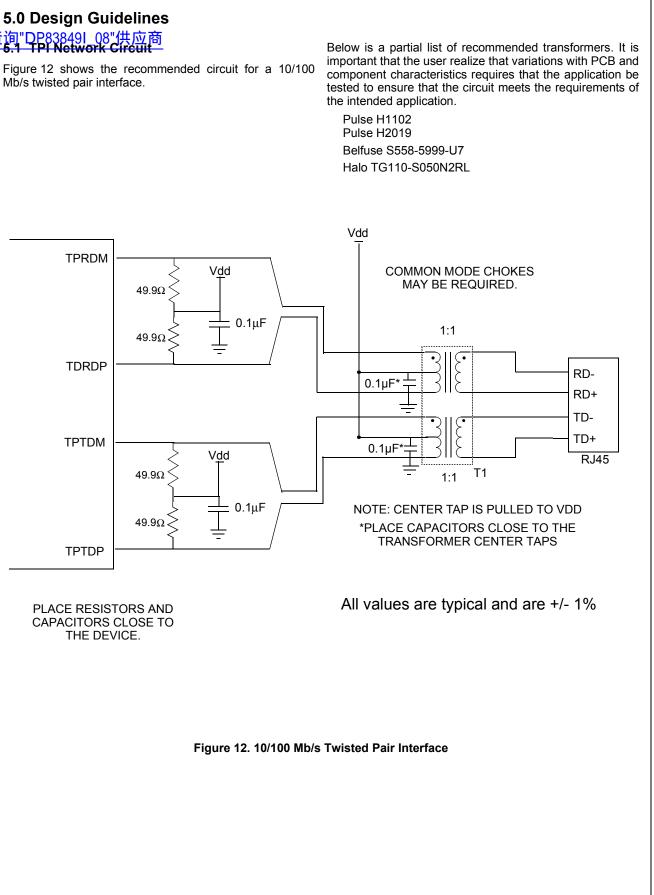

|   | 5.0    | Desig  | n Guideline     | es                                         |  |

|   |        | 5.1    | TPI Network C   | Circuit                                    |  |

|   |        |        |                 |                                            |  |

|   |        |        |                 | Requirements                               |  |

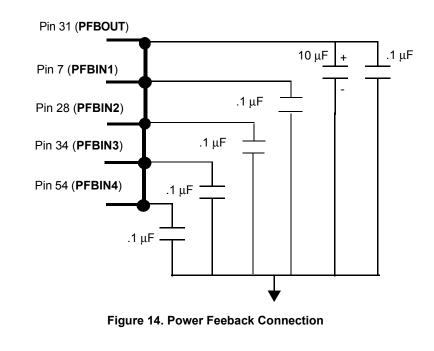

|   |        |        |                 | ack Circuit                                |  |

|   |        |        |                 |                                            |  |

|   |        | 5.5    |                 | Interrupt                                  |  |

|   |        |        |                 | wn Control Mode                            |  |

|   |        |        |                 | Mechanisms                                 |  |

|   |        |        |                 | t Mode                                     |  |

|   |        | 5.7    | Link Diagnosti  | ic Capabilities                            |  |

|   |        |        | 5.7.1 Linked Ca | able Status                                |  |

|   |        |        |                 | larity Reversal                            |  |

|   |        |        |                 | ble Swap Indication                        |  |

|   |        |        | 5.7.1.3 100     | OMB Cable Length Estimation    45          |  |

|   |        |        |                 | equency Offset Relative to Link Partner 45 |  |

|   |        |        | 5.7.1.5 Cal     | ble Signal Quality Estimation              |  |

|   |        |        |                 | lity Monitor                               |  |

|   |        |        | 5.7.2.1 Lin     | k Quality Monitor Control and Status 45    |  |

| ļ |        |        |                 | ecking Current Parameter Values 45         |  |

|   |        |        | 5.7.2.3 Thr     | reshold Control                            |  |

|   |        |        | 5.7.3 TDR Cabl  | le Diagnostics                             |  |

|   |        |        | 5.7.3.1 TD      | R Pulse Generator                          |  |

|   |        |        | 5.7.3.2 TD      | R Pulse Monitor                            |  |

|   |        |        |                 | R Control Interface                        |  |

|   |        |        | 5.7.3.4 TD      | R Results                                  |  |

|   | 6.0    | Rese   | Operation       |                                            |  |

|   |        |        | •               |                                            |  |

| ļ |        |        |                 | Reset                                      |  |

|   |        |        |                 |                                            |  |

|   | 7 0    |        |                 |                                            |  |

| ļ | 1.0    | -      |                 |                                            |  |

|   |        | 7.1    |                 | nition                                     |  |

| ļ |        |        |                 | de Control Register (BMCR) 54              |  |

| ļ |        |        |                 | de Status Register (BMSR) 56               |  |

|   |        |        |                 | tifier Register #1 (PHYIDR1)               |  |

|   |        |        |                 | tifier Register #2 (PHYIDR2) 57            |  |

| ļ |        |        | 7.1.5 Auto-Neg  | otiation Advertisement Register (ANAR) 57  |  |

|   |        |        |                 |                                            |  |

|          | 7.1.6 Auto-Negotiation Link Partner Ability Register (ANLPAR) (BASE Page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 本海       | All To Auto Negotiation Link Partner Ability Register (ANLPAR) (Next Page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <u> </u> | DP838471178Auto-Negotiation Link Partner Ability Register (ANLPAR) (Next Page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.1.9 Auto-Negotiation Next Page Transmit Register (ANNPTR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.1.10 PHY Status Register (PHYSTS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.1.11 MII Interrupt Control Register (MICR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.1.12 MII Interrupt Status and Misc. Control Register (MISR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.1.13 Page Select Register (PAGESEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.2 Extended Registers - Page 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.2.1 False Carrier Sense Counter Register (FCSCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.2.2 Receiver Error Counter Register (RECR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.2.3 100 Mb/s PCS Configuration and Status Register (PCSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.2.4 RMII and Bypass Register (RBR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.2.5 LED Direct Control Register (LEDCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.2.6 PHY Control Register (PHYCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.2.7 10 Base-T Status/Control Register (10BTSCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.2.8 CD Test and BIST Extensions Register (CDCTRL1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.2.9 Phy Control Register 2 (PHYCR2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.2.10 Energy Detect Control (EDCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 7.3 Link Diagnostics Registers - Page 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.3.1 100Mb Length Detect Register (LEN100_DET), Page 2, address 14h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 7.3.2 100Mb Frequency Offset Indication Register (FREQ100), Page 2, address 15h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

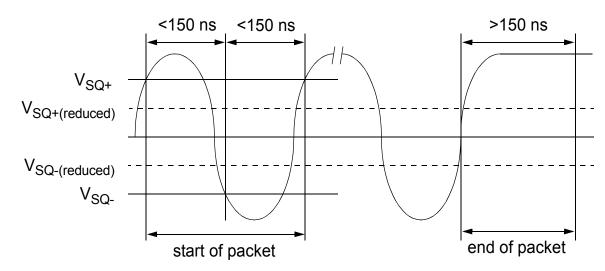

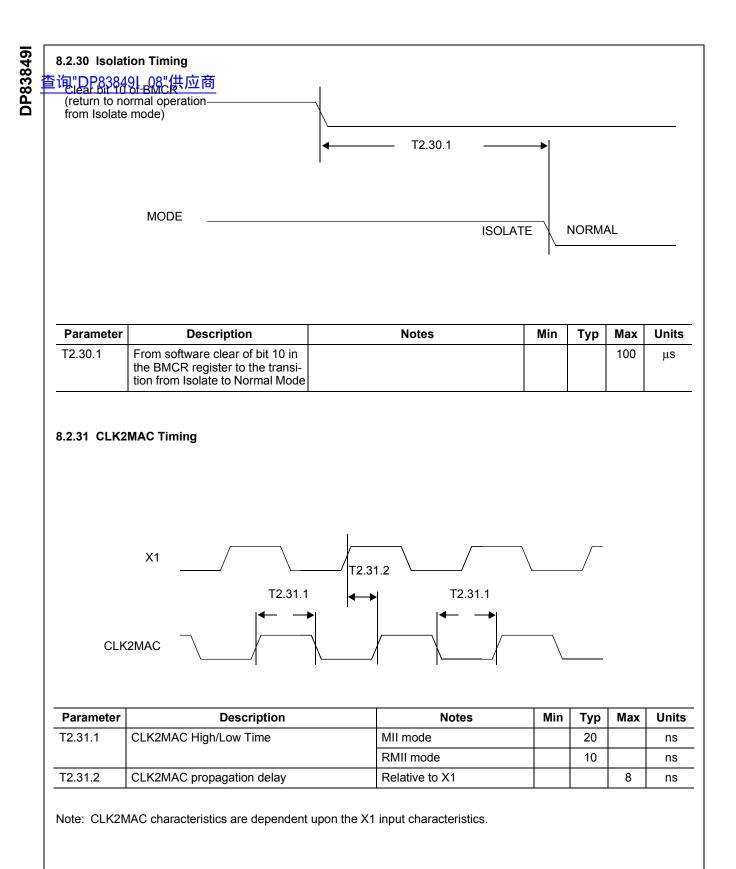

|          | 7.3.3 TDR Control Register (TDR_CTRL), Page 2, address 16h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |