|                               | REVISIONS                        |        |            |    |                                                              |                                          |      |      |      |   |                                                                                                                         |      |    |    |               |                                                  |          |          |          |          |          |          |      |                                               |   |

|-------------------------------|----------------------------------|--------|------------|----|--------------------------------------------------------------|------------------------------------------|------|------|------|---|-------------------------------------------------------------------------------------------------------------------------|------|----|----|---------------|--------------------------------------------------|----------|----------|----------|----------|----------|----------|------|-----------------------------------------------|---|

| LTR                           |                                  | _      |            |    | ***************************************                      | ı                                        | DESC | CRIP | TION |   |                                                                                                                         |      |    |    |               |                                                  |          | DAT      | E (YR    | -MO-[    | DA)      | A        | PPRO | WED                                           |   |

| LTR                           |                                  |        |            |    |                                                              |                                          |      |      |      |   |                                                                                                                         | PPHC |    |    |               |                                                  |          |          |          |          |          |          |      |                                               |   |

| REV                           | <del>- 1</del>                   |        |            |    | <u> </u>                                                     |                                          |      |      |      |   | Ī                                                                                                                       |      |    |    | <del></del> - | <b>I</b>                                         | Ī        |          | <u> </u> |          | <u> </u> | <b>I</b> |      | <u>,                                     </u> | r |

| SHEET                         | -                                | +-     |            |    | -                                                            |                                          | ┢    |      | -    | ┢ | $\vdash$                                                                                                                | Н    | -  |    | _             | <del>                                     </del> | <b>-</b> | ┞        | ┢        |          | ┢        |          |      |                                               |   |

| REV                           |                                  | T      |            |    | <b>-</b>                                                     | _                                        | _    |      |      | ┢ |                                                                                                                         |      | -  |    |               | 一                                                | <u> </u> | <u> </u> |          | <u> </u> |          |          |      |                                               |   |

| SHEET                         | _                                |        |            |    |                                                              |                                          |      |      |      |   |                                                                                                                         |      |    |    |               |                                                  |          |          |          |          | Π        |          |      |                                               |   |

| REV STA                       | tus .                            | RI     | V          |    |                                                              |                                          |      |      |      |   |                                                                                                                         |      |    |    |               |                                                  |          |          |          |          |          |          |      |                                               |   |

| OF SHE                        |                                  | SH     | IEET       |    | 1                                                            | 2                                        | 3    | 4    | 5    | 6 | 7                                                                                                                       | 8    | 9  | 10 | 11            | 12                                               | 13       | 14       | 15       | 16       |          |          |      |                                               |   |

| STANDARDIZED MILITARY DRAWING |                                  |        |            |    | CHECKED BY  CHECKED BY  CHECKED BY  APPROVED BY  APPROVED BY |                                          |      |      |      |   | DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444  MICROCIRCUIT, BIPOLAR, BIDIRECTIONAL I/O PORT, MONOLITHIC SILICON |      |    |    |               |                                                  |          |          |          |          |          |          |      |                                               |   |

|                               | SY ALL DI<br>AGENCIES<br>MENT OF | EPARTI | MENT<br>IE | rs | 2                                                            | DRAWING APPROVAL DATE   SIZE   CAGE CODE |      |      |      |   |                                                                                                                         | 87   | 57 | 6  |               |                                                  |          |          |          |          |          |          |      |                                               |   |

DESC FORM 193 SEP 87

\* U.S. GOVERNMENT PRINTING OFFICE: 1987 — 748-129/60911

5962-E365

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

| 1 | 22 | UDE |

|---|----|-----|

$1.1\,$  Scope. This drawing describes device requirements for class B microcircuits in accordance with  $1.2.1\,$  of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

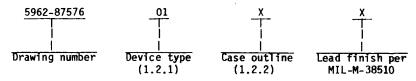

1.2 Part number. The complete part number shall be as shown in the following example:

1.2.1 Device type. The device type shall identify the circuit function as follows:

| Device type | Generic number | Circuit function                     |

|-------------|----------------|--------------------------------------|

| 01          | 8X371          | 8-bit latched bidirectional I/O port |

1.2.2 <u>Case outline</u>. The case outline shall be as designated in appendix C of MIL-M-38510, and as follows:

```

Outline letter

Case outline

D-11 (24-lead, 1.250" x .410" x .225") dual-in-line package

```

1.3 Absolute maximum ratings.

1.4 Recommended operating conditions.

```

Supply voltage - - - - - - - - - - - - - 4.5 V dc to 5.5 V dc Case operating temperature range (T_C) - - - - - - - - - - - - 55°C to +125°C Minimum high level input voltage (V_{IH}) - - - - - +2.0 V dc Maximum low level input voltage (V_{IL}) - - - - - - - - - - - +0.8 V dc

```

$\overline{1/}$  Must withstand the added PD due to short circuit tests; e.g.,  $I_{OS}$ .

DESC FORM 193A SEP 87

道"5892ICABLE DOCUMENTS 应商

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510

- Microcircuits, General Specification for.

**STANDARD**

MILITARY

MIL-STD-883

- Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

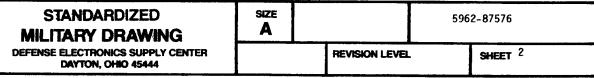

- 3.2.1 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.2 <u>Truth tables</u>. The truth tables shall be as specified on figure 2.

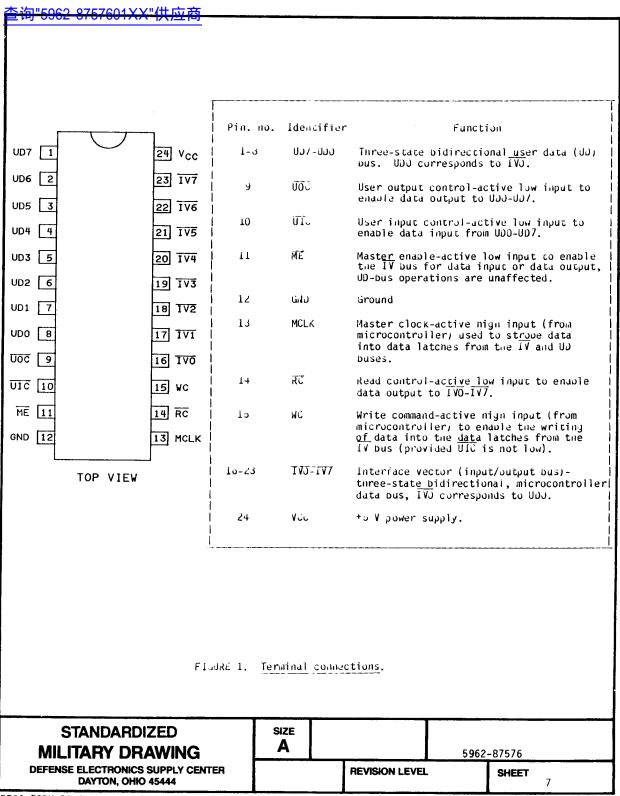

- 3.2.3 Logic diagram. The logic diagram shall be as specified on figure 3.

- 3.2.4 Case outline. The case outline shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.4 herein.

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.4. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

# STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 SIZE A FREVISION LEVEL SHEET 3

DESC FORM 193A SEP 87

| I ABLE                                              | I. <u>Flec</u>        | trical performance characteristics.                                                                                                                          |           |               |                   |      |  |

|-----------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-------------------|------|--|

| Test                                                | <br> Symbol           | Conditions<br>-55°C < T <sub>C</sub> < +125°C                                                                                                                | Group A   | Lin           | Unit              |      |  |

|                                                     |                       | Conditions $-55^{\circ}\text{C} < T_{\text{C}} \le +125^{\circ}\text{C}$ 4.5 $\text{V} \le \text{V}_{\text{CC}} \le 5.5 \text{V}$ unless otherwise specified | subgroups | Min           | Max               | <br> |  |

| Supply voltage                                      | Vcc                   | <br>                                                                                                                                                         | 1,2,3     | <br>  4.5<br> | 5.5               | ٧    |  |

| High level input voltage                            | I A <sup>I H</sup>    |                                                                                                                                                              | 1,2,3     | 2.0           | <br>              | ٧    |  |

| Low level input voltage                             | V <sub>IL</sub>       |                                                                                                                                                              | 1,2,3     | <br>          | 0.8<br>  0.8      | ٧    |  |

| Input clamp voltage                                 | IV <sub>IC</sub>      | V <sub>CC</sub> = 4.5 V I <sub>I</sub> = -10 mA                                                                                                              | 1,2,3     | <br> <br>     | -1.5              | ٧    |  |

| High level input current $1/$                       | I IH                  | V <sub>CC</sub> = 5.5 V V <sub>IH</sub> = 2.7 V                                                                                                              | 1,2,3     | <br> <br>     | 100               | μА   |  |

| Low level input current $\underline{1}/$            | IIL                   | V <sub>CC</sub> = 5.5 V V <sub>IL</sub> < 0.5 V                                                                                                              | 1,2,3     | <br> <br>     | -550 <br> -510    | μА   |  |

| Low level output voltage<br>TV bus (TVO-TV7)        | V <sub>OL</sub>       | V <sub>CC</sub> = 4.5 V I <sub>OL</sub> = 16 mA                                                                                                              | 1,2,3     |               | 0.55              | ٧    |  |

| user bus (UD4-UD7)                                  | <br> <br>             | V <sub>CC</sub> = 4.5 V I <sub>OL</sub> = 24 mA                                                                                                              | 1,2,3     |               | 0.55              | ν-   |  |

| High level output voltage                           | v <sub>OH</sub>       | V <sub>CC</sub> = 4.5 V I <sub>OH</sub> = -3.2 mA                                                                                                            | 1,2,3     | 2.4           |                   | ٧    |  |

| Short circuit output current 2/<br>TV bus (TVO-TV7) | Ios                   | V <sub>CC</sub> = 5.5 V                                                                                                                                      | 1,2,3     | -20           |                   | mA   |  |

| UD bus (UDO-UD7)                                    | <br>                  | V <sub>CC</sub> = 5.5 V                                                                                                                                      | 1,2,3     | -10           |                   | mA   |  |

| Supply current                                      | Icc                   | V <sub>CC</sub> = 5.5 V ME = UOC = V <sub>CC</sub>                                                                                                           | 1,2,3     |               | 150               | mA   |  |

| Function test                                       |                       | See 4.3.1c <u>3</u> /                                                                                                                                        | <br>  7,8 | <br> <br>     |                   |      |  |

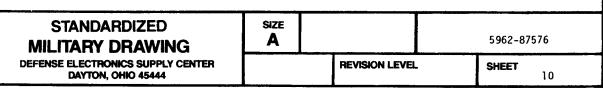

| Pulse widths:                                       | <u>i</u>              |                                                                                                                                                              |           | j             | į                 |      |  |

| Clock high + MCLK to + MCLK                         | i<br> t <sub>W1</sub> | <u>3</u> /                                                                                                                                                   | 9,10,11   | 30            | i  <br>  i<br>  i | ns   |  |

| User input control + UIC to                         | tw2                   | MCLK = High 3/                                                                                                                                               | 9,10,11   | 35            |                   | ns   |  |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |                | 596 | 52-87576 |   |

|------------------------------------------------------|------------------|----------------|-----|----------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | -   | SHEET    | 4 |

DESC FORM 193A SEP 87

| 查询"5902-8757601XX"供应高<br>TABLE 1. ET                            | ectrical         | performance ch                 | aracteristic                                                                    | s - Cont       | inued.                     |                          |               |  |  |

|-----------------------------------------------------------------|------------------|--------------------------------|---------------------------------------------------------------------------------|----------------|----------------------------|--------------------------|---------------|--|--|

| Test                                                            | <br> Symbol      | -55°C<br>  4.5 V               | nditions<br>< T <sub>C</sub> < +125°<br>< V <sub>CC</sub> < 5.5<br>erwise speci | C<br>V<br>fied | <br> Group A<br> subgroups | Limits<br> <br> Min  Max | Uni           |  |  |

| Propagation delays:                                             | ł<br>            | <br>                           |                                                                                 |                |                            |                          |               |  |  |

| UD propagation delay UD to TV                                   | tpD1             | <br>  MCLK                     | = UIC = Low                                                                     | 3/             | 9,10,11                    | <br>  45                 | l ns          |  |  |

| UD clock delay † MCLK to TV                                     | tpD2             | UD = Stable;<br>RC = WC = ME   | = UIC = Low                                                                     | <u>3</u> /     |                            | 55                       | ns            |  |  |

| UD input delay ↓ UIC to IV                                      | t <sub>PD3</sub> | UD = Stable;<br>RC = WC = ME   | MCLK = High<br>= Low                                                            | <u>3</u> /     |                            | 55                       | ns            |  |  |

| TV data propagation delay TV to UD                              | t <sub>PD4</sub> | MCLK = WC = U<br>ME = UOC = RC |                                                                                 | <u>3</u> /     |                            | 45                       | ns            |  |  |

| TV data clock delay<br>† MCLK to UD                             | t <sub>PD5</sub> | WC = UIC = Hi<br>ME = UOC = RC | gh; TV = Stal<br>= Low                                                          | ole <u>3</u> / |                            | <br>    55               | l<br>  ns<br> |  |  |

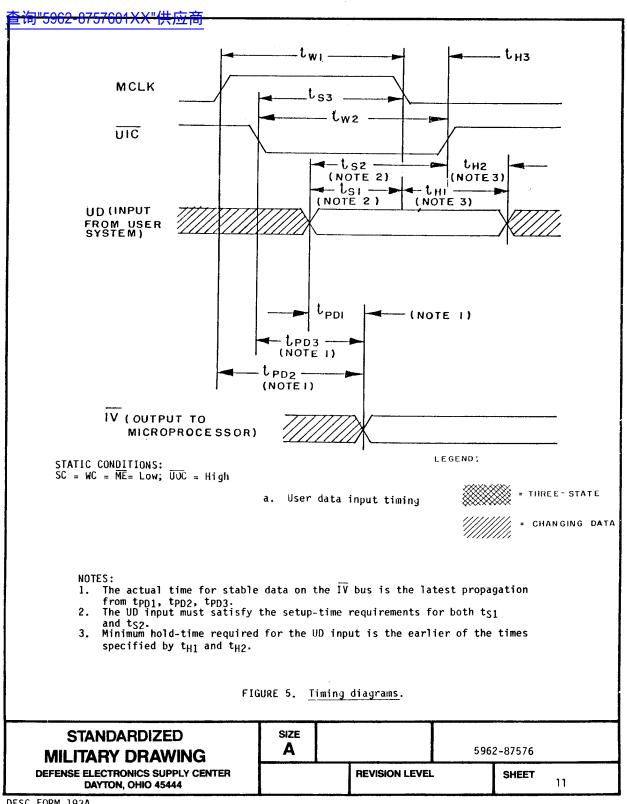

| Output enable timing:                                           | <b> </b><br>     |                                |                                                                                 |                |                            |                          | <b>i</b><br>! |  |  |

| UD output enable + UOC to UD                                    | t <sub>OE1</sub> | UIC = High                     |                                                                                 | <u>3</u> /     |                            | 45                       | ns            |  |  |

| UD input recovery † UIC to UD                                   | t <sub>OE2</sub> | UOC = Low                      |                                                                                 | <u>3</u> /     |                            | 45                       | l ns          |  |  |

| TV data master enable<br>→ ME to TV                             | t <sub>0E3</sub> | WC = RC = Low                  |                                                                                 | <u>3</u> /     |                            | 45                       | ns            |  |  |

| TV data read enable<br>↓ RC to TV                               | t <sub>OE4</sub> | WC = ME = Low                  |                                                                                 | <u>3</u> /     |                            | 45                       | ns            |  |  |

| TV data write recovery<br>+ WC to TV                            | t <sub>OE5</sub> | RC = ME = Low                  |                                                                                 | 3/             | )<br>                      | 45                       | l ns          |  |  |

| Output disable timing:                                          |                  |                                |                                                                                 | -              | <br>                       | ļ                        |               |  |  |

| UD output disable $\ ^{\uparrow}$ $\overline{\text{UOC}}$ to UD | t <sub>OD1</sub> | UIC = High                     |                                                                                 | <u>3</u> /     | <br>                       | <br>  40                 | ns            |  |  |

| UD input override + VIC to UD                                   | t <sub>OD2</sub> | UOC = Low                      |                                                                                 | <u>3</u> /     | <br>                       | 45                       | ns            |  |  |

| <pre>IV data master disable</pre>                               | t <sub>OD3</sub> | WC = RC = Low                  |                                                                                 | <u>3/ 4/</u>   |                            | <br>  40                 | ns            |  |  |

| TV data rèad disable<br>↑ RC to TV                              | t <sub>004</sub> | WC = ME = Low                  |                                                                                 | <u>3/ 4/</u>   | <br>                       | 40                       | ns            |  |  |

| TV data write override<br>↑ WC to TV                            | t <sub>OD5</sub> | RC = ME = Low                  |                                                                                 | <u>3/ 4/</u>   | <br>                       | 40 <br>  40              | ns            |  |  |

| ee footnotes at end of table.                                   |                  |                                |                                                                                 |                |                            |                          | •             |  |  |

| STANDARDIZED MILITARY DRAWING                                   |                  | SIZE<br>A                      |                                                                                 |                | 5962-                      | 87576                    | <del></del>   |  |  |

| DEFENSE ELECTRONICS SUPPLY CE<br>DAYTON, OHIO 45444             |                  | REVISION LEVEL                 |                                                                                 |                |                            | SHEET 5                  |               |  |  |

| TABLE I. ET                                      | ectrical        | performance characteristics                                                                                       | - Coi                      | ntinued.                     |              |          |          |

|--------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|--------------|----------|----------|

| Test                                             | <br> Symbol<br> | Conditions<br>  -55°C < T <sub>C</sub> < +125°C<br>  4.5 V < V <sub>CC</sub> < 5.5 \<br>  unless otherwise specif | <br> Group A<br> subgroups | Limits<br> <br> Min  Max<br> |              | Unit     |          |

| Setup time:                                      | <br>            |                                                                                                                   |                            |                              | i i          |          |          |

| UD clock setup time<br>UD to + MCLK              | t <sub>S1</sub> | UIC = Low                                                                                                         | <u>3</u> /                 | 9,10,11                      | 15  <br>  15 |          | ns       |

| UD setup time UD to † UIC                        | t <sub>S2</sub> | <br>  MCLK = High<br>                                                                                             | <u>3</u> /                 |                              | 25           |          | ns       |

| User input control setup time<br>+ UIC to + MCLK | t <sub>S3</sub> |                                                                                                                   | 3/                         |                              | 25           |          | ns       |

| TV data setup time<br>TV to + MCLK               | ts4             | WC = UIC = High; ME = Low                                                                                         | 3/                         | <br> <br> <br>               | 15           |          | ns       |

| TV master enable setup time<br>+ ME to + MCLK    | t <sub>S5</sub> | 5/<br>  WC = UIC = High<br>                                                                                       | <u>3</u> /                 | <br> <br>                    | 20           |          | ns       |

| TV write control setup time  ↑ WC to ↑ MCLK      | ts6             | ME = Low; UIC = High                                                                                              | 3/                         | -<br> <br> -<br>             | 40           |          | ns       |

| Hold times:                                      |                 |                                                                                                                   |                            | _<br>                        | Ī            | İ        |          |

| UD clock hold time<br>+ MCLK to UD               | t <sub>H1</sub> | UIC = Low                                                                                                         | <u>3</u> /                 | <br>                         | 20           |          | ns       |

| UD control hold time + UTC to UD                 | t <sub>H2</sub> | MCLK = High                                                                                                       | 3/                         | <br>                         | 10           |          | ns       |

| User input control hold time + MCLK to † UTC     | t <sub>H3</sub> |                                                                                                                   | <u>3</u> /                 |                              | 0            |          | ns       |

| TV data hold time<br>+ MCLK to TV                | t <sub>H4</sub> | WC = UIC = High; ME = Low                                                                                         | <u>3</u> /                 | 9   10,11                    | 5  <br>20    | <u> </u> | ns<br>ns |

| TV master enable hold time<br>+ MCLK to ↑ ME     | t <sub>H5</sub> | 5/<br>WE = UIC = High                                                                                             | 3/                         | 9,10,11                      | 0            | İ        | ns       |

| TV write control hold time<br>+ MCLK to + WC     | t <sub>H6</sub> | ME = Low; UIC = High                                                                                              | <u>3</u> /                 |                              | 0            |          | ns       |

The input current includes the three-state leakage current of the output driver on the data lines. Only one output may be shorted at a time.

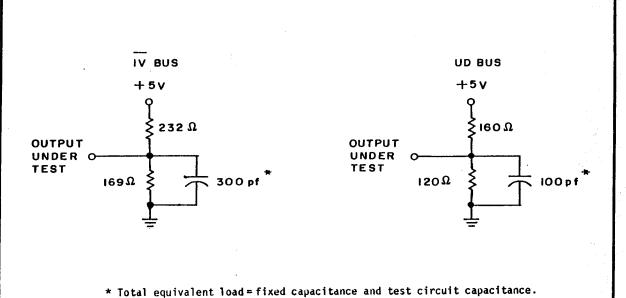

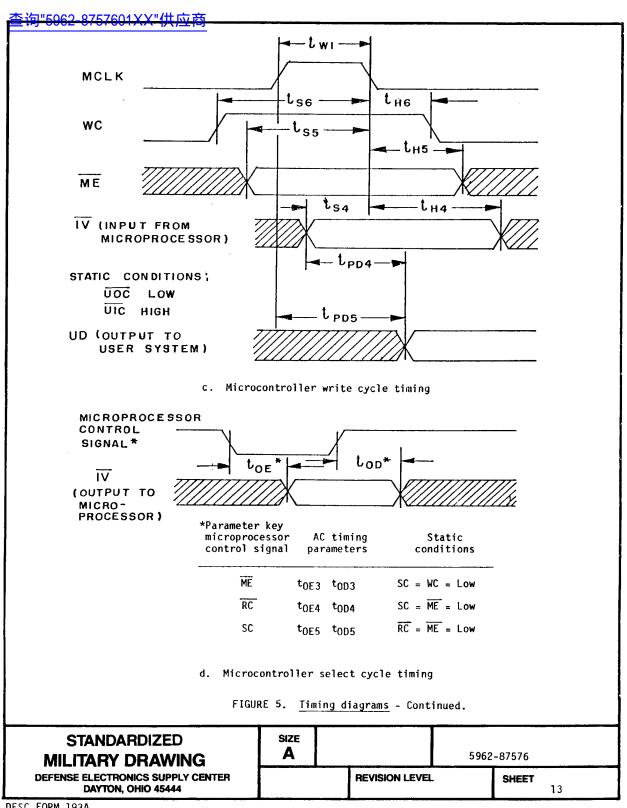

Test loading circuit and timing diagrams see figures 4 and 5.

These parameters are measured with a capacitive loading of 50 pf and represent the output driver

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |               |    | 5962-87576 |  |

|------------------------------------------------------|-----------|---------------|----|------------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVI | EL | SHEET 6    |  |

DESC FORM 193A SEP 87

If ME is to be high (inactive), it must be setup before the rising edge and held after the falling edge of MCLK to avoid unintended writing into or selection of the I/O port.

Functional operation

UD bus control

The user data (UD) bus interface is controlled by the  $\overline{\text{UIC}}$  and  $\overline{\text{UOC}}$  inputs. Data input to the UD bus is synchronous with MCLK, that is, with  $\overline{\text{UIC}}$  low, information is written into the data latches only when MCLK is high. Output drivers on the UD bus are enabled when  $\overline{\text{UOC}}$  is low and  $\overline{\text{UIC}}$  is high.

#### Input/output control of UD Bus

| ÜĪĈ | VÖC | MCLK | function of UD bus |

|-----|-----|------|--------------------|

| Н   | L   | х    | output             |

| L   | х   | н    | input data         |

| L   | х   | L    | inactive           |

| Н   | Н   | х    | inactive           |

X = don't care

#### Bus logic level

Data written into the I/O port from either bus will appear inverted when read from the other bus. Data written into either bus will not be inverted when read from the same bus. (Note. A logic "1" in microcontroller software corresponds to a high level on the UD bus even though the IV bus is inverted). The device wakes up in the unselected state with all data bits latched at the "logic 1" level (UD bus outputs high if enabled).

Input/output control of TV bus

| ME | RĈ | wc | MCLK | ŪĪĈ | function of TV bus |

|----|----|----|------|-----|--------------------|

| L  | L  | L  | Х    | х   | output data        |

| L  | х  | Н  | н    | Н   | input data         |

| L  | Ħ  | L  | х    | х   | inactive           |

| L  | х  | н  | х    | L   | inactive           |

| L  | х  | н  | L    | Н   | įnactive           |

| Н  | Х  | х  | х    | х   | inactive           |

#### TV bus control

Input/output control of the  $\overline{\text{IV}}$  bus is shown above. This bus is controlled by  $\overline{\text{RC}}$ ,  $\overline{\text{WC}}$ ,  $\overline{\text{ME}}$ , and  $\overline{\text{MCLK}}$ . The  $\overline{\text{IV}}$  bus is enabled for output (microcontroller read operation) when  $\overline{\text{ME}}$ , and  $\overline{\text{WC}}$  are all low. Data is written into the data latches from the  $\overline{\text{IV}}$  bus when  $\overline{\text{ME}}$  is low and both  $\overline{\text{WC}}$  and  $\overline{\text{MCLK}}$  are high. To avoid data-input conflicts, inputs from the  $\overline{\text{IV}}$  bus are inhibited when  $\overline{\text{UIC}}$  is low; under all other conditions, the  $\overline{\text{IV}}$  and  $\overline{\text{UD}}$  busses operate independently. The microcontroller left bank ( $\overline{\text{LB}}$ ) and right bank ( $\overline{\text{RB}}$ ) outputs can control the  $\overline{\text{ME}}$  inputs for two banks of  $\overline{\text{I/O}}$  devices, thus acting as a ninth address bit. If more than one  $\overline{\text{I/O}}$  port are to be connected to the same bank ( $\overline{\text{LB}}$  or  $\overline{\text{RB}}$ ) of the microcontroller, selection of each device must be accomplished with external control logic to avoid bus conflicts.

FIGURE 2. Truth tables.

# STANDARDIZED MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                | 5962 | 2-87576 |   |

|------------------|----------------|------|---------|---|

|                  | REVISION LEVEL | -    | SHEET   | 8 |

DESC FORM 193A SEP 87

\$\tau\$. GOVERNMENT PRINTING OFFICE: 1987: -549-096

FIGURE 4. Test loading circuits.

Powered by ICminer.com Electronic-Library Service CopyRight 2003

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 Screening. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 4, 5, and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroups 7 and 8 tests sufficient to verify the truth tables.

- 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> | ▲ 5962- |                |  |       | -87576 |  |

|------------------------------------------------------|------------------|---------|----------------|--|-------|--------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  |         | REVISION LEVEL |  | SHEET | 14     |  |

| T                                                                |                                                          |

|------------------------------------------------------------------|----------------------------------------------------------|

| MIL-STD-883 test requirements                                    | <br>  Subgroups  <br>  (per method  <br>  5005, table I) |

| Interim electrical parameters (method 5004)                      |                                                          |

|                                                                  | 1*,2,3,7,9                                               |

| Group A test requirements<br>  (method 5005)                     | 1,2,3,7,8,9,<br>10,11                                    |

| Groups C and D end-point   electrical parameters   (method 5005) | 1,2,3                                                    |

<sup>\*</sup> PDA applies to subgroup 1.

- 5. PACKAGING

- $5.1\,$  Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

- 6. NOTES

- Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

**STANDARDIZED** MILITARY DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER**

DAYTON, OHIO 45444

SIZE 5962-87576 Α 15 **REVISION LEVEL** SHEET

DESC FORM 193A SEP 87

\$\times\$ U.S. GOVERNMENT PRINTING OFFICE 1987 -549-096

6.4 Approved source of supply. An approved source of supply is listed herein. Additional sources will be added as they become available. The vendor listed herein has agreed to this drawing and a certificate of compliance (see 3.5 herein) has been submitted to DESC-ECS.

|                  | Vendor | Vendor       | Replacement            |

|------------------|--------|--------------|------------------------|

| Military drawing | CAGE   | similar part | military specification |

| part number      | number | number 1/    | part number            |

| 5962-8757601XX   | 18324  | 8X371/BXA    |                        |

$\frac{1}{a}$  Caution. Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

Vendor CAGE number

18324

Vendor name and address

Signetics Corporation 4130 South Market Court Sacramento, CA 95834

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

DESC FORM 193A SEP 87

☆ U.S GOVERNMENT PRINTING OFFICE: 1987--549-096

011929 ---