## 1-W High-Voltage Switchmode Regulator

### **FEATURES**

- CCITT Compatible

- Current-Mode Control

- Low Power Consumption (less than 5 mW)

- 10- to 120-V Input Range

- 200-V, 250-mA MOSFET

- Internal Start-Up Circuit

- SHUTDOWN and RESET

- Maximum Duty Cycle of 99.9%

### **DESCRIPTION**

The Si9108 high-voltage switchmode regulator is a monolithic BiC/DMOS integrated circuit which contains most of the components necessary to implement a high-efficiency dc/dc converter in ISDN terminals up to 3 watts. A 0.5-mA max supply current makes possible the design of a dc/dc converter with 60% efficiency at 25 mW, therefore meeting the recommended performance under the CCITT I.430 specifications.

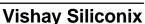

This device may be used with an appropriate transformer to implement isolated flyback power converter topologies to provide single or multiple regulated dc outputs (i.e.,  $\pm 5$  V).

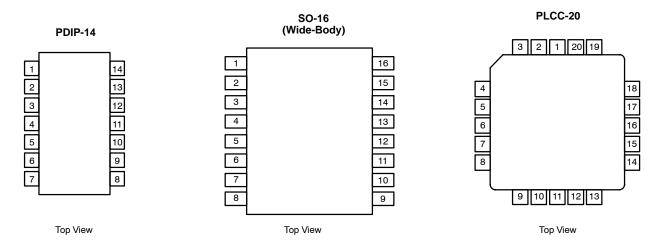

The Si9108 is available in both standard and lead (Pb)-free 16-pin wide-body SOIC, 14-pin plastic DIP and 20-pin PLCC packages which are specified to operate over the industrial temperature range of -40°C to 85°C.

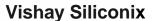

### **FUNCTIONAL BLOCK DIAGRAM**

# **Vāsh'āÿ¹SiPc'onfix**"供应商

### **ABSOLUTE MAXIMUM RATINGS**

| Voltages Referenced to -V <sub>IN</sub> (V <sub>CC</sub> < +V <sub>IN</sub> + 0.3 V)  V <sub>CC</sub>                                                                                                                          | Power Dissipation (Pa<br>14-Pin Plastic DIP (J S<br>16-Pin Plastic Wide-Bo          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| V <sub>DS</sub>                                                                                                                                                                                                                | 20-Pin PLCC (N Suffix                                                               |

| I <sub>D</sub> (Peak) (300 μs pulse, 2% duty cycle)                                                                                                                                                                            | Thermal Impedance (6<br>14-Pin Plastic DIP<br>16-Pin Plastic Wide-Bo<br>20-Pin PLCC |

| HV Pre-Regulator Input Current (continuous)         5 mA           Storage Temperature         -65 to 125°C           Operating Temperature         -40 to 85°C           Junction Temperature (T <sub>J</sub> )         150°C | Notes a. Device mounted v b. Derate 6 mW/°C c. Derate 7.2 mW/° d. Derate 11.2 mW/°  |

| Power Dissipation (Package)a                          |         |

|-------------------------------------------------------|---------|

| 14-Pin Plastic DIP (J Suffix) <sup>b</sup>            | 750 mW  |

| 16-Pin Plastic Wide-Body SOIC (W Suffix) <sup>c</sup> | 900 mW  |

| 20-Pin PLCC (N Suffix) <sup>d</sup>                   | 400 mW  |

| Thermal Impedance (⊖JA)                               |         |

| 14-Pin Plastic DIP                                    | 67° C/W |

| 16-Pin Plastic Wide-Body SOIC                         | 40°C/W  |

| 20-Pin PLCC                                           | 90°C/W  |

|                                                       |         |

- with all leads soldered or welded to PC board. C above 25°C  $^{\circ}\text{C}$  above 25°C

- /°C above 25°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING RANGE**

| Voltages Referenced to -V <sub>IN</sub> |                |

|-----------------------------------------|----------------|

| V <sub>CC</sub>                         | $R_{OSC}$      |

| +V <sub>IN</sub>                        | Linear Inputs  |

| f <sub>OSC</sub>                        | Digital Inputs |

| SPECIFICATIONS <sup>a</sup>          |                   |                                                                                                                                                                                                                                                                 |              |                  |                  |                  |        |

|--------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|------------------|------------------|--------|

|                                      |                   | Test Conditions Unless Otherwise Specified                                                                                                                                                                                                                      | ified Limits |                  |                  |                  |        |

| Parameter                            | Symbol            | $\begin{array}{l} \text{DISCHARGE} = -\text{V}_{\text{IN}} = 0 \text{ V} \\ \text{V}_{\text{CC}} = 10 \text{ V}, +\text{V}_{\text{IN}} = 48 \text{ V} \\ \text{R}_{\text{BIAS}} = 820 \text{ k}\Omega, \text{R}_{\text{OSC}} = 910 \text{ k}\Omega \end{array}$ | Tempb        | Min <sup>c</sup> | Typ <sup>d</sup> | Max <sup>c</sup> | Unit   |

| Reference                            | <u> </u>          |                                                                                                                                                                                                                                                                 |              |                  |                  |                  |        |

| Output Voltage                       | V <sub>R</sub>    | OSC IN = $V_{IN}$ (OSC Disabled)<br>R <sub>L</sub> = 10 M $\Omega$                                                                                                                                                                                              | Room         | 3.92             | 4.00             | 4.08             | ٧      |

| Output Impedancee                    | Z <sub>OUT</sub>  | OSC IN = $-V_{IN}$                                                                                                                                                                                                                                              | Room         | 15               | 300              | 45               | kΩ     |

| Short Circuit Current                | I <sub>SREF</sub> | OSC IN = $-V_{IN}$ , $V_{REF} = -V_{IN}$                                                                                                                                                                                                                        | Room         | 70               | 100              | 130              | μΑ     |

| Temperature Stability <sup>e</sup>   | T <sub>REF</sub>  | OSC IN = -V <sub>IN</sub>                                                                                                                                                                                                                                       | Full         |                  | 0.25             | 1.0              | mV/°C  |

| Long Term Stability <sup>e</sup>     |                   | t = 1000 hrs, T <sub>A</sub> = 125°C                                                                                                                                                                                                                            | Room         |                  | 5.00             | 25.00            | mV     |

| Oscillator                           | · ·               |                                                                                                                                                                                                                                                                 |              | •                | •                |                  |        |

| Maximum Frequencye                   | f <sub>MAX</sub>  | R <sub>OSC</sub> = 0                                                                                                                                                                                                                                            | Room         | 1                | 3                |                  | MHz    |

| Initial Accuracy                     | fosc              | See Note e                                                                                                                                                                                                                                                      | Room         | 32               | 40               | 48               | kHz    |

| Voltage Stability                    | Δf/f              | $\Delta f/f = f (13.5 \text{ V}) - f (9.5 \text{ V})/f (9.5 \text{ V})$                                                                                                                                                                                         | Room         |                  | 10               | 15               | %      |

| Temperature Coefficient <sup>e</sup> | T <sub>OSC</sub>  |                                                                                                                                                                                                                                                                 | Full         |                  | 200              | 500              | ppm/°C |

| Error Amplifier                      | <u> </u>          |                                                                                                                                                                                                                                                                 |              |                  |                  |                  |        |

| Feedback Input Voltage               | V <sub>FB</sub>   | FB Tied to COMP OSC IN = $-V_{IN}$ (OSC Disabled)                                                                                                                                                                                                               | Room         | 3.96             | 4                | 4.04             | V      |

| Input BIAS Current                   | I <sub>FB</sub>   | OSC IN = $-V_{IN}$ , $V_{FB} = 4 V$                                                                                                                                                                                                                             | Room         |                  | 25               | 500              | nA     |

| Open Loop Voltage Gaine              | A <sub>VOL</sub>  | OSC IN = -V <sub>IN</sub> (OSC Disabled)                                                                                                                                                                                                                        | Room         | 60               | 80               |                  | dB     |

| Input Offset Voltage                 | Vos               |                                                                                                                                                                                                                                                                 | Room         |                  | ± 15             | ± 40             | mV     |

| Unity Gain Bandwidthe                | BW                | OSC IN = $-V_{IN}$                                                                                                                                                                                                                                              | Room         | 0.5              | 0.8              |                  | MHz    |

| Dynamic Output Impedance             | Z <sub>OUT</sub>  |                                                                                                                                                                                                                                                                 | Room         |                  | 1                |                  | kΩ     |

| Outrost Coment                       | 1.                | Source (V <sub>FB</sub> = 3.4 V)                                                                                                                                                                                                                                | Room         |                  | -1.2             | -0.32            | 4      |

| Output Current                       | <b>!</b> оит      | Sink (V <sub>FB</sub> = 4.5 V) Room 0                                                                                                                                                                                                                           |              | 0.05             | 05 0.08          |                  | mA     |

| Power Supply Rejection               | PSRR              | $10 \text{ V} \le \text{V}_{CC} \le 13.5 \text{ V}$                                                                                                                                                                                                             | Room         |                  | 70               |                  | dB     |

# Vishay Siliconix

| SPECIFICATIONS <sup>a</sup>                                 |                      |                                                                                                             |        |                  |                  |                  |      |

|-------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------|--------|------------------|------------------|------------------|------|

|                                                             |                      | Test Conditions<br>Unless Otherwise Specified                                                               | Limits |                  |                  |                  |      |

| Parameter                                                   | Symbol               | DISCHARGE = $-V_{IN}$ = 0 V<br>$V_{CC}$ = 10 V, $+V_{IN}$ = 48 V<br>$R_{BIAS}$ = 820 kΩ, $R_{OSC}$ = 910 kΩ | Tempb  | Min <sup>c</sup> | Typ <sup>d</sup> | Max <sup>c</sup> | Unit |

| PWM                                                         |                      | 511.0                                                                                                       | -      |                  |                  |                  |      |

| Maximum Duty Cycle                                          | D <sub>MAX</sub>     |                                                                                                             | Room   | 99.0             | 99.6             | 99.9             | %    |

| Dead Time                                                   |                      |                                                                                                             | Room   |                  | 100              |                  | ns   |

| Minimum Duty Cycle                                          | D <sub>MIN</sub>     |                                                                                                             | Room   |                  |                  | 0                | %    |

| Minimum Pulse Width Before Pulse<br>Drops Out               |                      |                                                                                                             | Room   |                  | 110              | 175              | ns   |

| Current Limit                                               | L L                  |                                                                                                             | _ L    | 1                | 1                | <u> </u>         |      |

| Threshold Voltage                                           | V <sub>SOURCE</sub>  | $R_L$ = 100 $\Omega$ from DRAIN to $V_{CC}$<br>$V_{FB}$ = 0 $V$                                             | Room   | 0.8              | 1.0              | 1.2              | V    |

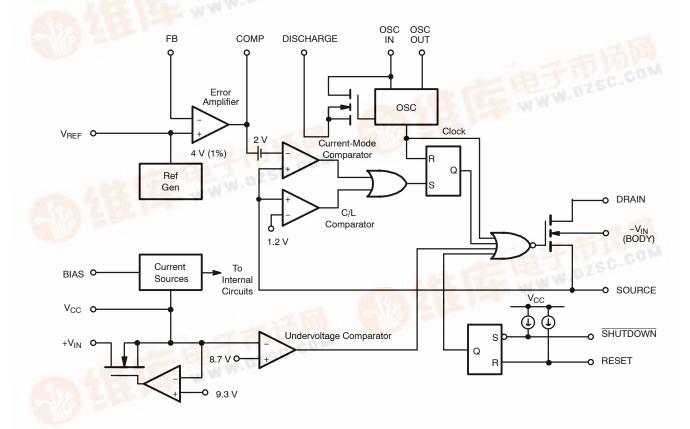

| Delay to Output <sup>e</sup>                                | t <sub>d</sub>       | $R_L$ = 100 $\Omega$ from DRAIN to $V_{CC}$ $V_{SOURCE}$ = 1.5 V, See Figure 1                              | Room   |                  | 200              | 300              | ns   |

| Input Voltage                                               | +V <sub>IN</sub>     | I <sub>IN</sub> = 10 μA                                                                                     | Room   | 120              |                  |                  | V    |

| Input Leakage Current                                       | +I <sub>IN</sub>     | $V_{CC} \ge 10 \text{ V}$                                                                                   | Room   |                  |                  | 10               | μΑ   |

| Pre-Regulator Start-Up Current                              | I <sub>START</sub>   | Pulse Width $\leq$ 300 $\mu$ s, V <sub>CC</sub> = 7 V                                                       | Room   | 8                | 15               |                  | mA   |

| V <sub>CC</sub> Pre-Regulator<br>Turn-Off Threshold Voltage | V <sub>REG</sub>     | I <sub>PRE-REGULATOR</sub> = 10 μA                                                                          | Room   | 7.5              | 9.3              | 9.7              |      |

| Undervoltage Lockout                                        | V <sub>UVLO</sub>    | $R_L$ = 100 $\Omega$ from DRAIN to $V_{CC}$<br>See Detailed Description                                     | Room   | 7.0              | 8.7              | 9.2              | V    |

| V <sub>REG</sub> – V <sub>UVLO</sub>                        | V <sub>DELTA</sub>   |                                                                                                             | Room   | 0.25             | 0.5              |                  |      |

| Supply                                                      |                      |                                                                                                             |        |                  |                  |                  |      |

| Supply Current                                              | Icc                  |                                                                                                             | Room   |                  | 0.35             | 0.5              | mA   |

| Bias Current                                                | I <sub>BIAS</sub>    |                                                                                                             | Room   |                  | 7.5              |                  | μΑ   |

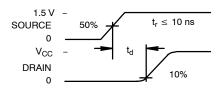

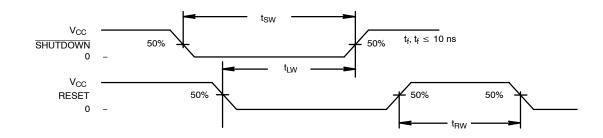

| SHUTDOWN Delay                                              | t <sub>SD</sub>      | V <sub>SOURCE</sub> = -V <sub>IN</sub> , See Figure 2                                                       | Room   |                  | 50               | 100              |      |

| SHUTDOWN Pulse Width                                        | t <sub>SW</sub>      |                                                                                                             | Room   | 50               |                  |                  |      |

| RESET Pulse Width                                           | t <sub>RW</sub>      | See Figure 3                                                                                                | Room   | 50               |                  |                  | ns   |

| Latching Pulse Width SHUTDOWN and RESET Low                 | t <sub>LW</sub>      | g                                                                                                           | Room   | 25               |                  |                  |      |

| Input Low Voltage                                           | V <sub>IL</sub>      |                                                                                                             | Room   |                  |                  | 2.0              | .,   |

| Input High Voltage                                          | V <sub>IH</sub>      | Room 8.0                                                                                                    |        |                  |                  | V                |      |

| Input Current, Input Voltage High                           | I <sub>IH</sub>      | V <sub>IN</sub> = 10 V                                                                                      | Room   |                  | 1                | 5                | A    |

| Input Current, Input Voltage Low                            | I <sub>ΙL</sub>      | V <sub>IN</sub> = 0 V                                                                                       | Room   | -35              | -25              |                  | μΑ   |

| MOSFET Switch                                               |                      |                                                                                                             |        |                  |                  |                  |      |

| Breakdown Voltage                                           | V( <sub>BR)DSS</sub> | I <sub>DRAIN</sub> = 100 μA                                                                                 | Full   | 200              | 220              |                  | V    |

| Drain-Source On Resistance <sup>9</sup>                     | r <sub>DS(on)</sub>  | I <sub>DRAIN</sub> = 100 mA                                                                                 | Room   |                  | 5                | 7                | Ω    |

| Drain Off Leakage Current                                   | I <sub>DSS</sub>     | V <sub>DRAIN</sub> = 100 V                                                                                  | Room   |                  |                  | 10               | μΑ   |

| Drain Capacitance                                           | C <sub>DS</sub>      |                                                                                                             | Room   |                  | 35               |                  | pF   |

- Notes

a. Refer to PROCESS OPTION FLOWCHART for additional information.

b. Room =  $25^{\circ}$ C, Cold and Hot = as determined by the operating temperature suffix.

c. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

d. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

e. Guaranteed by design, not subject to production test.

f.  $C_{STRAY}$  Pin 8 =  $\leq$  5 pF

g. Temperature coefficient of  $r_{DS(on)}$  is 0.75% per  $^{\circ}$ C, typical.

# **Vāšh'āÿ¹Sɨ₽ċ⊘rfix**"供应商

### **TIMING WAVEFORMS**

FIGURE 1.

FIGURE 2.

FIGURE 3.

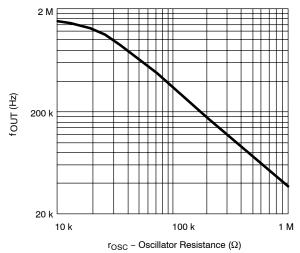

### **TYPICAL CHARACTERISTICS**

### **Output Switching Frequency vs. Oscillator Resistance**

FIGURE 4.

### **PIN CONFIGURATIONS**

| PIN DESCRIPTION    |                    |             |                     |  |  |

|--------------------|--------------------|-------------|---------------------|--|--|

|                    | Pin Number         |             |                     |  |  |

| Function           | 14-Pin Plastic DIP | 16-Pin SOIC | 20-Pin PLCC         |  |  |

| SOURCE             | 4                  | 1           | 7                   |  |  |

| -V <sub>IN</sub>   | 5                  | 2           | 8                   |  |  |

| V <sub>CC</sub>    | 6                  | 4           | 9                   |  |  |

| OSC <sub>OUT</sub> | 7                  | 5           | 10                  |  |  |

| OSC <sub>IN</sub>  | 8                  | 6           | 11                  |  |  |

| DISCHARGE          | 9                  | 7           | 12                  |  |  |

| V <sub>REF</sub>   | 10                 | 8           | 14                  |  |  |

| SHUTDOWN           | 11                 | 9           | 16                  |  |  |

| RESET              | 12                 | 10          | 17                  |  |  |

| COMP               | 13                 | 11          | 18                  |  |  |

| FB                 | 14                 | 12          | 20                  |  |  |

| BIAS               | 1                  | 13          | 2                   |  |  |

| +V <sub>IN</sub>   | 2                  | 14          | 3                   |  |  |

| DRAIN              | 3                  | 16          | 5                   |  |  |

| NC                 |                    | 3, 15       | 1, 4, 6, 13, 15, 19 |  |  |

| ORDERING INFORMATION                  |                                          |              |                      |  |

|---------------------------------------|------------------------------------------|--------------|----------------------|--|

| Standard<br>Part Number               | Lead (Pb)-Free<br>Part Number            | Package      | Temperature<br>Range |  |

| Si9108DJ02                            | Si9108DJ02—E3                            | PDIP-14      |                      |  |

| Si9108DW                              |                                          |              |                      |  |

| Si9108DW-T1<br>(With Tape and Reel)   | Si9108DW-T1—E3<br>(With Tape and Reel)   | SOIC-16 (WB) | –40 to 85 °C         |  |

| Si9108DN02                            |                                          |              |                      |  |

| Si9108DN02-T1<br>(With Tape and Reel) | Si9108DN02-T1—E3<br>(With Tape and Reel) | PLCC-20      |                      |  |

### **Vāsāy¹Si₽doonīx**世应商

### **DETAILED DESCRIPTION**

### Pre-Regulator/Start-Up Section

Due to the low quiescent current requirement of the Si9108 control circuitry, bias power can be supplied from the unregulated input power source, from an external regulated low-voltage supply, or from an auxiliary "bootstrap" winding on the output inductor or transformer.

When power is first applied during start-up,  $+V_{IN}$  will draw a constant current. The magnitude of this current is determined by a high-voltage depletion MOSFET device which is connected between  $+V_{IN}$  and  $V_{CC}$ . This start-up circuitry provides initial power to the IC by charging an external bypass capacitance connected to the  $V_{CC}$  pin. The constant current is disabled when  $V_{CC}$  exceeds 9.3 V. If  $V_{CC}$  is not forced to exceed the 9.3-V threshold, then  $V_{CC}$  will be regulated to a nominal value of 9.3 V by the pre-regulator circuit.

As the supply voltage rises toward the normal operating conditions, an internal undervoltage (UV) lockout circuit keeps the output MOSFET disabled until  $V_{CC}$  exceeds the undervoltage lockout threshold (typically 8.7 V). This guarantees that the control logic will be functioning properly and that sufficient gate drive voltage is available before the MOSFET turns on. The design of the IC is such that the undervoltage lockout threshold will not exceed the pre-regulator turn-off voltage. Power dissipation can be minimized by providing an external power source to  $V_{CC}$  such that the constant current source is always disabled.

### **BIAS**

To properly set the bias for the Si9108, a 820-k $\Omega$  resistor should be tied from BIAS to  $-V_{IN}$ . This determines the magnitude of bias current in all of the analog sections and the pull-up current for the  $\overline{SHUTDOWN}$  and RESET pins. The current flowing in the bias resistor is nominally 7.5  $\mu$ A.

### **Reference Section**

The reference section of the Si9108 consists of a temperature compensated buried zener and trimmable divider network. The output of the reference section is connected internally to the non-inverting input of the error amplifier. Nominal reference output voltage is 4 V. The trimming procedure that is used on the Si9108 brings the output of the error amplifier (which is configured for unity gain during trimming) to within  $\pm\,1\%$  of 4 V. This automatically compensates for the input offset voltage in the error amplifier.

The output impedance of the reference section has been purposely made high so that a low impedance external voltage source can be used to override the internal voltage source, if desired, without otherwise altering the performance of the device.

### **Error Amplifier**

Closed-loop regulation is provided by the error amplifier, whose 1-k $\Omega$  dynamic output impedance enables it to be used with feedback compensation (unlike transconductance amplifiers). A MOS differential input stage provides for low input current. The noninverting input to the error amplifier (V<sub>REF</sub>) is internally connected to the output of the reference supply and should be bypassed with a small capacitor to ground.

### **Oscillator Section**

The oscillator consists of a ring of CMOS inverters, capacitors, and a capacitor discharge switch. Frequency is set by an external resistor between the OSC IN and OSC OUT pins. (See Typical Characteristics graph of resistor value vs. frequency.) The DISCHARGE pin should be tied to  $-V_{\rm IN}$  for normal internal oscillator operation. For 98% duty cycle, the discharge pin must be connected to  $-V_{\rm IN}$  or can be connected to  $-V_{\rm IN}$  through a resistor to set the dead time.

Remote synchronization can be accomplished by capacitive coupling of a synchronization pulse into the OSC IN terminal. For a 5-V pulse amplitude and 0.5- $\mu$ s pulse width, typical values would be 100 pF in series with 3 k $\Omega$  to OSC IN.

### **SHUTDOWN** and RESET

SHUTDOWN and RESET are intended for overriding the output MOSFET switch via external control logic. The two inputs are fed through a latch preceding the output switch. Depending on the logic state of RESET, SHUTDOWN can be either a latched or unlatched input. The output is off whenever SHUTDOWN is low. By simultaneously having SHUTDOWN and RESET low, the latch is set and SHUTDOWN has no effect until RESET goes high. (See the table below.)

**Table 1:** Truth Table for the SHUTDOWN and RESET Pins

| SHUTDOWN | RESET | Output                       |

|----------|-------|------------------------------|

| Н        | Н     | Normal Operation             |

| Н        | 7.    | Normal Operation (No Change) |

| L        | Н     | Off (Not Latched)            |

| L        | L     | Off (Latched)                |

| <b>.</b> | L     | Off (Latched, No Change)     |

When power is first applied during start-up,  $+V_{IN}$  will draw a constant current. The magnitude of this current is determined by a high-voltage depletion MOSFET device which is connected between  $+V_{IN}$  and  $V_{CC}$ . This start-up circuitry provides initial power to the IC by charging an external bypass capacitance connected to the  $V_{CC}$  pin. The constant current is disabled when  $V_{CC}$  exceeds 9.3 V. If  $V_{CC}$  is not forced to exceed the 9.3-V threshold, then  $V_{CC}$  will be regulated to a nominal value of 9.3 V by the pre-regulator circuit.

### **DETAILED DESCRIPTION (CONT'D)**

Both pins have internal current source pull-ups and can be left disconnected when not in use. An added feature of the current sources is the ability to connect a capacitor and an open-collector driver to the SHUTDOWN pin to provide variable shutdown time.

### **Output Switch**

The output switch is a 7- $\Omega$ , 200-V lateral DMOS transistor. Like discrete MOSFETs, the switch contains an intrinsic body-drain diode. However, the body contact in the Si9108 is connected internally to  $-V_{IN}$  and is independent of the SOURCE.

### **APPLICATIONS**

FIGURE 5. CCITT Compatible ISDN Terminal Power Supply

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?70883">http://www.vishay.com/ppg?70883</a>.

Vishay

### **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 Revision: 18-Jul-08