查询"54F547DMQB"供应商

#### 54F/74F547

## Octal Decoder/Demultiplexer with Address Latches and Acknowledge

#### **General Description**

The 'F547 is a 3-to-8 line address decoder with latches for address storage. Designed primarily to simplify multiple chip selection in a microprocessor system, it contains one active LOW and two active HIGH Enables to conserve address space. Also included is an active LOW Acknowledge output that responds to either a Read or Write input signal when the Enables are active.

#### **Features**

- 3-to-8 line address decoder

- Address storage latches

- Multiple enables for address extension

- Open collector acknowledge output

#### Ordering Code: See Section 5

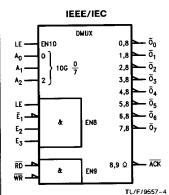

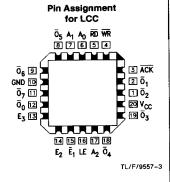

#### **Logic Symbols**

# LE A0 A1 A2

00 01 02 03 04 05 06

TL/F/9557-1

#### **Connection Diagrams**

4-446

#### Unit Loading/Fan Out: See Section 2 for U.L. definitions

|                                                  |                                                | 54               | F/74F                                                                             |

|--------------------------------------------------|------------------------------------------------|------------------|-----------------------------------------------------------------------------------|

| Pin Names                                        | 查询"54F54 <b>759M"以</b> B"供应商                   | U.L.<br>HIGH/LOW | Input I <sub>IH</sub> /I <sub>IL</sub><br>Output I <sub>OH</sub> /I <sub>OL</sub> |

| A <sub>0</sub> -A <sub>2</sub>                   | Address Select Inputs                          | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |

| A <sub>0</sub> −A <sub>2</sub><br>Ē <sub>1</sub> | Chip Enable Input (Active LOW)                 | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |

| E <sub>2</sub> , E <sub>3</sub>                  | Chip Enable Inputs                             | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |

| LE                                               | Latch Enable Input                             | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |

| RD                                               | Read Acknowledge Input (Active LOW)            | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |

| WR                                               | Write Acknowledge Input (Active LOW)           | 1.0/1.0          | 20 μA/ - 0.6 mA                                                                   |

| ACK                                              | Open Collector Acknowledge Output (Active LOW) | *OC/33.3         | *OC/20 mA                                                                         |

| $\overline{O}_0 - \overline{O}_7$                | Decoded Outputs (Active LOW)                   | 50/33.3          | −1 mA/20 mA                                                                       |

<sup>\*</sup>OC = Open Collector

#### **Functional Description**

When enabled, the 'F547 accepts the  $A_0-A_2$  Address inputs and decodes them to select one of eight active LOW, mutually exclusive outputs, as shown in the Decoder Truth Table. With LE HIGH, the Address latches are transparent and the output selection changes each time the  $A_0-A_2$  address changes. When LE is LOW, the latches store the last valid address preceding the HIGH-to-LOW transition of the LE input signal. For applications in which the separation of latch enable and chip enable functions is not required, LE and  $\overline{E}_1$  can be tied together, such that when HIGH the outputs are OFF and the latches are transparent, and when LOW the latches are storing and the selected output is enabled.

The open collector Acknowledge ( $\overline{ACK}$ ) output is normally HIGH (i.e., OFF) and goes LOW when  $\overline{E}_1$ ,  $E_2$  and  $E_3$  are all active and either the Read ( $\overline{RD}$ ) or Write ( $\overline{WR}$ ) input is LOW, as indicated in the Acknowledge Truth Table.

#### **Acknowledge Truth Table**

|    | Inputs         |                |    |    |     |  |  |  |

|----|----------------|----------------|----|----|-----|--|--|--|

| Ē, | E <sub>2</sub> | E <sub>3</sub> | RD | WR | ACK |  |  |  |

| Н  | Х              | X              | Х  | Х  | Н   |  |  |  |

| x  | L              | Х              | X  | Х  | н   |  |  |  |

| x  | Х              | L              | X  | X  | н   |  |  |  |

| L  | Н              | Н              | H  | Н  | Н   |  |  |  |

| L  | Н              | Н              | L  | X  | L   |  |  |  |

| L  | Н              | Н              | X  | L  | L   |  |  |  |

H = HIGH Voltage Level

#### **Latch Status Table**

| Input LE | Latch Status |

|----------|--------------|

| Н        | Transparent  |

| L        | Storing      |

#### **Output Status Table**

|                | Inputs | Decoder |                                  |

|----------------|--------|---------|----------------------------------|

| Ē <sub>1</sub> | Ē₁ E₂  |         | Outputs                          |

| L              | Н      | Н       | $\overline{O}_n = LOW^{\dagger}$ |

| н              | X      | X       | $O_0 - O_7 = HIGH$               |

| ×              | L      | ×       | $O_0 - O_7 = HIGH$               |

| Х              | X      | L       | $O_0 - O_7 = HIGH$               |

<sup>†</sup>See Decoder Truth Table

#### **Decoder Truth Table\***

|                | Inputs         |                |                | Outputs |                |                  |                  |                |                |    |

|----------------|----------------|----------------|----------------|---------|----------------|------------------|------------------|----------------|----------------|----|

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | O <sub>0</sub> | Ō₁      | O <sub>2</sub> | $\overline{O}_3$ | $\overline{O}_4$ | Ō <sub>5</sub> | Ō <sub>6</sub> | 07 |

| L              | L              | L              | L              | Н       | Н              | Н                | Н                | н              | н              | Н  |

| L              | L              | Н              | н              | L       | Н              | Н                | Н                | Н              | Н              | Н  |

| L              | Н              | L              | н              | Н       | L              | Н                | Н                | Н              | Н              | Н  |

| L              | Н              | Н              | н              | Н       | Н              | L                | Н                | н              | Н              | Н  |

| Н              | L              | L              | н              | Н       | Н              | Н                | L                | Н              | Н              | н  |

| н              | L              | н              | н              | Н       | Н              | Н                | н                | L              | Н              | Н  |

| н              | Н              | L              | Н              | Н       | Н              | Н                | Н                | Н              | L              | Н  |

| Н              | Н              | н              | Н              | Н       | н              | Н                | Н                | H              | Н              | L  |

<sup>\*</sup>Assuming E1, LOW; E2 and E3, HIGH

Powered by ICminer.com Electronic-Library Service CopyRight 2003

L = LOW Voltage Level

X = Immaterial

#

#### Absolute Maximum Ratings (Note 1)

if Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distribution of the Maria of the Maria

Storage Temperature 65°C to +150°C

Ambient Temperature under Bias -55°C to +125°C

Junction Temperature under Bias —55°C to +175°C

V<sub>CC</sub> Pin Potential to

Ground Pin -0.5V to +7.0V Input Voltage (Note 2) -0.5V to +7.0V

Input Current (Note 2)

-30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with  $V_{CC} = 0V$ )

Standard Output -0.5V to V<sub>CC</sub>

TRI-STATE® Output -0.5V to +5.5V

Current Applied to Output

in LOW State (Max) twice the rated I<sub>OL</sub> (mA)

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

### Recommended Operating Conditions

Free Air Ambient Temperature

Military

−55°C to +125°C

Commercial

0°C to +70°C

Supply Voltage

Military + 4.5V to + 5.5V Commercial + 4.5V to + 5.5V

#### **DC Electrical Characteristics**

| Combal           | Parameter                                |                                                                              | 54F/74F           |     |             | Units    | Vcc        | Conditions                                                                                                                             |  |

|------------------|------------------------------------------|------------------------------------------------------------------------------|-------------------|-----|-------------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol           |                                          |                                                                              | Min               | Тур | Max         | Oille    | <b>VCC</b> | Conditions                                                                                                                             |  |

| V <sub>IH</sub>  | Input HIGH Voltage                       | ,                                                                            | 2.0               |     |             | ٧        |            | Recognized as a HIGH Signa                                                                                                             |  |

| V <sub>IL</sub>  | Input LOW Voltage                        |                                                                              |                   |     | 0.8         | V        |            | Recognized as a LOW Signal                                                                                                             |  |

| V <sub>CD</sub>  | Input Clamp Diode Vo                     | ltage                                                                        |                   |     | -1.2        | <b>V</b> | Min        | I <sub>IN</sub> = -18 mA                                                                                                               |  |

| V <sub>OH</sub>  | Output HIGH<br>Voltage                   | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub><br>74F 5% V <sub>CC</sub> | 2.5<br>2.5<br>2.7 |     |             | ٧        | Min        | $I_{OH} = -1 \text{ mA } (\overline{O}_n)$<br>$I_{OH} = -1 \text{ mA } (\overline{O}_n)$<br>$I_{OH} = -1 \text{ mA } (\overline{O}_n)$ |  |

| V <sub>OL</sub>  | Output LOW<br>Voltage                    | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub>                           |                   |     | 0.5<br>0.5  | >        | Min        | $I_{OL} = 20 \text{ mA } (\overline{ACK}, \overline{O}_n)$<br>$I_{OL} = 20 \text{ mA } (\overline{ACK}, \overline{O}_n)$               |  |

| lін              | Input HIGH<br>Current                    | 54F<br>7 <b>4</b> F                                                          |                   |     | 20.0<br>5.0 | μΑ       | Max        | V <sub>IN</sub> = 2.7V                                                                                                                 |  |

| l <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test     | 54F<br>74F                                                                   |                   |     | 100<br>7.0  | μΑ       | Max        | V <sub>IN</sub> = 7.0V                                                                                                                 |  |

| I <sub>CEX</sub> | Output HIGH<br>Leakage Current           | 54F<br>74F                                                                   |                   |     | 250<br>50   | μΑ       | Max        | $V_{OUT} = V_{CC}(\overline{O}_n)$                                                                                                     |  |

| V <sub>ID</sub>  | Input Leakage<br>Test                    | 74F                                                                          | 4.75              |     |             | V        | 0.0        | $I_{\text{ID}} = 1.9  \mu\text{A}$ All Other Pins Grounded                                                                             |  |

| l <sub>OD</sub>  | Output Leakage<br>Circuit Current        | 74F                                                                          |                   |     | 3.75        | μΑ       | 0.0        | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded                                                                                   |  |

| I <sub>fL</sub>  | Input LOW Current                        |                                                                              |                   |     | -0.6        | mA       | Max        | V <sub>IN</sub> = 0.5V                                                                                                                 |  |

| los              | Output Short-Circuit (                   | Current                                                                      | -60               |     | -150        | mA       | Max        | $V_{OUT} = 0V(\overline{O}_n)$                                                                                                         |  |

| ОНС              | Open Collector, Outp<br>OFF Leakage Test | ut                                                                           |                   |     | 250         | μΑ       | Min        | $V_{OUT} = V_{CC} (\overline{ACK})$                                                                                                    |  |

| lcc              | Power Supply Curren                      | t                                                                            |                   | 17  | 30          | mA       | Max        |                                                                                                                                        |  |

#### AC Electrical Characteristics: See Section 2 for Waveforms and Load Configurations

|                                      |                                                              |                                                                               | 74F         |                                                                  | 5          | 4F                                                               | 7          | 4F           |             |     |

|--------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|-------------|------------------------------------------------------------------|------------|------------------------------------------------------------------|------------|--------------|-------------|-----|

| 查询<br>Symbol                         | "54F547DMQB"<br>Parameter                                    | 供应商 <sub>A</sub> = +25°C<br>V <sub>CC</sub> = +5.0V<br>C <sub>L</sub> = 50 pF |             | T <sub>A</sub> , V <sub>CC</sub> = Mil<br>C <sub>L</sub> = 50 pF |            | T <sub>A</sub> , V <sub>CC</sub> = Com<br>C <sub>L</sub> = 50 pF |            | Units        | Fig.<br>No. |     |

|                                      |                                                              | Min                                                                           | Тур         | Max                                                              | Min        | Max                                                              | Min        | Max          | ]           |     |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay  An to On                                  | 2.0<br>4.5                                                                    | 7.0<br>9.0  | 9.0<br>12.0                                                      | 3.0<br>5.0 | 10.5<br>13.5                                                     | 1.5<br>4.0 | 10.0<br>13.0 | ns          | 2-3 |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay  E <sub>1</sub> to O <sub>n</sub>          | 2.5<br>3.0                                                                    | 6.5<br>6.5  | 8.5<br>8.5                                                       | 3.0<br>3.5 | 10.0<br>10.0                                                     | 2.0<br>3.0 | 9.5<br>9.5   | ns          | 2-3 |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>LE to $\overline{\mathbb{O}}_n$         | 3.5<br>5.0                                                                    | 7.5<br>14.5 | 10.0<br>14.0                                                     | 4.0<br>5.0 | 11.5<br>20.0                                                     | 3.0<br>5.0 | 11.0<br>15.0 | ns          | 2-3 |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $E_2$ or $E_3$ to $\overline{O}_n$         | 4.0<br>4.0                                                                    | 8.5<br>8.5  | 10.0<br>10.0                                                     | 4.5<br>4.5 | 12.5<br>12.5                                                     | 3.0<br>4.0 | 11.0<br>11.0 | ns          | 2-3 |

| t <sub>PLH</sub>                     | Propagation Delay<br>E <sub>1</sub> , RD or WR to ACK        | 6.5<br>3.5                                                                    | 11.0<br>7.5 | 13.0<br>9.5                                                      | 6.5<br>3.5 | 16.0<br>11.0                                                     | 6.5<br>3.0 | 14.0<br>10.5 | ns          | 2-3 |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>E <sub>2</sub> or E <sub>3</sub> to ACK | 7.5<br>4.5                                                                    | 13.0<br>8.5 | 14.0<br>12.0                                                     | 8.0<br>5.0 | 18.5<br>12.5                                                     | 7.0<br>4.0 | 15.0<br>11.0 | ns          | 2-3 |

#### AC Operating Requirements: See Section 2 for Waveforms

| Symbol             |                         | 74F |                                                              | 54 <b>F</b> |                                         | 74F |                                        |    | Fig. |

|--------------------|-------------------------|-----|--------------------------------------------------------------|-------------|-----------------------------------------|-----|----------------------------------------|----|------|

|                    | Parameter               |     | $T_A = +25^{\circ}C$<br>$V_{CC} = +5.0V$ $T_A, V_{CC} = Mil$ |             | $T_A, V_{CC} = Mil$ $T_A, V_{CC} = Cor$ |     | T <sub>A</sub> , V <sub>CC</sub> = Com |    |      |

|                    |                         | Min | Max                                                          | Min         | Max                                     | Min | Min Max                                |    |      |

| t <sub>s</sub> (H) | Setup Time, HIGH or LOW | 5.0 |                                                              | 5.0         |                                         | 5.0 |                                        |    |      |

| t <sub>s</sub> (L) | A <sub>n</sub> to LE    | 5.0 |                                                              | 5.0         |                                         | 5.0 |                                        | ns | 2-6  |

| t <sub>h</sub> (H) | Hold Time, HIGH or LOW  | 6.0 |                                                              | 6.0         |                                         | 6.0 |                                        |    |      |

| t <sub>h</sub> (L) | A <sub>n</sub> to LE    | 6.0 |                                                              | 6.0         |                                         | 6.0 |                                        |    |      |

| t <sub>w</sub> (H) | LE Pulse Width, HIGH    | 6.0 |                                                              | 6.0         |                                         | 6.0 |                                        | ns | 2-4  |