**Features**

# **Automotive Contact Monitor and Level Shifters with LDO Regulator**

# **General Description**

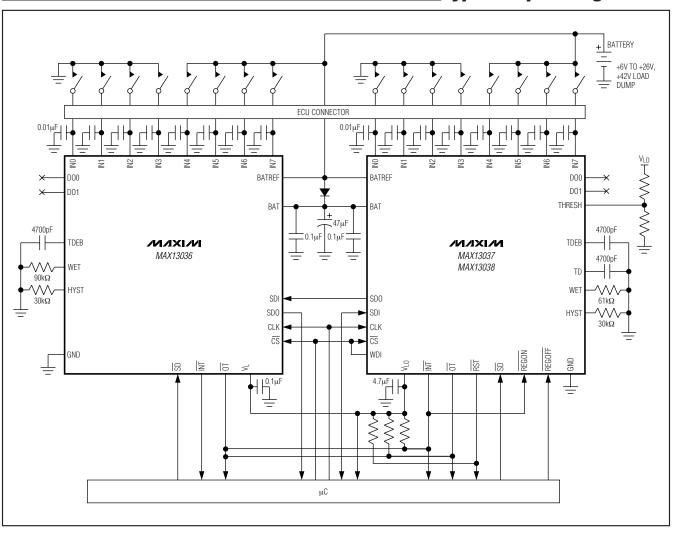

The MAX13037/MAX13038 automotive contact monitor and level shifters monitor and debounce eight remote mechanical switches and assert an interrupt (INT) if a switch changes state. The state of each switch is sampled through an SPI™ interface by reading the status register. Any switch can be prohibited from asserting an interrupt by writing to the command register. Four of the switch inputs are intended for ground-connected switches (IN0-IN3) and the other four inputs (IN4-IN7) are programmable in groups of two for either groundconnected or battery-connected switches. Two switch inputs (INO, IN1) have direct level-shifted outputs (DO0, DO1) to be used for PWM or other timing-based signals.

Switch input thresholds are set to 50% of the voltage applied to BATREF. The threshold hysteresis is set by connecting an external resistor from HYST to ground. The MAX13037/MAX13038 supply an adjustable wetting current to each closed switch to clean mechanical switch contacts that are exposed to adverse conditions.

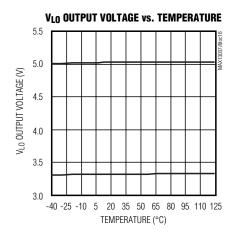

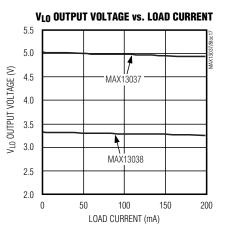

The MAX13037/MAX13038 feature a low dropout (LDO) linear regulator capable of supplying up to 150mA of current. The MAX13037 LDO has an output voltage of +5V, whereas the MAX13038 has an output voltage of +3.3V. The MAX13037/MAX13038 also feature a watchdog timer and an open-drain reset output with adjustable timing.

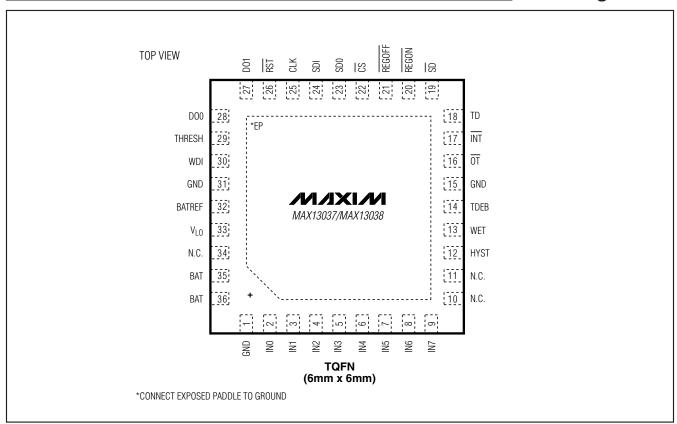

The MAX13037/MAX13038 operate with a +6V to +26Vbattery voltage applied to BAT. The MAX13037/ MAX13038 are available in a 6mm x 6mm, 36-pin TQFN package and operate over the automotive -40°C to +125°C temperature range.

# **Applications**

**Body Computers** Window Lifters Seat Movers Electric Sunroofs Other Control ECUs

SPI is a trademark of Motorola, Inc.

# ♦ +6V to +26V Operating Voltage Range

- ◆ +42V Compatibility on BAT

- ♦ Switch Inputs Withstand Reverse Battery

- 150mA LDO, +5V (MAX13037) or +3.3V (MAX13038)

- ♦ Ultra-Low Operating Current 28µA (typ) in 64ms Scan Mode with LDO ON

- ♦ Resistor Adjustable Switching Hysteresis

- ♦ Watchdog and Reset

- ♦ Built-In Switch Debouncing

- ♦ Immunity to Transients

- ♦ High Modularity

- ♦ Thermal Protection

- ♦ ±8kV HBM ESD Protection on IN0–IN7 Without **External Components**

- ♦ Two Inputs (IN0, IN1) Programmable as Direct Outputs

- ♦ Four Inputs (IN4–IN7) Programmable for BAT or **GND Related Switches** WWW.DZSC

# **Ordering Information**

| PART                 | LDO<br>OUTPUT<br>VOLTAGE | TEMP<br>RANGE      | PIN-<br>PACKAGE               | PKG<br>CODE |

|----------------------|--------------------------|--------------------|-------------------------------|-------------|

| <b>MAX13037</b> ATX+ | +5V                      | -40°C to<br>+125°C | 36 TQFN-EP*<br>(6mm x<br>6mm) | T3666-3     |

| MAX13038ATX+         | +3.3V                    | -40°C to<br>+125°C | 36 TQFN-EP*<br>(6mm x<br>6mm) | T3666-3     |

<sup>+</sup>Denotes a lead-free package.

Pin Configuration and Typical Application Circuit at end of data sheet.

N/IXI/N

df.dzsc.com

<sup>\*</sup>EP = Exposed paddle.

### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND, unless otherwise noted.)

| V <sub>LO</sub> 0.3V to +6.0V                         |

|-------------------------------------------------------|

| BAT0.3V to +42V                                       |

| IN_ , BATREF45V to +45V                               |

| IN_ to BAT45V to +45V                                 |

| SD, REGON0.3V to +45V                                 |

| HYST, WET, TD, TDEB, THRESH, OT, INT, RST0.3V to 6.0V |

| CS, CLK, SDI, SDO, WDI,                               |

| DO0, DO1, REGOFF0.3V to (V <sub>LO</sub> + 0.3V)      |

| Continuous Current (CS, CLK, SDI, SDO, WDI, DOO,      |

| DO1, REGOFF)±20mA                                     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )              |

|--------------------------------------------------------------------|

| 36-Pin TQFN (derate 35.7mW/°C above +70°C)2857mW                   |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) (Note 1)    |

| 36-Pin TQFN 1.4°C/W                                                |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) (Note 1) |

| 36-Pin TQFN                                                        |

| Operating Temperature Range40°C to +125°C                          |

| Junction Temperature+150°C                                         |

| Storage Temperature Range65°C to +150°C                            |

| Lead Temperature (soldering, 10s)+300°C                            |

|                                                                    |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal considerations see <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(BAT = +6V to +26V, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at BAT = +14V, T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                             | SYMBOL                | CONDITIONS                                                                                                                                                         | N | ΛIN | TYP | MAX    | UNITS |

|-------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|--------|-------|

| POWER SUPPLY                                          | •                     |                                                                                                                                                                    |   |     |     |        | •     |

| BAT Supply Range                                      | V <sub>BAT</sub>      |                                                                                                                                                                    |   | 6   |     | 26     | V     |

| BAT Supply Current with<br>Regulator On               | ISUP_REG              | $V_{BAT}$ = +14V, continuous scan (SC: SC1 = 1, SC0 = 0), programmable hysteresis off (M0 = M1 = 1), IN0-IN7 = unconnected, regulator of (REGON = REGOFF = GND).   |   |     | 57  | 110    | μА    |

| BAT Supply Current with Regulator Off                 | I <sub>SUP</sub>      | $V_{BAT}$ = +14V, continuous scan (SC) SC1 = 1, SC0 = 0), programmable hysteresis off (M0 = M1 = 1), IN0-IN7 = unconnected, regulator (REGON = BAT, REGOFF = GND). |   |     | 46  | 80     | μА    |

| BAT Supply Current in Scan<br>Mode with Regulator On  | ISCAN_REG             | $V_{BAT}$ = +14V, scan mode (SC0 = 0, SC1 = 0, SC2 = 0), regulator on (REGON = REGOFF = GND).                                                                      | , |     | 28  | 48     | μA    |

| BAT Supply Current in Scan<br>Mode with Regulator Off | ISCAN                 | $V_{BAT}$ = +14V, scan mode (SC0 = 0, SC1 = 0, SC2 = 0), regulator off ( $\overline{REGON}$ = BAT, $\overline{REGOFF}$ = GND).                                     | , |     | 17  | 35     | μΑ    |

| BAT Supply Current in Shutdown Mode                   | I <sub>SHDN</sub>     | $V\overline{SD} = 0V$ , $VBAT = +14V$ , $TA = +2$<br>$\overline{REGON} = BAT$ $T_A = +1$                                                                           |   |     | 3   | 5<br>7 | μΑ    |

| BATREF Input Resistance                               | RBATREF               | VBATREF = +14V                                                                                                                                                     |   | 1   | 2.7 |        | МΩ    |

| BATREF Input Leakage Current in Shutdown              | I <sub>L_BATREF</sub> | VSD = 0V, VBATREF = +14V                                                                                                                                           |   |     |     | 1      | μΑ    |

MIXIN \_\_\_\_\_\_

# **ELECTRICAL CHARACTERISTICS (continued)**

$(BAT = +6V \text{ to } +26V, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at BAT = +14V, } T_A = +25^{\circ}\text{C.})$  (Note 2)

| PARAMETER                                            | SYMBOL                          | CONDITIO                                                                                                                         | MIN            | TYP                   | MAX                            | UNITS                          |     |  |

|------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|--------------------------------|--------------------------------|-----|--|

| SWITCH INPUTS (IN0-IN7)                              | ı                               | 1                                                                                                                                |                | <b></b>               |                                |                                |     |  |

| Input Voltage Threshold Center                       | VTILO                           | R <sub>HYST</sub> = ∞ or programma disabled                                                                                      | ble hysteresis | 0.425 x<br>VBATREF    | 0.5 x<br>VBATREF               | 0.575 x<br>V <sub>BATREF</sub> | V   |  |

| (Note 3)                                             | VTH_C                           | $R_{HYST} = 90k\Omega$                                                                                                           |                | 0.4 x<br>VBATREF      | 0.5 x<br>V <sub>BATREF</sub>   | 0.63 x<br>VBATREF              |     |  |

|                                                      |                                 | R <sub>HYST</sub> = ∞ or programma disabled                                                                                      | ble hysteresis |                       | 0.166 x<br>V <sub>BATREF</sub> | 0.22 x<br>VBATREF              |     |  |

| Input Voltage Threshold<br>Hysteresis (Note 4)       | V <sub>TH_H</sub> ys            | $R_{HYST} = 90k\Omega$                                                                                                           |                | 0. 26 x<br>VBATREF    |                                | 0. 48 x<br>VBATREF             | V   |  |

|                                                      |                                 | $R_{HYST} = 0\Omega$                                                                                                             |                |                       | 0.5 x<br>VBATREF               |                                |     |  |

| Switch-State Sense Resistor                          | RSENSE                          |                                                                                                                                  |                |                       |                                |                                | kΩ  |  |

| Wetting Current Rise/Fall Time                       | IWET_RISE_                      | $R_{WET} = 61k\Omega$                                                                                                            | Rise           |                       | 6                              |                                | 110 |  |

| (Note 5)                                             | FALL                            | UMF1 = 01K75                                                                                                                     | Fall           |                       | 1                              |                                | μs  |  |

|                                                      |                                 | $R_{WET} = 61k\Omega$                                                                                                            |                |                       | 22                             |                                |     |  |

| Wetting Current                                      | IWET                            | $R_{WET} = 30k\Omega$                                                                                                            |                | 28                    | 40                             | 51                             | mA  |  |

|                                                      |                                 | $R_{WET} = 330 k\Omega$                                                                                                          |                | 7.5                   |                                |                                |     |  |

| IN0-IN7 Input Impedance in Shutdown                  |                                 | $V_{\overline{SD}} = 0V$ , $V_{IN} = +14V$                                                                                       | 5.5            | 8.5                   |                                | МΩ                             |     |  |

| ESD Protection IN0-IN7                               |                                 | Human Body Model (HBN                                                                                                            | 1)             |                       | 8                              |                                | kV  |  |

| LOGIC-LEVELS ( $\overline{\text{CS}}$ , CLK, SDI , S | DI, DO0, DO                     | 1, $\overline{\text{INT}}$ , $\overline{\text{OT}}$ , $\overline{\text{RST}}$ , $\overline{\text{SD}}$ , $\overline{\text{REG}}$ | ON, REGOFF)    |                       |                                |                                |     |  |

| SDO, DO1, DO2<br>Output Voltage High                 | Voн                             | Source current = 2mA                                                                                                             |                | 0.8 x V <sub>L</sub>  | 0                              |                                | V   |  |

| SDO, DO1, DO2<br>Output Voltage Low                  | V <sub>OL</sub>                 | Sink current = 4mA                                                                                                               |                |                       | (                              | 0.2 x V <sub>LO</sub>          | V   |  |

| ĪNT, ŌT, RST Output Voltage Low                      | VINTL                           | Sink current = 4mA                                                                                                               |                |                       |                                | 0.4                            | V   |  |

| SD Input Leakage Current                             | IL_SD                           | $V_{\overline{SD}} = V_{BAT} = +14V$                                                                                             |                |                       |                                | 1                              | μΑ  |  |

| SD, REGON Input Voltage Low                          | V <sub>IL_SD</sub>              |                                                                                                                                  |                |                       |                                | 0.8                            | V   |  |

| SD, REGON Input Voltage High                         | V <sub>IH</sub> _ <del>SD</del> |                                                                                                                                  |                | 2.4                   |                                |                                | V   |  |

| REGON Pullup Current                                 | IREGON                          | REGON = 0                                                                                                                        |                | 0.4                   | 1                              | 3.0                            | μΑ  |  |

| CS, CLK, SDI, REGOFF, WDI<br>Input Voltage Low       | VIL                             |                                                                                                                                  |                |                       | C                              | .33 x V <sub>LO</sub>          | V   |  |

| CS, CLK, SDI, REGOFF, WDI<br>Input Voltage High      | VIH                             |                                                                                                                                  |                | 0.66 x V <sub>I</sub> | _0                             |                                | V   |  |

| CS, CLK, WDI, REGOFF Input<br>Leakage Current        | I <sub>IL</sub>                 |                                                                                                                                  |                | -1                    |                                | +1                             | μΑ  |  |

| INT, OT, RST Leakage Current                         | loL                             |                                                                                                                                  |                | -1                    |                                | +1                             | μΑ  |  |

| SDI Pulldown Resistor                                | R <sub>SDI</sub>                |                                                                                                                                  |                | 65                    | 100                            | 145                            | kΩ  |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(BAT = +6V \text{ to } +26V, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at BAT = +14V, } T_A = +25^{\circ}\text{C.})$  (Note 2)

| PARAMETER                                              | SYMBOL           | CONDITIO                                                                 | ONS                         | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------------------------|------------------|--------------------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|

| LINEAR REGULATOR                                       | •                |                                                                          |                             |       |       |       | •     |

| Outrout Valtage                                        | \/               | MAX13037, $V_{BAT} = +14V$                                               | , I <sub>LOAD</sub> = 1mA   | 4.92  | 5.00  | 5.08  | V     |

| Output Voltage                                         | V <sub>LO</sub>  | MAX13038, $V_{BAT} = +14V$                                               | , I <sub>LOAD</sub> = 1mA   | 3.234 | 3.300 | 3.366 | V     |

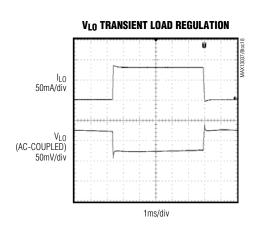

|                                                        |                  | $I_{LOAD} = 1 \text{mA to } 50 \text{mA},$                               | $V_{LO} = +5V$ (MAX13037)   |       | 0.53  | 1     |       |

| Load Deputation                                        | LOAD DEC         | V <sub>BAT</sub> = +14V                                                  | $V_{LO} = +3.3V$ (MAX13038) |       | 0.53  | 1     |       |

| Load Regulation                                        | LOAD_REG         | $I_{LOAD} = 1$ mA to 150mA,                                              | $V_{LO} = +5V$ (MAX13037)   |       | 1     | 1.85  | %     |

|                                                        |                  | $V_{BAT} = +14V$                                                         | $V_{LO} = +3.3V$ (MAX13038) |       | 1     | 1.85  | ı     |

| Line Regulation                                        | LINE_REG         | $V_{BAT} = +6V \text{ to } +26V$                                         | •                           | -0.9  |       | +0.9  | mV/V  |

|                                                        |                  | $V_{LO} = +5V$ , $I_{LO} = 50$ mA (                                      |                             |       | 330   |       |       |

| Dropout Voltage                                        | VDROP            | $V_{LO} = +5V$ , $I_{LO} = 150$ mA                                       | (MAX13037)                  |       |       | 1000  | mV    |

|                                                        |                  | $V_{LO} = +3.3V$ , $I_{LO} = 150m$                                       | A (MAX13038)                |       |       | 1300  |       |

| Output Current Limit                                   | I <sub>LIM</sub> | $V_{BAT} = +14V$                                                         |                             | 150   |       |       | mA    |

| Power-Supply Rejection Ratio                           | PSRR             | I <sub>LO</sub> = 10mA, f = 100Hz, 5<br>AC-coupled into V <sub>BAT</sub> | 00mV <sub>P-P</sub> ,       |       | 68    |       | dB    |

| Start-Up Time                                          | tstart           |                                                                          |                             |       | 1     |       | ms    |

| RESET, WATCHDOG                                        |                  |                                                                          |                             |       |       |       |       |

| Reset Reference Voltage                                | V <sub>RST</sub> | THRESH from high to low                                                  |                             | 1.20  | 1.24  | 1.28  | V     |

| THERMAL SHUTDOWN                                       |                  |                                                                          |                             |       |       |       |       |

| Thermal Shutdown Temperature                           | TSHDN            | (Note 6)                                                                 |                             |       | 165   |       | °C    |

| Thermal Shutdown Temperature for Wetting Currents Only | Twarn            | (Note 7)                                                                 |                             |       | 135   |       | °C    |

| Thermal Shutdown Hysteresis                            | THYST            |                                                                          |                             |       | 15    |       | °C    |

# **TIMING CHARACTERISTICS**

$(BAT = +6V \text{ to } +26V, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at BAT = +14V, } T_A = +25^{\circ}\text{C.})$  (Note 2)

| PARAMETER                                                                        | SYMBOL | CONDITIONS                           | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------------------------|--------|--------------------------------------|-----|-----|-----|-------|

| IN0 to DO0 Propagation Delay,                                                    | topon  | $V_{BAT} = +6V$                      |     | 22  | 35  | 0     |

| IN1 to DO1 Propagation Delay                                                     | tprop  | $V_{BAT} = +14V$                     |     | 22  |     | μs    |

| CLK Frequency                                                                    | fCLK   | Input rise/fall time < 2ns           |     |     | 5   | MHz   |

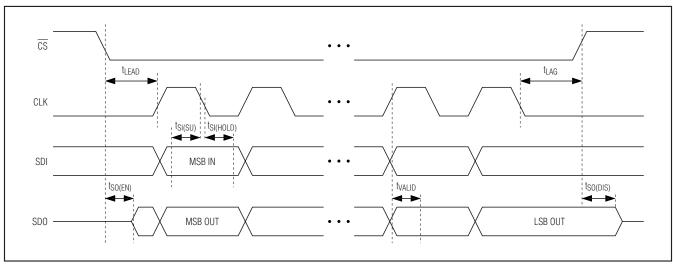

| Falling Edge of $\overline{\text{CS}}$ to Rising Edge of CLK Required Setup Time | †LEAD  | Input rise/fall time < 2ns, Figure 1 | 110 |     |     | ns    |

| Falling Edge of CLK to Rising Edge of CS Required Setup Time                     | tLAG   | Input rise/fall time < 2ns, Figure 1 | 50  |     |     | ns    |

! \_\_\_\_\_\_ /V/XI/N

# **TIMING CHARACTERISTICS (continued)**

(BAT = +6V to +26V, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at BAT = +14V, T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                                             | SYMBOL                | CONDITIONS                                                                      | MIN                  | TYP | MAX  | UNITS |

|-----------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------|----------------------|-----|------|-------|

| SDI to Falling Edge of CLK<br>Required Setup Time                     | tsi(su)               | Input rise/fall time < 2ns, Figure 1                                            | 30                   |     |      | ns    |

| Falling Edge of CLK to SDI<br>Required Hold Time                      | <sup>t</sup> SI(HOLD) | Input rise/fall time < 2ns, Figure 1                                            | 20                   |     |      | ns    |

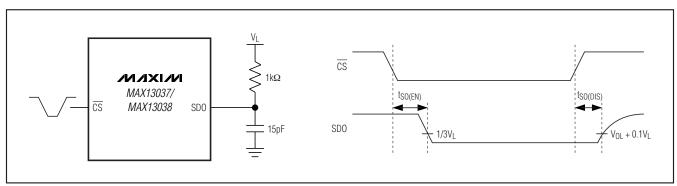

| Time from Falling Edge of $\overline{\text{CS}}$ to SDO Low Impedance | tso(EN)               | Input rise/fall time < 2ns, Figure 1                                            |                      |     | 55   | ns    |

| Time from Rising Edge of $\overline{CS}$ to SDO High Impedance        | tso(DIS)              | Figures 1 and 2                                                                 |                      |     | 55   | ns    |

| Time from Rising Edge of CLK to SDO Data Valid                        | tvalid                | C <sub>SDO</sub> =15pF, Figure 1                                                |                      |     | 70   | ms    |

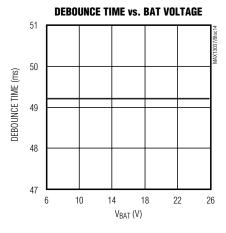

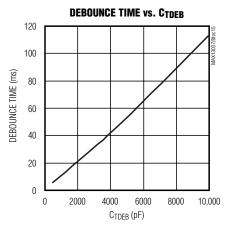

| Debounce Time                                                         | to.=0                 | C <sub>TDEB</sub> = 500pF                                                       | 3.18                 | 5.9 | 9.42 | ms    |

| Debourice Time                                                        | tDEB                  | C <sub>TDEB</sub> = 10nF                                                        | 63                   | 120 | 188  | ms    |

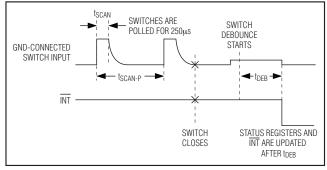

| Scanning Time Pulse                                                   | tscan                 |                                                                                 | 130                  | 250 | 400  | μs    |

| Scanning Time Period                                                  | tscan-p               | SC0 = 0, SC1 = 1, SC2 = 1                                                       | 4                    | 8   | 14   | ms    |

| Wetting Time Pulse                                                    | twett                 | WTOFF = 0                                                                       | 10                   | 21  | 35   | ms    |

| Time from Shutdown to Normal Operation                                | tsD                   | SD low-to-high transition to input monitoring enabled                           |                      | 200 |      | μs    |

| Time from SCAN Mode to Normal Operation                               | tsM                   | (Note 8)                                                                        |                      | 500 |      | μs    |

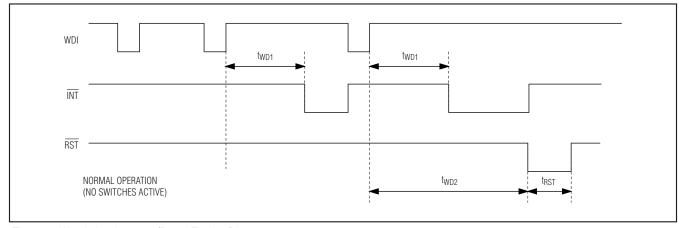

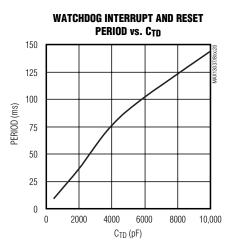

| Reset Output Pulse Width                                              | t <sub>RST</sub>      | C <sub>TD</sub> = 10nF (Figure 3)                                               | 10                   | 21  | 36   | ms    |

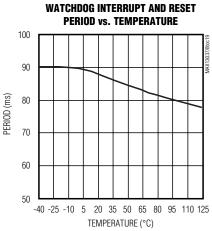

| Watchdog Timeout Period 1                                             | t <sub>WD1</sub>      | C <sub>TD</sub> = 10nF, time before $\overline{\text{INT}}$ goes low (Figure 3) | 40                   | 84  | 144  | ms    |

| Watchdog Timeout Period 2                                             | t <sub>WD2</sub>      | C <sub>TD</sub> = 10nF, time before RST goes low (Figure 3)                     | 2 × t <sub>WD1</sub> |     |      | ms    |

| Minimum Watchdog Timeout<br>Reset on WDI                              | t <sub>WDI</sub>      |                                                                                 | 300                  |     |      | ns    |

- **Note 2:** All units are 100% production tested at T<sub>A</sub> = 125°C. Limits over the operating temperature range are guaranteed by design and not production tested.

- Note 3:  $VTH_C = (VTH_HIGH + VTH_LOW) / 2$ .

- Note 4: VTH\_HYS = (VTH\_HIGH VTH\_LOW).

- Note 5: Wetting current rise/fall time is measured as the time it takes to go from 20% to 80% of the maximum wetting current.

- Note 6: TSHDN is the temperature at which the wetting currents and LDO are disabled.

- **Note 7:** TWARN is the temperature at which only the wetting currents are disabled.

- Note 8: When exiting SCAN mode to enter Normal Mode (through SPI) any input change is ignored for 500µs (typ) to allow correct wake-up of input comparators. After this time elapses, the inputs are monitored in continuous mode.

Figure 1. SPI Timing Characteristics

Figure 2. SDO Enable/Disable Test Circuit and Timing Diagram

Figure 3. Watchdog Interrupt/Reset Timing Diagram

6 \_\_\_\_\_\_ /N/XI/M

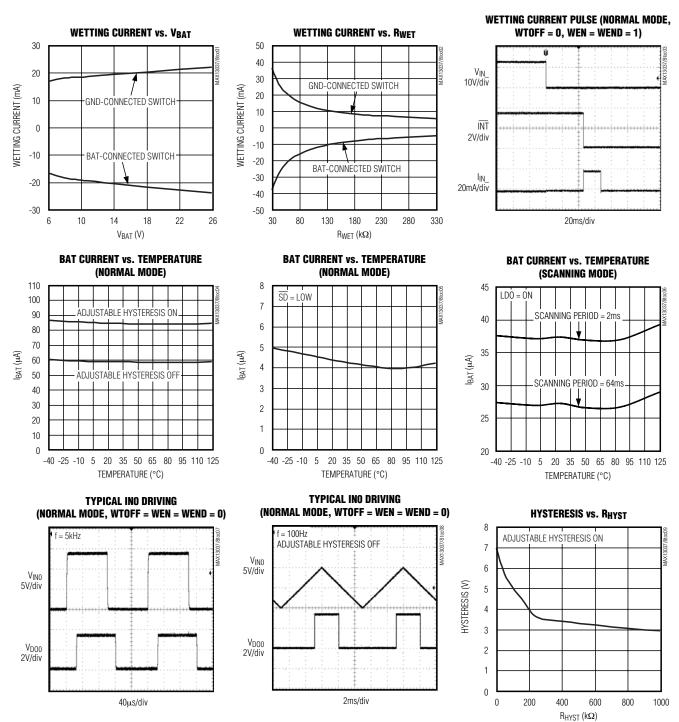

# **Typical Operating Characteristics**

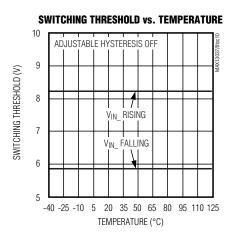

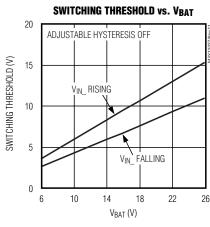

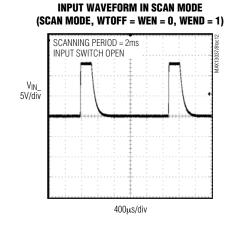

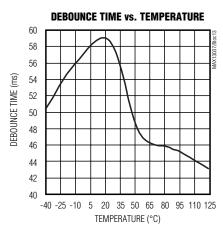

$(BAT = +14V, \overline{SD} = V_{BAT}, R_{WET} = 61k\Omega, R_{HYST} = 90k\Omega, C_{TDEB} = 4700pF, C_{TD} = 4700pF, T_{A} = +25^{\circ}C, unless otherwise noted.)$

# Typical Operating Characteristics (continued)

$(BAT = +14V, \overline{SD} = V_{BAT}, R_{WET} = 61k\Omega, R_{HYST} = 90k\Omega, C_{TDEB} = 4700pF, C_{TD} = 4700pF, T_{A} = +25^{\circ}C, unless otherwise noted.)$

· \_\_\_\_\_

# Typical Operating Characteristics (continued)

$(BAT = +14V, \overline{SD} = V_{BAT}, R_{WET} = 61k\Omega, R_{HYST} = 90k\Omega, C_{TDEB} = 4700pF, C_{TD} = 4700pF, T_{A} = +25^{\circ}C, unless otherwise noted.)$

# **Pin Description**

| PIN        | NAME | FUNCTION                                                                                                                                                                                                  |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 15, 31  | GND  | Ground                                                                                                                                                                                                    |

| 2          | INO  | Switch Input Channel 0. Connect IN0 to a switch connected to GND. IN0 can be programmed as a direct input with a level-shifted output on DO0 (see the <i>Mechanical Switch Inputs (IN0–IN7)</i> section). |

| 3          | IN1  | Switch Input Channel 1. Connect IN1 to a switch connected to GND. IN1 can be programmed as a direct input with a level-shifted output on DO1 (see the <i>Mechanical Switch Inputs (IN0–IN7)</i> section). |

| 4          | IN2  | Switch Input Channel 2. Connect IN2 to a switch connected to GND.                                                                                                                                         |

| 5          | IN3  | Switch Input Channel 3. Connect IN3 to a switch connected to GND.                                                                                                                                         |

| 6          | IN4  | Switch Input Channel 4. Connect IN4 to a switch connected to GND or BAT.                                                                                                                                  |

| 7          | IN5  | Switch Input Channel 5. Connect IN5 to a switch connected to GND or BAT.                                                                                                                                  |

| 8          | IN6  | Switch Input Channel 6. Connect IN6 to a switch connected to GND or BAT.                                                                                                                                  |

| 9          | IN7  | Switch Input Channel 7. Connect IN7 to a switch connected to GND or BAT.                                                                                                                                  |

| 10, 11, 34 | N.C. | No Connection. Not internally connected.                                                                                                                                                                  |

| 12         | HYST | Hysteresis Input. Connect HYST to GND with a $0\Omega$ to $900k\Omega$ resistor to set the input voltage hysteresis on IN0–IN7.                                                                           |

| 13         | WET  | Wetting Current Input. Connect a $30k\Omega$ to $330k\Omega$ resistor from WET to GND to set the wetting current on IN0–IN7.                                                                              |

| 14         | TDEB | Switch Debounce Time Input. Connect a 500pF to 10nF capacitor from TDEB to GND to set the switch debounce time.                                                                                           |

| 16         | ŌT   | Overtemperature Warning Output. $\overline{\text{OT}}$ is an open-drain output that asserts low when the thermal warning threshold is exceeded.                                                           |

| 17         | ĪNT  | Interrupt Output. INT is an open-drain output that asserts low when one or more of the IN0–IN7 inputs change state and are enabled for interrupts or when the watchdog times out.                         |

| 18         | TD   | Reset and Watchdog Timeout Input. Connect TD to GND with a 500pF to 10nF capacitor to set the timeout period for the reset and watchdog.                                                                  |

# **Pin Description (continued)**

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                            |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN    | NAME            |                                                                                                                                                                                                                                                                                                                     |

| 19     | SD              | Shutdown Input. Drive $\overline{SD}$ low to place the MAX13037/MAX13038 into shutdown mode and disable the linear regulator. Drive $\overline{SD}$ high for normal operation. $\overline{SD}$ is compatible with voltages up to V <sub>BAT</sub> .                                                                 |

| 20     | REGON           | Linear Regulator Enable Input (Active Low). Connect REGON to INT to enable a wake-up when a switch status change is detected. Drive REGON using an open-drain logic output to control the regulator directly. REGON is internally pulled up to an internal bias voltage of approximately +4.8V.                     |

| 21     | REGOFF          | Linear Regulator Disable Input (Active Low). $\overline{\text{REGOFF}}$ is used in conjunction with $\overline{\text{REGON}}$ when the internal regulator is enabled by an interrupt (see the <i>Low-Dropout Linear Regulator (VLO)</i> section).                                                                   |

| 22     | CS              | SPI Chip-Select Input. Drive $\overline{\text{CS}}$ low to enable the clocking of data into and out of the MAX13037/MAX13038. SPI data is latched into the MAX13037/MAX13038 on the rising edge of $\overline{\text{CS}}$ .                                                                                         |

| 23     | SDO             | SPI Serial-Data Output. SPI data is output on SDO on the rising edges of CLK while $\overline{\text{CS}}$ is held low. SDO is three-state when $\overline{\text{CS}}$ is high.                                                                                                                                      |

| 24     | SDI             | SPI Serial-Data Input. SPI data is latched into the internal shift register on the falling edges of CLK while $\overline{\text{CS}}$ is held low. SDI has an internal 100k $\Omega$ pulldown resistor.                                                                                                              |

| 25     | CLK             | SPI Serial-Clock Input                                                                                                                                                                                                                                                                                              |

| 26     | RST             | Reset Output. $\overline{\text{RST}}$ is an open-drain output that asserts low when V <sub>LO</sub> is below the threshold determined by the THRESH input. $\overline{\text{RST}}$ also asserts low when the watchdog times out.                                                                                    |

| 27     | DO1             | Data Output Channel 1. DO1 is the level-shifted output of IN1 when WEND = 0.                                                                                                                                                                                                                                        |

| 28     | DO0             | Data Output Channel 0. DO0 is the level-shifted output of IN0 when WEND = 0.                                                                                                                                                                                                                                        |

| 29     | THRESH          | Reset Threshold Level Input. Connect THRESH to a resistor divider between V <sub>LO</sub> and GND to set the reset reference level.                                                                                                                                                                                 |

| 30     | WDI             | Watchdog Timer Input. The watchdog timer is reset at every transition on the WDI input.                                                                                                                                                                                                                             |

| 32     | BATREF          | Battery Reference Input. Switch thresholds are set to 50% of the voltage applied to BATREF. Connect BATREF to the system's battery supply voltage.                                                                                                                                                                  |

| 33     | V <sub>LO</sub> | Linear Regulator Output. $V_{LO}$ is the output of an internal linear regulator and is the reference voltage for all digital I/O. Bypass $V_{LO}$ with a 2.2 $\mu$ F or greater ceramic capacitor. Alternatively, a 10 $\mu$ F electrolytic capacitor can be used in parallel with a 0.1 $\mu$ F ceramic capacitor. |

| 35, 36 | BAT             | Battery Supply Input. Connect BAT to a positive +6V to +26V battery supply voltage. Bypass BAT to ground with a 0.1µF ceramic capacitor and a 10µF electrolytic capacitor placed as close as possible to BAT.                                                                                                       |

| _      | EP              | Exposed Paddle. Connect EP to GND.                                                                                                                                                                                                                                                                                  |

|        | 1               |                                                                                                                                                                                                                                                                                                                     |

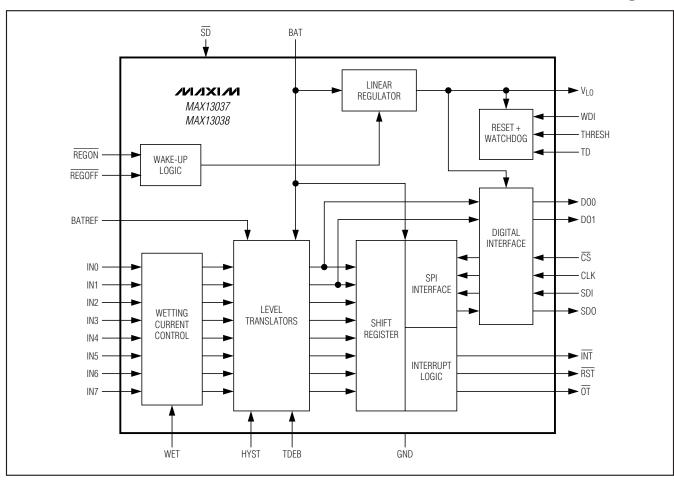

# **Functional Diagram**

# **Detailed Description**

The MAX13037/MAX13038 automotive contact monitor and level shifters monitor and debounce eight remote mechanical switches and assert an interrupt (INT) if a switch changes state. Any of the switch inputs can be prohibited from asserting an interrupt. The switch threshold levels are set to 50% of the voltage applied to BATREF and all switch inputs feature a common adjustable hysteresis, debounce time, and wetting current. Two switch inputs (INO, IN1) are programmable to have direct outputs (DO0, DO1), useable for PWM or other timing-based signals.

The MAX13037/MAX13038 feature an SPI interface to monitor individual switch inputs and to configure interrupt masking, hysteresis, and wetting current enable/disable, switch configuration (battery-connected or ground-connected), and scanning period.

The MAX13037/MAX13038 provide an internal low dropout (LDO) linear regulator capable of supplying up to 150mA. The LDO can be enabled or disabled through two digital control inputs: REGON and REGOFF. A watchdog timer and power-on reset circuitry is provided on the MAX13037/MAX13038 to supervise external microcontrollers (µC).

The MAX13037/MAX13038 feature three modes of operation: normal mode, scanning mode, and shutdown mode. In normal mode, the part is fully functional and internal sensing resistors are connected to all switch inputs. In scanning mode, the sensing resistors are connected for a finite duration to reduce power consumption. In shutdown mode, all switch inputs are high impedance and the internal LDO is switched off to further reduce power consumption.

#### **BAT**

BAT is the main power-supply input. Bypass BAT to ground with a  $0.1\mu F$  ceramic capacitor placed as close as possible to BAT. In addition, bypass BAT with a  $10\mu F$  or greater capacitor. BAT can withstand DC voltages up to +42V.

### Low-Dropout Linear Regulator (VLO)

The MAX13037/MAX13038 contain an internal LDO linear regulator supplied by the BAT input. The LDO output voltage is present on  $V_{LO}$  and is capable of supplying up to 150mA of current. The MAX13037 output voltage is set to +5V and the MAX13038 output voltage is set to +3.3V.

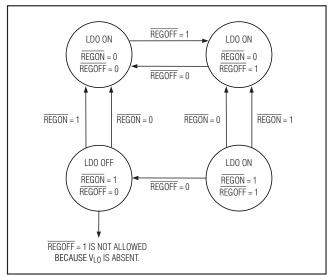

The <u>LDO</u> regulator is controlled through the  $\overline{\text{REGON}}$  and  $\overline{\text{REGOFF}}$  inputs as shown in Figure 4.  $\overline{\text{REGON}}$  is an input able to withstand voltages up to  $V_{BAT}$ . The LDO startup time is 1ms (typ).

There are two options for controlling the linear regulator:

- Wake-Up on Interrupt: In this case, REGON is connected to INT and when the MAX13037/MAX13038 generate an interrupt, the linear regulator is turned on, thus providing power to the local μCs. The μC pulls REGOFF high to keep the regulator on before making an SPI read (which causes INT and REGON to go high). The linear regulator can then be turned off by pulling REGOFF low.

- Direct Control: In this case, the regulator is enabled/disabled by some other signal in the system which must be connected to REGON. If REGOFF is not used, it must be connected to GND to allow the turnoff of the LDO.

Figure 4. Linear Regulator State Diagram

### **Linear Regulator Wake-Up**

Regulator wake-up can be controlled with the  $\overline{\text{INT}}$  output by connecting it to  $\overline{\text{REGON}}$ .  $\overline{\text{REGON}}$  is a TTL input with an internal pullup to a low-voltage internal reference of +4.8V (typ). With this control scheme, any change of the input switches (enabled for interrupt generation) causes the regulator to turn on, thus providing power to any external circuitry connected to VLO. If an external microcontroller is supplied from VLO, the microcontroller can keep the LDO on by forcing REGOFF high. Reading from the MAX13037/MAX13038 over the SPI interface causes the  $\overline{\text{INT}}$  output to go into high-impedance so that both  $\overline{\text{INT}}$  and  $\overline{\text{REGON}}$  are pulled high. After this phase, the microcontroller can turn off the regulator again by driving  $\overline{\text{REGOFF}}$  low.

Note that it is also possible to tie multiple open-drain active-low outputs in an ORing configuration, allowing the wakeup of the regulator from other devices.

If the  $\overline{\text{INT}}$  output is not used to control the regulator, connect the  $\overline{\text{REGOFF}}$  input to ground and use  $\overline{\text{REGON}}$  to enable or disable the regulator as shown in Figure 4.

### Watchdog Timer (WDI)

The MAX13037/MAX13038 feature a watchdog timer that is reset on every transition on the WDI input. If there is no transition on WDI before the first timeout period (twD1) the  $\overline{INT}$  output asserts low. If there is still no transition on WDI after the second timeout period (twD2), the  $\overline{RST}$  output is pulsed low for tRST and the  $\overline{INT}$  output deasserts (see Figure 3). The watchdog timeout period can be adjusted by changing the capacitor value on the TD input.

$t_{RST}$  (ms) = 2 x  $C_{TD}$  (nF)

$t_{WD1} = 4 \times t_{RST} (ms)$

$twD2 = 8 \times tRST (ms)$

Note that WDI can be tied to the  $\overline{CS}$  input to allow a watchdog reset for every read/write operation over the SPI interface. To avoid any corruption of the internal command register, it is necessary to transmit the full programming word (16 bits) for every  $\overline{CS}$  negative pulse.

## Reset Output (RST)

The  $\overline{\text{RST}}$  output asserts low when a watchdog timeout occurs or when the LDO output voltage drops below a certain threshold. The threshold voltage is set by connecting an external voltage divider on the THRESH input between VLO and GND. The voltage on THRESH is compared with an internal reference voltage of +1.24V and if it is lower, the  $\overline{\text{RST}}$  output asserts low for treshold.

\_ /N/XI/N

### **Mechanical Switch Inputs (IN0-IN7)**

INO–IN7 are the inputs for remote mechanical switches. The status of each switch input is indicated by the SW0 through SW7 bits in the status register, and each switch input can be programmed to not assert an interrupt (INT) by writing to the P0–P7 bits in the command register. All switch inputs are configured to assert an interrupt upon power-up.

The first four inputs (IN0–IN3) are intended for ground-connected switches. The remaining four inputs (IN4–IN7) can be programmed in sets of two for either ground-connected or battery-connected switches by writing to the M0 and M1 bits (see Table 5). The default state after power-up is IN2–IN7 configured for ground-connected switches, and IN0/IN1 configured for direct inputs.

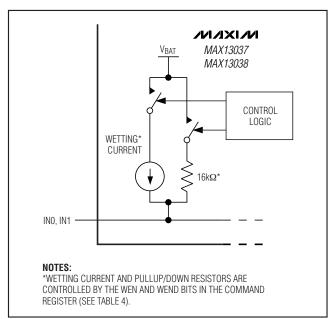

All switch inputs have internal  $16k\Omega$  sense resistors to detect switch transitions. Inputs configured for ground-connected switches are pulled up to BAT and inputs configured for battery-connected switches are pulled down to GND. Figure 5 shows the switch input structure for INO and IN1. INO and IN1 can be programmed as direct inputs with level-shifted outputs (DO0 and DO1) by clearing the WEND bit in the command register (normal mode only). When programmed as direct inputs, INO and IN1 can be used for PWM or other signaling. Clearing the WEND bit disables the sense resistors and wetting currents on INO and IN1. When programmed as direct inputs, the status of INO and IN1 is not reflected in the status register, and interrupts are not allowed on these inputs.

Figure 5. Input Structure of INO and IN1

### Switch Threshold Levels and Hysteresis (BATREF, HYST)

Input thresholds for the remote switches are 50% of the voltage applied to BATREF. The BATREF input is typically connected to the battery voltage before the reverse-battery protection diode. The MAX13037/MAX13038 feature adjustable hysteresis on the switch inputs by connecting an external 0 to 900k $\Omega$  resistor from HYST to ground (normal mode only). Short HYST to ground to obtain the maximum hysteresis of (0.5 x VBATREF). The approximate formula for hysteresis is given below:

$$V_{HYST} = \left[0.166 + \frac{43}{(123 + (\mathsf{R}_{\mathsf{HYST}(\mathsf{k}\Omega)})}\right] (V_{\mathsf{BATREF}})$$

To reduce power consumption, the adjustable hysteresis can be disabled by setting [SC2:SC1:SC0 = 1:1:0] in the command register. When the adjustable hysteresis is disabled, the hysteresis is set to 0.166 x VBATREF.

### **Switch Debounce and Deglitch**

The switch inputs INO–IN7 share a common programmable debounce timer to increase the noise immunity of the system in normal and scan mode. The switch debounce time is set by connecting a capacitor between the tDEB input and ground. The minimum value of this capacitor is 500pF and the maximum value is 10nF, corresponding to a debounce time of 5ms to 100ms respectively. To calculate other debounce times the following formula should be used:

$$C(nF) = tDEB(ms) / 10$$

All switch input glitches of less than 20µs in duration are automatically rejected by the MAX13037/MAX13038.

#### Debounce in Normal Mode

When a change of state occurs at the switch input the debounce timer starts. If the new state is stable for at least tDEB, the status register is updated and an interrupt is generated (if enabled). If the input returns to its previous state before the debounce time has elapsed, an interrupt is not generated and the status register is not updated.

#### Debounce in Scan Mode

A change of state at the switch input causes the device to automatically enter normal mode and the debounce timing to start. The device remains in normal mode as long as the input state differs from the previous state. As soon as the debounce time ends, the status register is updated, an interrupt is generated, and the device re-enters scan mode.

If the input returns to its previous state before the end of the debounce time, the device re-enters scan mode, an interrupt is not generated, and the status register is not updated.

### Wetting Current (WET)

The MAX13037/MAX13038 feature adjustable wetting current to any closed switch to clean switch contacts that are exposed to adverse conditions. The wetting current is set by connecting a  $30k\Omega$  to  $330k\Omega$  resistor from WET to ground. A  $30k\Omega$  resistor corresponds to a wetting current of 40mA (typ) and a  $330k\Omega$  resistor corresponds to a 4mA (typ) wetting current. See the *Typical Operating Characteristics* section for the relationship between the wetting current and RWET.

The WEN and WEND bits in the command register enable and disable the wetting currents and the WTOFF bit allows the wetting current to be activated for a duration of 20ms (typ) (see the *Command Register* section). Disabling wetting currents, or limiting the active wetting current time reduces power consumption. The default state upon power-up is all wetting currents disabled.

Wetting current is activated on closed switches just after the debounce time. The wetting current pulse starts after the debounce time. A wetting current pulse is provided to all closed switches when a valid input change is detected. Wetting current rise and fall times are controlled to enhance EMC performance. There is one wetting current timer for all switch inputs. Therefore, it is possible to observe wetting pulses longer than expected whenever two switches turn on in sequence and are spaced out less than twether long pulse only.

When using wetting currents, special care must be taken to avoid exceeding the maximum power dissipation of the MAX13037/MAX13038 (see the *Applications Information* section).

#### **Switch Outputs (D00, D01)**

DO0 and DO1 are direct level-shifted outputs of the switch inputs IN0 and IN1 when the WEND bit of the command register is cleared and when operating in normal mode. When configured as direct inputs, the wetting currents and sensing resistors are disabled on IN0 and IN1. DO0 and DO1 are three-stated when the WEND bit is set or when operating in scan mode.

When programmed as direct inputs, the status of INO and IN1 are not reflected in the status register and interrupts are not allowed on these inputs.

#### Interrupt Output (INT)

INT is an active-low, open-drain output that asserts when any of the switch inputs change state, as long as the particular input is enabled for interrupts (set by clearing P7-P0 in the command register). INT also

asserts when the first watchdog timeout period elapses (twD1). A pullup resistor to  $V_{LO}$  is needed on  $\overline{INT}$ .  $\overline{INT}$  is cleared when  $\overline{CS}$  is driven low for a read/write operation.

The INT output still asserts when V<sub>LO</sub> is disabled provided that it is pulled up to a different supply voltage.

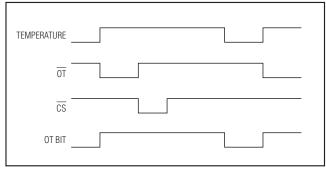

### Thermal Protection $(\overline{OT})$

The MAX13037/MAX13038 feature a two-level thermal protection strategy that prevents the device from being damaged by overheating. At the initial warning temperature of +135°C (typ), only wetting currents are disabled. The MAX13037/MAX13038 return to normal operation after the internal temperature decreases below +120°C (typ). This protection feature is disabled when WEN = 0 or when all inputs are open. At the second thermal warning temperature of +170°C (typ), the LDO is shut down. Because a  $\mu C$  is often supplied by the LDO, an overheating event caused by excessive power dissipation related to I/O wetting currents is normally resolved without affecting the  $\mu C$  status.

An open-drain, active-low output  $(\overline{OT})$  asserts low when the internal temperature of the device rises above the thermal warning threshold.  $\overline{OT}$  is immediately cleared when the  $\overline{CS}$  input is driven low for read/write operations, regardless of whether the temperature is above the threshold, or not. The overtemperature status of the MAX13037/MAX13038 can also be monitored by reading the OT bit in the status register. The OT bit is set when the internal temperature rises above the temperature threshold, and it is cleared when the temperature falls below the temperature hysteresis level. This allows a  $\mu C$  to monitor the overtemperature status, even if the  $\overline{OT}$  output has been cleared. See Figure 6 for an example timing diagram of the overtemperature alerts.

If desired, the  $\overline{OT}$  and  $\overline{INT}$  outputs can be connected to the same  $\mu C$  GPIO in a wired-OR configuration to save a  $\mu C$  pin. The  $\overline{OT}$  output still asserts when  $V_L$  is absent provided that it is pulled up to a different supply voltage.

Figure 6. Example Timing Diagram of the Overtemperature Alerts

\_\_\_\_\_\_\_\_/N/XI/N

Figure 7. SPI Read/Write Example

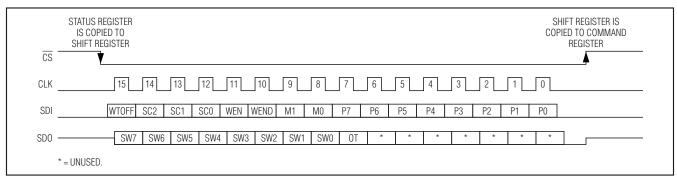

# Serial Peripheral Interface (CS, SD0, SDI, CLK)

The MAX13037/MAX13038 operate as a Serial Peripheral Interface (SPI) slave devices. An SPI master accesses the MAX13037/MAX13038 by reading from a status register and writing to a command register. Both registers are 16 bits long and are accessed most significant bit (MSB) first.

On the falling edge of CS, the status register is immediately loaded to an internal shift register and the contents are transferred out of the SDO output on the rising edge of CLK. Serial data on the SDI input is latched into the shift register on the falling edge of CLK. On the rising edge of  $\overline{CS}$ , the contents of the shift register are copied to the command register (see Figure 7). The status and command registers are 16 bits wide, so it is essential to clock a total of 16 bits while CS is low for the input and output data to be valid. When  $\overline{CS}$  is high, the SDO output is high-impedance and any transitions on CLK and SDI are ignored. The INT and OT flags are cleared on the CS falling edge. Input status changes occurring during the CS reading/writing operation are allowed. If a switch status changes when  $\overline{CS}$  is low, the interrupt is asserted as usual. This allows the part to be used even if VLO is disabled provided that the INT output is pulled up to another supply voltage.

### Status Register

The status register contains the status of the switches connected to IN7 through IN0 and it also contains an overtemperature warning bit (see Table 1). The status register is accessed through an SPI-compatible master.

#### Notes

### Bits 15-8: Switch 7 Through 0 Status (SW7-SW0)

SW7 through SW0 reflect the status of the switches connected to inputs IN7 through IN0, respectively. Open switches are returned as a [0] and closed switches are returned as a [1].

#### **Bit 7: Overtemperature Warning (OT)**

The OT bit returns a [1] when the internal temperature of the MAX13037/MAX13038 is above the temperature warning threshold of +135°C (typ). The OT bit returns a [0] when the MAX13037/MAX13038 is either below the temperature threshold, or it has fallen below the temperature hysteresis level following an overtemperature event.

#### Bits 6-0: Unused

Bits 6 through 0 are unused and should be ignored.

#### Command Register

The command register is used to configure the MAX13037/MAX13038 for various modes of operation and is accessed by an SPI-compatible master (see Table 2). The power-on reset (POR) value of the command register is 0x00.

**Table 1. Status Register**

| BIT  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|---|---|---|---|---|---|---|

| NAME | SW7 | SW6 | SW5 | SW4 | SW3 | SW2 | SW1 | SW0 | TO |   | _ |   |   | _ |   | _ |

### **Table 2. Command Register**

| BIT  | 15    | 14  | 13  | 12  | 11  | 10   | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|------|-------|-----|-----|-----|-----|------|----|----|----|----|----|----|----|----|----|----|

| NAME | WTOFF | SC2 | SC1 | SC0 | WEN | WEND | M1 | MO | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

| POR  | 0     | 0   | 0   | 0   | 0   | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### Notes:

#### **Bit 15: Wetting Current Mode (WTOFF)**

Set the WTOFF bit to configure the wetting currents as continuous on closed switches. Clear the WTOFF bit to configure the wetting current as a pulse where the wetting current is turned on for a set duration of 20ms after a switch closes (and the debounce is timed out). After 20ms elapses, the wetting current is turned off. Either wetting current mode is only applicable to switches that have wetting currents enabled (see WEN and WEND bits). In scan mode, the wetting currents are on for the polling time of 250µs (typ) and are pulsed at the programmed scanning period. When WTOFF is set, the wetting current continuously pulses at the programmed scanning period. When WTOFF is cleared, the wetting current pulses at the programmed scanning period, but turns off after 20ms elapses.

#### Bits 14, 13, 12: Scanning Period (SC2, SC1, SC0)

The SC2, SC1, and SC0 bits are used to program the scanning period as depicted in Table 3. Switch inputs are simultaneously polled for a finite duration of 250µs (typ), and polling occurs at a period selected through the SC2, SC1, and SC0 inputs. Figure 8 shows a timing diagram of switch scanning and sampling. When the inputs are not being polled, the sense resistors are disconnected, reducing the current consumption caused from polling closed switches. For a continuous scanning

period ([SC2:SC1:SC0] = [1:1:1] or [1:1:0]), the switch inputs are constantly being monitored and the sense resistors are always connected. The state [SC2:SC1:SC0] = [1:1:0] also disables adjustable hysteresis (normally set by  $R_{HYST}$ ) and fixes hysteresis at 0.166 x  $V_{BATREF}$ . When adjustable hysteresis is not needed, it is recommended to disable this feature to reduce power consumption.

### Bit 11: Global Wetting Current Enable (WEN)

The WEN bit is a global enable for the wetting currents on all the channels. Set the WEN bit to enable wetting currents on all channels and clear the WEN bit to disable wetting currents. Even with wetting currents globally enabled, the wetting currents and sense resistors on INO and IN1 can still be turned off with the WEND bit (see Table 4).

### Bit 10: IN0 and IN1 Wetting Current Enable (WEND)

The WEND bit is used to turn on wetting currents and sense resistors on inputs INO and IN1. Set the WEND bit to enable wetting currents on INO and IN1 and clear the WEND bit to turn off the wetting current and sense resistors on INO and IN1. When the wetting currents and sense resistors are disabled (WEND = 0), INO and IN1 are configured as direct inputs with level-shifted outputs on DOO and DO1. DOO and DO1 can only be used as level-shifted outputs in normal mode and are three-stated in scan mode (see the *Scan Mode* section). Note that both the WEN and WEND bits need to be set for wetting currents to be enabled on INO and

Table 3. Programmable Scanning Period

| SC2 | SC1 | SC0 | SCANNING PERIOD (ms)                 |

|-----|-----|-----|--------------------------------------|

| 0   | 0   | 0   | 64                                   |

| 0   | 0   | 1   | 32                                   |

| 0   | 1   | 0   | 16                                   |

| 0   | 1   | 1   | 8                                    |

| 1   | 0   | 0   | 4                                    |

| 1   | 0   | 1   | 2                                    |

| 1   | 1   | 0   | Continuous/adjustable hysteresis off |

| 1   | 1   | 1   | Continuous                           |

Figure 8. Switch Sampling in Scan Mode

#### Table 4. Truth Table for WEN and WEND

| WEN | WEND | WETTING CURRENT<br>(IN0, IN1) | 16kΩ SENSE RESISTOR (IN0, IN1) | WETTING CURRENT<br>(IN2-IN7) | 16k $\Omega$ SENSE RESISTOR (IN2–IN7) |  |

|-----|------|-------------------------------|--------------------------------|------------------------------|---------------------------------------|--|

| 0   | 0    | Off                           | Off                            | Off                          | On                                    |  |

| 0   | 1    | Off                           | On                             | Off                          | On                                    |  |

| 1   | 0    | Off                           | Off                            | On                           | On                                    |  |

| 1   | 1    | On                            | On                             | On                           | On                                    |  |

16 \_\_\_\_\_\_\_\_/N\_\_\_//N

Table 5. Switch Configuration Controlled by M1 and M0

| M1 | МО | IN7 AND IN6 SWITCH<br>CONFIGURATION | IN5 AND IN4 SWITCH<br>CONFIGURATION | IN3-IN0 SWITCH<br>CONFIGURATION |  |

|----|----|-------------------------------------|-------------------------------------|---------------------------------|--|

| 0  | 0  | Ground                              | Ground                              | Ground                          |  |

| 0  | 1  | Ground                              | Battery                             | Ground                          |  |

| 1  | 0  | Battery                             | Ground                              | Ground                          |  |

| 1  | 1  | Battery                             | Battery                             | Ground                          |  |

IN1 (see Table 4). The DO0 and DO1 outputs are three-stated when WEND = 1. When programmed as direct inputs (WEND = 0), any input changes on IN0 and IN1 are not reflected by the status register.

#### Bits 9 and 8: Switch Configuration for IN7-IN4 (M1, M0)

The M1 and M0 bits set the switch configuration in groups of two for IN7 through IN4 (see Table 5). Set M1 to configure IN7 and IN6 for battery-connected switches and clear M1 for ground-connected switches. Set M0 to configure IN5 and IN4 for battery-connected switches and clear M0 for ground-connected switches.

### Bits 7-0: Interrupt Enable for IN7-IN0 (P7-P0)

The P7 through P0 bits allow independent control of whether inputs IN7 through IN0 generate an interrupt  $(\overline{\text{INT}})$ . Set any bit to disable interrupts on the corresponding input and clear the bit to enable interrupts on the corresponding channel. An interrupt is asserted when any input configured for interrupts changes state. IN0 and IN1 do not generate an interrupt when configured as direct inputs (WEND = 0).

### **Operating Modes**

The MAX13037/MAX13038 feature three modes of operation: normal mode, scan mode, and shutdown mode. Normal mode is entered when the scanning period bits in the command register are configured for continuous scanning ([SC2:SC1:SC0] = [1:1:1] or [1:1:0]). Scan mode is entered when the scanning period bits are set for a periodic scanning time as shown in Table 3. Shutdown mode is entered by driving the shutdown input  $(\overline{SD})$  low. The default mode after power-up is scan mode (when  $\overline{SD}$  = high) with a scan period of 64ms.

### Normal Mode (Continuous Scanning)

In normal mode, the input sense resistors are always connected to the switch inputs to detect any input status change (except INO and IN1 when WEND = [0]). Wetting currents are enabled according to the WEN, WEND, and WTOFF bits in the command register. If adjustable hysteresis is not required, this feature can be disabled to reduce power consumption (see the *Typical Operating Characteristics*) by setting the scanning period bits in the

command register to ([SC2:SC1:SC0] = [1:1:0]). The hysteresis is set to 0.166 x  $V_{BATREF}$  when adjustable hysteresis is disabled.

### Scan Mode

In scan mode, each sense resistor is connected for a finite duration of 250µs (typ) and is repeated at a period according to the scanning period bits SC2, SC1, and SC0 (see Table 3). All input resistors are connected simultaneously and the inputs are polled at the same time. When all external switches are open and the scanning period is set to 64ms the scanning mode reduces current consumption to typically 28µA (LDO on) and 17µA (LDO off). Wetting currents (if enabled) are applied to closed switches during the polling time of 250µs (typ) and are pulsed at the programmed scanning period. When WTOFF is set, the wetting current continuously pulses at the programmed scanning period. When WTOFF is cleared, the wetting current pulses at the programmed scanning period, but turns off after 20ms elapses. Inputs INO and IN1 cannot be used as direct inputs (WEND = 0) in scan mode. When configured as direct inputs in scan mode, the outputs DO0 and DO1 are high impedance. The quiescent current for a given scan mode can be calculated by the following formula (LDO off):

$$I_{BAT(\mu A)} = 16 \times \left(1 + \frac{1}{t_{SCAN_P(ms)}}\right)$$

Where  $V_{BAT} = \overline{SD} = +14V$ ,  $I_{BAT}$  is the BAT current expressed in microamps and  $t_{SCAN\_P}$  is the scanning period expressed in milliseconds.

#### Shutdown Mode

In shutdown mode, the LDO is disabled, all switch inputs are high impedance and the external switches are no longer monitored, reducing current consumption on BAT to 2.85 $\mu$ A (typ). The MAX13037/MAX13038 reset upon entering shutdown mode and the contents of the command register are lost. Exit shutdown mode by bringing the voltage on  $\overline{SD}$  above +2.4V. The  $\overline{SD}$  input is compatible with voltages up to VBAT. The MAX13037/MAX13038 take 200 $\mu$ s (typ) to exit shutdown

18

# Automotive Contact Monitor and Level Shifters with LDO Regulator

at which point the command register is restored to its power-up default (0x00) and the MAX13037/MAX13038 enter scan mode. Note that  $\overline{SD}$  is compatible with both logic and BAT voltage levels. Having  $\overline{SD}$  compatible to V<sub>BAT</sub> allows the MAX13037/MAX13038 to retain the settings in the command register as well as input monitoring even when V<sub>LO</sub> is disabled, provided that  $\overline{SD} = V_{BAT}$ .

# **Applications Information**

### **Automotive Considerations**

### Reverse-Battery Tolerance

The BATREF and INO-IN7 inputs can withstand voltages down to -45V without damage so that reverse battery is not an issue. The BAT input should be protected with a reverse-battery diode as shown in the *Typical Application Circuit*. The shutdown (SD) and REGON inputs can be controlled from a battery-level source, but should be protected against reverse battery in the application.

#### **Power Dissipation**

Wetting currents and the LDO output current can result in overheating the MAX13037/MAX13038. At the early thermal warning threshold of +135°C (typ), wetting currents are disabled. This allows the LDO output to remain enabled if overheating is caused by the wetting currents. At temperatures above +170°C, the LDO is also turned off to avoid damage to the device.

It is important to consider the effects of wetting currents on the power dissipated by the MAX13037/MAX13038. For example, assume all inputs are configured for a continuous wetting current of 25mA, all external switches have an on-resistance of 1 $\Omega$  and the battery voltage is +16V. If all switches are simultaneously closed, the corresponding power dissipated due to wetting currents only is (16V - (25mA x 1 $\Omega$ )) x 25mA x 8 = 3.12W, which is higher than the absolute maximum power dissipation of 2857mW at +70°C.

The LDO is a second source of power dissipation. For example, if  $V_{LO} = +3.3V$ ,  $I_{LO} = 100$ mA and  $V_{BAT} = +16V$ , the power dissipated by the LDO is (16V - 3.3V) + (0.1) = 1.27W. Both the LDO and wetting currents should be taken into account for correct use of the MAX13037/MAX13038.

#### **ESD Protection**

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The IN7–IN0 inputs have extra protection against static electricity. Maxim's engineers have developed state-of-the-art structures to protect these pins against ESD of ±8kV without damage.

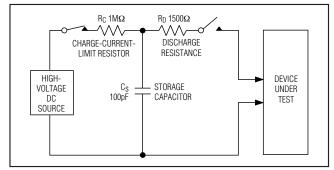

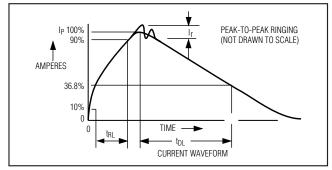

#### Human Body Model

The MAX13037/MAX13038 IN7-IN0 pins are characterized for  $\pm 8kV$  ESD protection using the Human Body Model, Figure 7a shows the Human Body Model, and Figure 7b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a 1.5k $\Omega$  resistor.

Figure 7a. Human Body ESD Test Model

Figure 7b. Human Body Model Current Waveform

Pin Configuration

# Typical Operating Circuit

\_Chip Information

PROCESS: BICMOS

20 \_\_\_\_\_\_/N/XI/M

# **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

# Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

|                   |           |      |           | MMON      | DIMENS    | IONS |           |      |      |

|-------------------|-----------|------|-----------|-----------|-----------|------|-----------|------|------|

| COMMON DIMENSIONS |           |      |           |           |           |      |           |      |      |

| PKG.              | 36L 6x6   |      |           | 40L 6x6   |           |      | 48L 6x6   |      |      |

| SYMBOL            | MIN.      | NOM  | MAX.      | MIN.      | NOM.      | MAX. | MIN       | NOM. | MAX. |

| A                 | 0.70      | 0.75 | 0.80      | 0.70      | 0.75      | 0.80 | 0.70      | 0.75 | 0.80 |

| A1                | 0         | 0.02 | 0.05      | 0         | 0.02      | 0.05 | 0         | _    | 0.05 |

| A2                | 0.20 REF. |      |           | 0.20 REF. |           |      | 0.20 REF. |      |      |

| b                 | 0.20      | 0.25 | 0.30      | 0.20      | 0.25      | 0.30 | 0.15      | 0.20 | 0.25 |

| D                 | 5.90      | 6.00 | 6.10      | 5.90      | 6.00      | 6.10 | 5.90      | 6.00 | 6.10 |

| E                 | 5.90      | 6.00 | 6.10      | 5.90      | 6.00      | 6.10 | 5.90      | 6.00 | 6.10 |

| 9                 | 0.50 BSC. |      | 0.50 BSC. |           | 0.40 BSC. |      |           |      |      |

| k                 | 0.25      | -    | -         | 0.25      | _         | ı    | 0.25      | _    | _    |

| L                 | 0.45      | 0.55 | 0.65      | 0.30      | 0.40      | 0.50 | 0.30      | 0.40 | 0.50 |

| N                 | 36        |      | 40        |           | 48        |      |           |      |      |

| ND                | 9         |      |           | 10        |           | 12   |           |      |      |

| NE                | 9         |      |           | 10        |           |      | 12        |      |      |

| JEDEC             | WJJD-1    |      |           | WJJD-2    |           |      | -         |      |      |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |

|------------------------|------|------|------|------|------|------|--|

| PKG.                   |      | D2   |      | E2   |      |      |  |

| CODES                  | MIN  | NOM. | MAX. | MIN. | NOM. | MAX  |  |

| T3666-2                | 3,60 | 3.70 | 3.80 | 3.60 | 3.70 | 3.80 |  |

| T3666-3                | 3.60 | 3.70 | 3.80 | 3.60 | 3.70 | 3.80 |  |

| T3666N-1               | 3.60 | 3.70 | 3.80 | 3.60 | 3.70 | 3.80 |  |

| T3666MN-1              | 3.60 | 3.70 | 3.80 | 3.60 | 3.70 | 3.80 |  |

| T4066-2                | 4.00 | 4.10 | 4.20 | 4.00 | 4.10 | 4.20 |  |

| T4066-3                | 4.00 | 4.10 | 4.20 | 4.00 | 4.10 | 4.20 |  |

| T4066-4                | 4.00 | 4.10 | 4.20 | 4.00 | 4.10 | 4.20 |  |

| T4066-5                | 4.00 | 4.10 | 4.20 | 4.00 | 4.10 | 4.20 |  |

| T4866-1                | 4.40 | 4.50 | 4.60 | 4.40 | 4.50 | 4.60 |  |

| T4866-2                | 4.40 | 4.50 | 4.60 | 4.40 | 4.50 | 4.60 |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- 6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- & COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR 0.4mm LEAD PITCH PACKAGE T4866-1.

- 10. WARPAGE SHALL NOT EXCEED 0.10 mm.

- MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 12. NUMBER OF LEADS SHOWN FOR REFERENCE ONLY.

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.