### PIN DESCRIPTION

#### J1 - POWER CONNECTOR

Tyco AMP #640445-8 or equivalent.

Mates with Tyco AMP 640428-8, Molex 09-50-3081 or equivalent

#### PIN SIGNAL DESCRIPTION

| PIN | SIGNAL          | DESCRIPTION                |

|-----|-----------------|----------------------------|

| 1   | N/C             | No connection              |

| 2   | N/C             | No connection              |

| 3   | KEY             | Used to key connector      |

| 4   | GND             | Ground                     |

| 5   | GND             | Ground                     |

| 6   | V <sub>CC</sub> | Logic and LED drive supply |

| 7   | RESERVED        | No connection              |

| 8   | N/C             | No connection              |

#### J2 - DATA CONNECTOR

Tyco AMP #103309-2 or equivalent.

Mates with Tyco AMP 746195-2, Molex 39-27-1146 or equivalent

| PIN | DESCRIPTION    | PIN | DESCRIPTION |

|-----|----------------|-----|-------------|

| 1   | Display enable | 2   | Ground      |

| 3   | Row data       | 4   | Ground      |

| 5   | Row clock      | 6   | Ground      |

| 7   | Column latch   | 8   | Ground      |

| 9   | Dot clock      | 10  | Ground      |

| 11  | Serial data    | 12  | Ground      |

| 13  | No connection  | 14  | Ground      |

#### J3 - POWER CONNECTOR

Tyco AMP #641737-1 or equivalent.

Mates with Tyco AMP 1-480424-0 housing, 60617-4 socket terminals

| PIN | SIGNAL          | DESCRIPTION                |

|-----|-----------------|----------------------------|

| 1   | RESERVED        | No connection              |

| 2   | GND             | Ground                     |

| 3   | GND             | Ground                     |

| 4   | V <sub>CC</sub> | Logic and LED drive supply |

### INTERFACE SIGNAL DESCRIPTION

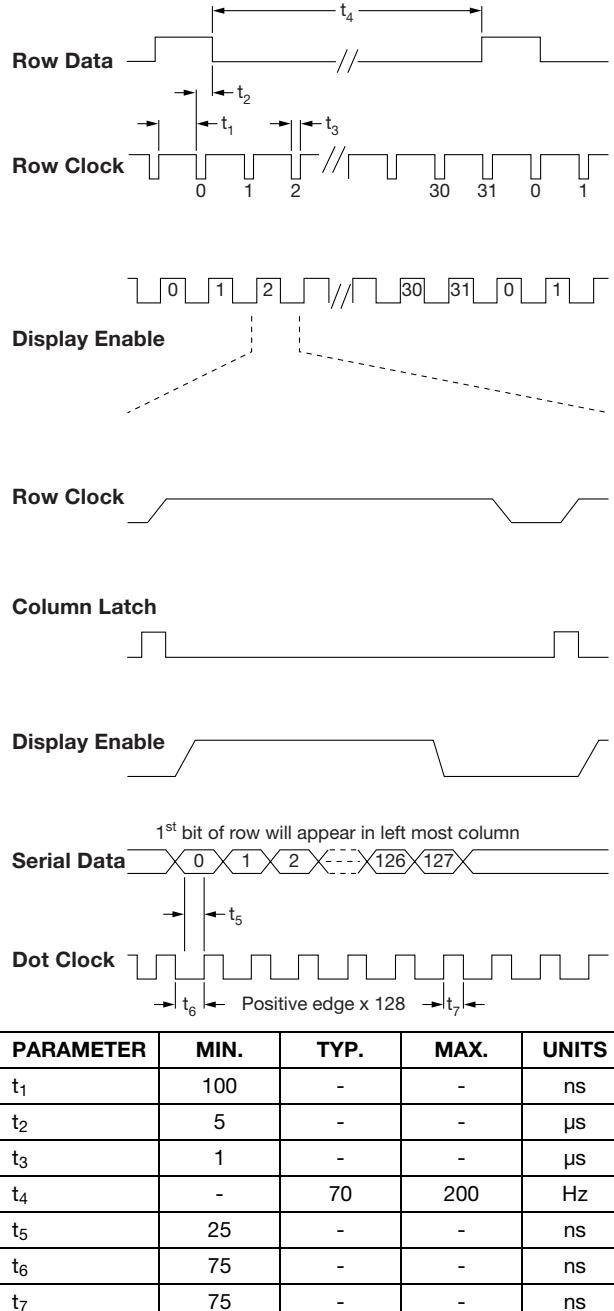

**Dot clock** - This signal enters the *serial data* on each low to high transition. A total of 128 *dot clock* transitions must be present for each line of column/anode data.

**Serial data** - This signal presents the pixel data in positive logic format. A logic one represents a lit pixel and a logic zero represents an extinguished pixel. Data is entered from right to left. The first pixel data entered will represent the left most pixel in the row.

**Column latch** - This signal latches the pixel data into the driver outputs. When the *column latch* signal goes to logic one the data entered previously will fall through to the driver outputs. When the signal returns to a logic zero the data is latched and the shift register is now ready to accept the next row of data. Must be held low while entering new *serial data*.

**Display enable** - This signal enables the output drivers. Using a duty cycle control, this signal may also be used for intensity control. The *display enable* must be at logic zero before the *column latch* signal transitions. To avoid display blurring, the *row clock* signal should also transition while *display enable* is a logic zero.

**Row data** - This signal is the first line marker for the scan. This input should be held high to correspond to the first row of pixel data.

**Row clock** - This signal clocks *row data* on the falling edge. The *row clock* signal is repetitive and must be present for proper scanning of the display module.

The LED-128G032-1 has an unique input protection circuit that assures the column drivers stay blanked on power up. The protection circuit unblanks the column drivers when the *row clock* signal begins (i.e the display begins scanning).

### LOGIC AND DATA TIMING

### ORDERING INFORMATION

| DESCRIPTION                                             | PART NUMBER   |

|---------------------------------------------------------|---------------|

| Display, Driver Electronics and + 5 V HC CMOS Interface | LED-128G032-1 |

| J2 Data Connector Kit (2 pcs. recommended)              | 280105-05     |

| J1 Power Connector Kit                                  | 280108-12     |

| J3 Power Connector Kit                                  | 280108-05     |

## **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.