# LP38512-ADJ

# 1.5A Fast-Transient Response Adjustable Low-Dropout Linear Voltage Regulator

## **General Description**

The LP38512-ADJ Fast-Transient Response Low-Dropout Voltage Regulator offers the highest-performance in meeting AC and DC accuracy requirements for powering Digital Cores. The LP38512-ADJ uses a proprietary control loop that enables extremely fast response to change in line conditions and load demands. Output Voltage DC accuracy is guaranteed at 2.5% over line, load and full temperature range from -40°C to +125°C. The LP38512-ADJ is designed for inputs from the 2.5V, 3.3V, and 5.0V rail, is stable with 10  $\mu$ F ceramic capacitors, and has an adjustable output voltage. The LP38512-ADJ provides excellent transient performance to meet the demand of high performance digital core ASICs, DSPs, and FPGAs found in highly-intensive applications such as servers, routers/switches, and base stations.

### **Features**

- 2.25V to 5.5V Input Voltage Range

- Adjustable Output Voltage Range of 0.5V to 4.5V

- 1.5A Output Load Current

- ±2.0% Accuracy over Line, Load, and Full-Temperature Range from -40°C to +125°C

- Stable with tiny 10 µF ceramic capacitors

- Enable pin

- Typically less than 1uA of Ground pin current in when Enable pin is low

- 25dB of PSRR at 100 kHz

- Over-Temperature and Over-Current Protection

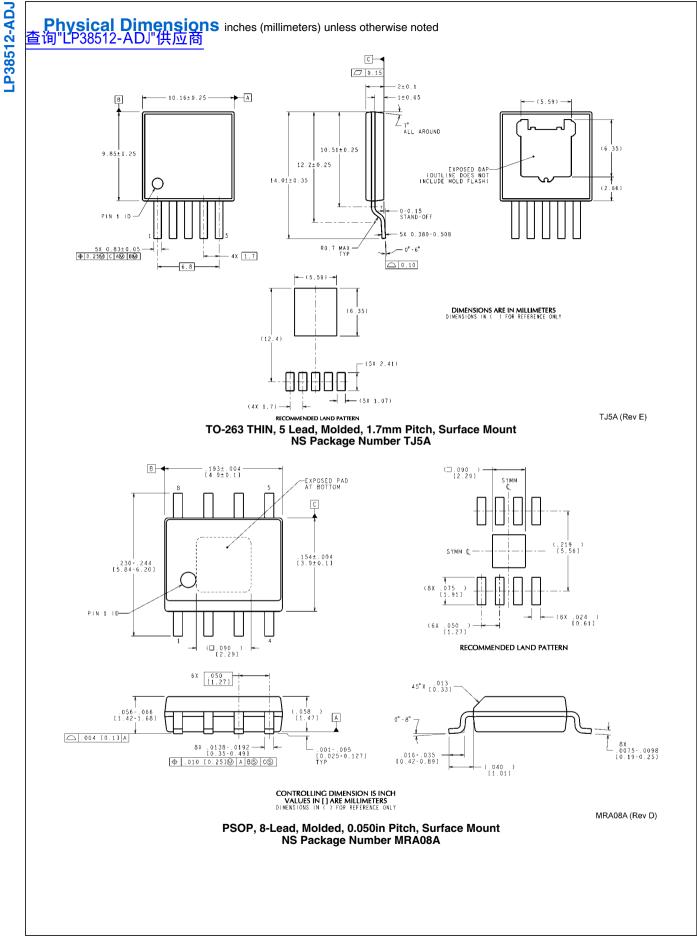

- PSOP-8 and TO263 THIN Surface Mount Packages

## **Applications**

- Digital Core ASICs, FPGAs, and DSPs

- Servers

- Routers and Switches

- Base Stations

- Storage Area Networks

- DDR2 Memory

\_P38512-ADJ 1.5A Fast-Transient Response Adjustable Low-Dropout Linear Voltage Regulator

Output

Voltage

ADJ

#### Ordering Information 查询"LP38512-ADJ"供应商

Number

LP38512MR-ADJ

LP38512MRX-ADJ

Order

LP38512TJ-ADJ

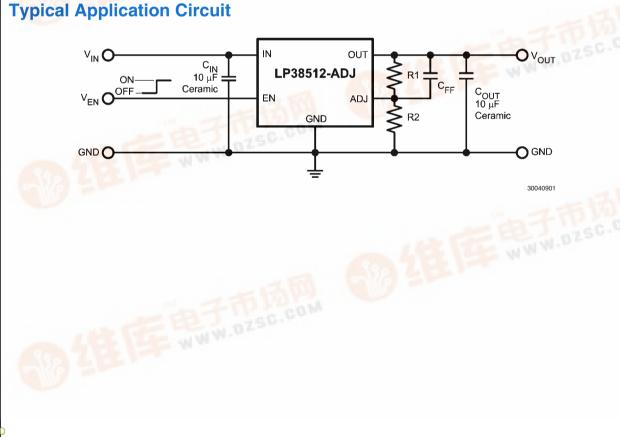

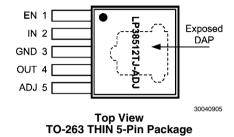

## **Connection Diagrams**

Supplie

As

Rail

Tape and Reel

Tape and Reel

Package

Marking

LP38512MR-ADJ

LP38512MR-ADJ

LP38512TJ-ADJ

Top View PSOP 8-Pin Package

## Pin Descriptions for TO-263 THIN (TJ) Package

| Pin # | Pin Name                                                                                                                                      | Function                                                                                                                                                                                                                                                                                                                             |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | 1 Enable. Pull high to enable the output, low to disable the output. This pin has n<br>must be tied to the input voltage, or actively driven. |                                                                                                                                                                                                                                                                                                                                      |  |  |

| 2     | IN                                                                                                                                            | Input Supply Pin                                                                                                                                                                                                                                                                                                                     |  |  |

| 3     | GND                                                                                                                                           | Ground                                                                                                                                                                                                                                                                                                                               |  |  |

| 4     | OUT                                                                                                                                           | Regulated Output Voltage Pin                                                                                                                                                                                                                                                                                                         |  |  |

| 5     | ADJ                                                                                                                                           | The feedback to the internal Error Amplifier to set the output voltage                                                                                                                                                                                                                                                               |  |  |

| DAP   | DAP                                                                                                                                           | The TJ-263 DAP is used as a thermal connection to remove heat from the device to an external heat-sink in the form of the copper area on the printed circuit board. The DAP is physically connected to backside of the die, but is not internally connected to device ground. The DAP should be soldered to the Ground Plane copper. |  |  |

Package

Туре

PSOP-8

PSOP-8

TO263 THIN

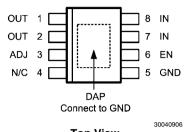

## Pin Descriptions for PSOP-8 (MR) Package

| Pin # | Pin Name | Function                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 2  | OUT      | Regulated Output Voltage Pin. Pins share current and must be connected together.                                                                                                                                                                                                                                                                |  |  |  |

| 3     | ADJ      | The feedback to the internal Error Amplifier to set the output voltage                                                                                                                                                                                                                                                                          |  |  |  |

| 4     | N/C      | No internal connection.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 5     | GND      | Ground                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 6     | EN       | Enable. Pull high to enable the output, low to disable the output. This pin has no internal bias and must be tied to the input voltage, or actively driven.                                                                                                                                                                                     |  |  |  |

| 7, 8  | IN       | Input Supply Pin. Pins share current and must be connected together.                                                                                                                                                                                                                                                                            |  |  |  |

| DAP   | DAP      | The PSOP-8 DAP connection is used as a thermal connection to remove heat from the device to an external heat-sink in the form of the copper area on the printed circuit board. The DAP is physically connected to backside of the die, but is not internally connected to device ground. The DAP should be soldered to the Ground Plane copper. |  |  |  |

# LP38512-ADJ

Absolute Maximum Ratings (Note 1) 首何"L P38512-AD.J"供以商 If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Storage Temperature Range      | –65°C to +150°C    |

|--------------------------------|--------------------|

| Soldering Temperature (Note 3) |                    |

| Thin TO-263                    | 260°C, 10s         |

| PSOP-8                         | 260°C, 10s         |

| ESD Rating (Note 2)            | ±2 kV              |

| Power Dissipation (Note 4)     | Internally Limited |

| Input Pin Voltage (Survival)   | -0.3V to +6.0V     |

| Enable Pin Voltage (Survival)  | -0.3V to +6.0V     |

| Output Pin Voltage (Survival)  | -0.3V to +6.0V     |

| ADJ Pin Voltage (Survival)     | -0.3V to +6.0V     |

| I <sub>OUT</sub> (Survival)    | Internally Limited |

## Operating Ratings (Note 1)

Input Supply Voltage,  $V_{IN}$ Output Voltage,  $V_{OUT}$ Enable Input Voltage,  $V_{EN}$ Output Current (DC) Junction Temperature (Note 4) 2.25V to 5.5V V<sub>ADJ</sub> to 5V 0.0V to 5.5V 1 mA to 1.5A -40°C to +125°C

## **Electrical Characteristics**

Unless otherwise specified:  $V_{IN}$ = 2.50V,  $V_{OUT}$ =  $V_{ADJ}$ ,  $I_{OUT}$ = 10 mA,  $C_{IN}$ = 10 µF,  $C_{OUT}$ = 10 µF,  $V_{EN}$ = 2.0V. Limits in standard type are for  $T_J$ = 25°C only; limits in **boldface type** apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$ = 25°C, and are provided for reference purposes only.

| Symbol                               | Parameter                                        | Conditions                                                                                          | Min                   | Тур                 | Max                   | Units |  |

|--------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|---------------------|-----------------------|-------|--|

| V <sub>ADJ</sub>                     | V <sub>ADJ</sub> Accuracy<br>(Note 7)            | $2.25V \le V_{IN} \le 5.5V$<br>10 mA $\le I_{OUT} \le 1.5A$                                         | 495.0<br><b>490.0</b> | 500.                | 505.0<br><b>510.0</b> | mV    |  |

| I <sub>ADJ</sub>                     | ADJ Pin Bias Current                             | $2.25V \le V_{ N } \le 5.5V$                                                                        | -                     | 1                   | -                     | nA    |  |

| ΔV <sub>ADJ</sub> /ΔV <sub>IN</sub>  | V <sub>ADJ</sub> Line Regulation<br>(Notes 5, 7) | $2.25V \le V_{IN} \le 5.5V$                                                                         | -                     | 0.03<br><b>0.06</b> | -                     | %/V   |  |

| ΔV <sub>ADJ</sub> /ΔΙ <sub>ΟUT</sub> | V <sub>ADJ</sub> Load Regulation<br>(Notes 6, 7) | 10 mA ≤ I <sub>OUT</sub> ≤ 1.5A                                                                     | -                     | 0.10<br><b>0.20</b> | -                     | %/A   |  |

| V <sub>DO</sub>                      | Dropout Voltage<br>(Note 8)                      | I <sub>OUT</sub> = 1.5A                                                                             | -                     | -                   | 300                   | mV    |  |

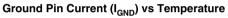

| I <sub>GND</sub>                     | Ground Pin Current, Output                       | I <sub>OUT</sub> = 10 mA                                                                            | -                     | 10                  | 12<br><b>15</b>       | mA    |  |

|                                      | Enabled                                          | I <sub>OUT</sub> = 1.5A                                                                             | -                     | 10                  | 12<br><b>14</b>       | mA    |  |

|                                      | Ground Pin Current, Output<br>Disabled           | V <sub>EN</sub> = 0.50V                                                                             | -                     | 60                  | 100<br><b>110</b>     | μA    |  |

| I <sub>SC</sub>                      | Short Circuit Current                            | $V_{OUT} = 0V$                                                                                      | -                     | 2.8                 | -                     | A     |  |

| nable Input                          |                                                  |                                                                                                     |                       |                     |                       |       |  |

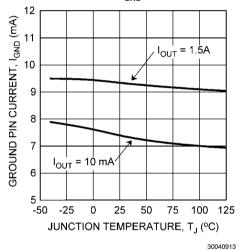

| V <sub>EN(ON)</sub>                  | Enable ON Voltage Threshold                      | $V_{EN}$ rising from < $V_{EN(OFF)}$ until $V_{OUT} = ON$                                           | 0.90<br><b>0.80</b>   | 1.20                | 1.50<br><b>1.60</b>   | V     |  |

| $V_{\text{EN(OFF)}}$                 | Enable OFF Voltage<br>Threshold                  | $V_{EN}$ falling from > $V_{EN(ON)}$ until $V_{OUT} = OFF$                                          | 0.60<br><b>0.50</b>   | 1.00                | 1.40<br><b>1.50</b>   | V     |  |

| V <sub>EN(HYS)</sub>                 | Enable Voltage Hysteresis                        | V <sub>EN(ON)</sub> - V <sub>EN(OFF)</sub>                                                          | -                     | 200                 | -                     | mV    |  |

|                                      |                                                  | $V_{EN} = V_{IN}$                                                                                   | -                     | 1                   | -                     |       |  |

| I <sub>EN</sub>                      | Enable Pin Current                               | V <sub>EN</sub> = 0V                                                                                | -                     | -1                  | -                     | – nA  |  |

| t <sub>d(OFF)</sub>                  | Turn-off delay                                   | Time from V <sub>EN</sub> < V <sub>EN(TH)</sub> to V <sub>OUT</sub> = OFF, I <sub>LOAD</sub> = 1.5A | -                     | 5                   | -                     |       |  |

| t <sub>d(ON)</sub> Turn-on delay     |                                                  | Time from $V_{EN} > V_{EN(TH)}$ to $V_{OUT} = ON$ , $I_{LOAD} = 1.5A$                               | -                     | 5                   | -                     | μs    |  |

| Symbol          | Parameter                                             | Conditions                          | Min | Тур | Max | Units             |  |

|-----------------|-------------------------------------------------------|-------------------------------------|-----|-----|-----|-------------------|--|

| Paramete        | 12-ADJ"供应商                                            |                                     | 3   |     |     | •                 |  |

| PSRR            | Ripple Rejection                                      | V <sub>IN</sub> = 2.5V<br>f = 120Hz | -   | 73  | -   | - dB              |  |

|                 |                                                       | V <sub>IN</sub> = 2.5V<br>f = 1 kHz | -   | 70  | -   |                   |  |

| $\rho_{n(l/f)}$ | Output Noise Density                                  | f = 120Hz                           | -   | 0.4 | -   | μV/√ <del>Π</del> |  |

| e <sub>n</sub>  | Output Noise Voltage                                  | BW = 10Hz - 100kHz                  | -   | 25  | -   | μV <sub>RMS</sub> |  |

| nermal Cha      | racteristics                                          |                                     | 3   |     |     |                   |  |

| $T_{SD}$        | Thermal Shutdown                                      | T <sub>J</sub> rising               | -   | 165 | -   | °C                |  |

| $\Delta T_{SD}$ | Thermal Shutdown Hysteresis                           | $T_J$ falling from $T_{SD}$         | -   | 10  | -   | - °C              |  |

| $\theta_{J-A}$  | Thermal Resistance<br>Junction to Ambient<br>(Note 4) | PSOP-8                              | -   | 168 | -   | °C/W              |  |

|                 |                                                       | TO-263 THIN                         | -   | 67  | -   |                   |  |

| 0               | Thermal Resistance                                    | PSOP-8                              | -   | 11  | -   | · · · · ·         |  |

| $\theta_{J-C}$  | Junction to Case                                      | TO-263 THIN                         | -   | 3   | -   | - °C/W            |  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and conditions, see the Electrical Characteristics.

Note 2: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. Test method is per JESD22-A114.

Note 3: Refer to JEDEC J-STD-020C for surface mount device (SMD) package reflow profiles and conditions. Unless otherwise stated, the temperatures and times are for Sn-Pb (STD) only.

Note 4: Device operation must be evaluated, and derated as needed, based on ambient temperature  $(T_A)$ , power dissipation  $(P_D)$ , maximum allowable operating junction temperature  $(T_{J(MAX)})$ , and package thermal resistance  $(\theta_{JA})$ . The typical  $\theta_{JA}$  ratings given are worst case based on minimum land area on two-layer PCB (EIA/JESD51-3). See *POWER DISSIPATION/HEAT-SINKING* for details.

Note 5: Line regulation is defined as the change in  $V_{ADJ}$  from the nominal value due to change in the voltage at the input.

Note 6: Load regulation is defined as the change in V<sub>ADJ</sub> from the nominal value due to change in the load current at the output.

Note 7: The line and load regulation specification contains only the typical number. However, the limits for line and load regulation are included in the output voltage tolerance specification.

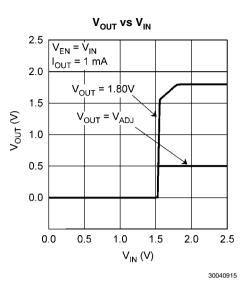

**Note 8:** Dropout voltage ( $V_{DO}$ ) is typically defined as the input to output voltage differential ( $V_{IN} - V_{OUT}$ ) where the input voltage is low enough to cause the output voltage to drop 2%. For the LP38512-ADJ, the minimum operating voltage of 2.25V is the limiting factor when the programed output voltage is less than typically 1.80V.

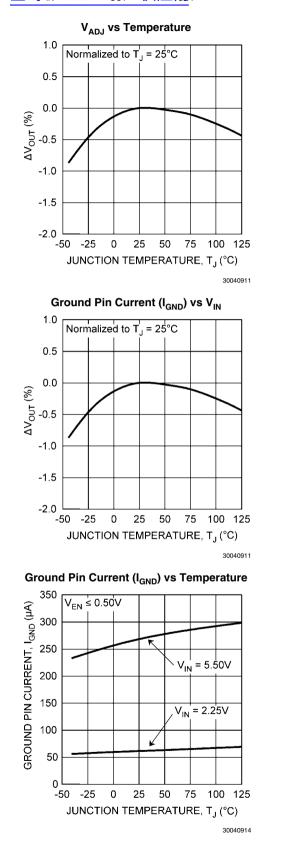

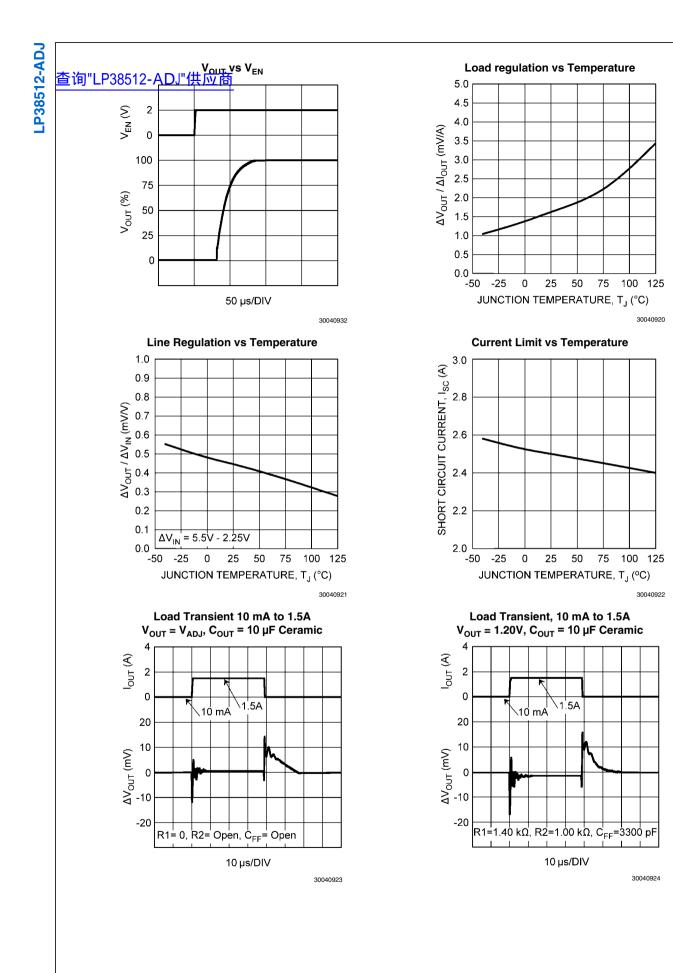

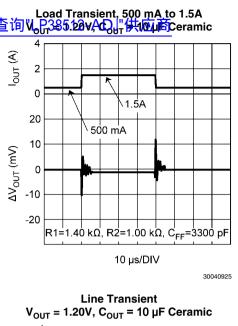

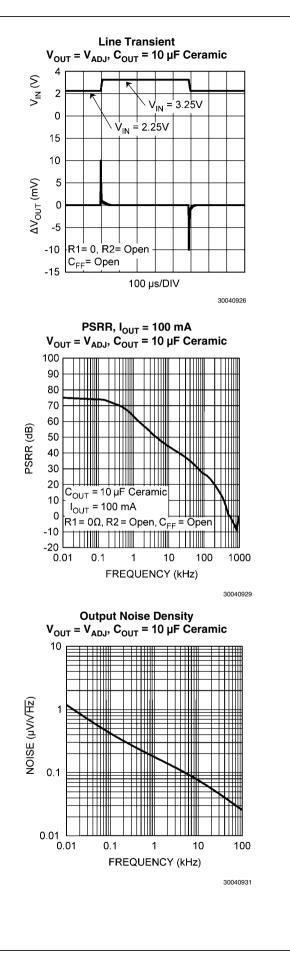

# Typical Performance Characteristics Unless otherwise specified: T<sub>J</sub> = 25°C, V<sub>IN</sub> = 2.50V, V<sub>OUT</sub>= V<sub>ADJ</sub>, V<sub>EN</sub> = 查讨论从P305作2CAD+"供应商<sub>JT</sub> = 10 mA.

**Enable Threshold vs Temperature**

# 查爾哈哈哈姆國國際地方

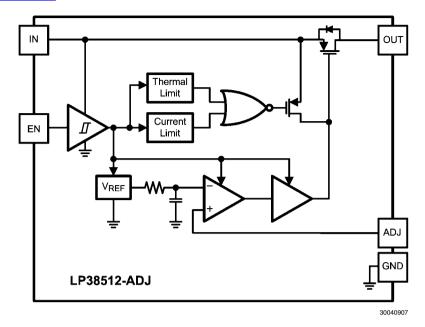

#### Application Information EXTERNAL CAPACITORS

Like any low-dropout regulator, external capacitors are required to assure stability. These capacitors must be correctly selected for proper performance.

#### **Input Capacitor**

A ceramic input capacitor of at least 10  $\mu$ F is required. For general usage across all load currents and operating conditions, a 10  $\mu$ F ceramic input capacitor will provide satisfactory performance.

#### **Output Capacitor**

A ceramic capacitor with a minimum value of 10  $\mu F$  is required at the output pin for loop stability. It must be located less than 1 cm from the device and connected directly to the output and ground pin using traces which have no other currents flowing through them. As long as the minimum of 10  $\mu F$  ceramic is met, there is no limitation on any additional capacitance.

X7R and X5R dielectric ceramic capacitors are strongly recommended, as they typically maintain a capacitance range within  $\pm 20\%$  of nominal over full operating ratings of temperature and voltage. Of course, they are typically larger and more costly than Z5U/Y5U types for a given voltage and capacitance.

Z5U and Y5V dielectric ceramics are not recommended as the capacitance will drop severely with applied voltage. A typical Z5U or Y5V capacitor can lose 60% of its rated capacitance with half of the rated voltage applied to it. The Z5U and Y5V also exhibit a severe temperature effect, losing more than 50% of nominal capacitance at high and low limits of the temperature range.

#### **REVERSE VOLTAGE**

A reverse voltage condition will exist when the voltage at the output pin is higher than the voltage at the input pin. Typically this will happen when  $V_{\rm IN}$  is abruptly taken low and  $C_{\rm OUT}$  continues to hold a sufficient charge such that the input to output

voltage becomes reversed. A less common condition is when an alternate voltage source is connected to the output.

There are two possible paths for current to flow from the output pin back to the input during a reverse voltage condition.

While  $V_{IN}$  is high enough to keep the control circuity alive, and the Enable pin is above the  $V_{EN(ON)}$  threshold, the control circuitry will attempt to regulate the output voltage. Since the input voltage is less than the programmed output voltage, the control circuit will drive the gate of the pass element to the full on condition when the output voltage begins to fall. In this condition, reverse current will flow from the output pin to the input pin, limited only by the R<sub>DS(ON)</sub> of the pass element and the output to input voltage differential. Discharging an output capacitor up to 1000 µF in this manner will not damage the device as the current will rapidly decay. However, continuous reverse current should be avoided. When the Enable is low this condition will be prevented.

The internal PFET pass element in the LP38512-ADJ has an inherent parasitic diode. During normal operation, the input voltage is higher than the output voltage and the parasitic diode is reverse biased. However, if the output voltage to input voltage differential is more than 500 mV (typical) the parasitic diode becomes forward biased and current flows from the output pin to the input pin through the diode. The current in the parasitic diode should be limited to less than 1A continuous and 5A peak.

If used in a dual-supply system where the regulator output load is returned to a negative supply, the output pin must be diode clamped to ground. A Schottky diode is recommended for this protective clamp.

#### SHORT-CIRCUIT PROTECTION

The LP38512-ADJ is short circuit protected, and in the event of a peak over-current condition the short-circuit control loop will rapidly drive the output PMOS pass element off. Once the power pass element shuts down, the control loop will rapidly cycle the output on and off until the average power dissipation causes the thermal shutdown circuit to respond to servo the on/off cashing to a torget frequency Planet refer to the POW-ER DISSIPATION/HEAT-SINKING section for power dissipation calculations.

#### SETTING THE OUTPUT VOLTAGE

The output voltage is set using the external resistive divider R1 and R2. The output voltage is given by the formula:

$$V_{OUT} = V_{ADJ} x (1 + (R1/R2))$$

(1)

The resistors used for R1 and R2 should be high quality, tight tolerance, and with matching temperature coefficients. It is important to remember that, although the value of  $V_{ADJ}$  is guaranteed, the final value of  $V_{OUT}$  is not. The use of low quality resistors for R1 and R2 can easily produce a  $V_{OUT}$  value that is unacceptable.

It is recommended that the values selected for R1 and R2 are such that the parallel value is less than 1.00 k $\Omega$ . This is to reduce the possibility of any internal parasitic capacitances on the ADJ pin from creating an undesirable phase shift that may interfere with device stability.

$$((R1 \times R2) / (R1 + R2)) \le 1.00 \text{ k}\Omega$$

(2)

#### FEED FORWARD CAPACITOR, C<sub>FF</sub>

When using a ceramic capacitor for  $C_{OUT}$ , the typical ESR value will be too small to provide any meaningful positive phase compensation,  $F_{z}$ , to offset the internal negative phase shifts in the gain loop.

$$F_{z} = 1 / (2 \times \pi \times C_{OUT} \times ESR)$$

(3)

A capacitor placed across the gain resistor R1 will provide additional phase margin to improve load transient response of the device. This capacitor,  $C_{FF}$ , in parallel with R1, will form a zero in the loop response given by the formula:

$$F_{z} = 1 / (2 \times \pi \times C_{FF} \times R1)$$

(4)

For optimum load transient response select  $C_{FF}$  so the zero frequency,  $F_Z$ , falls between 20 kHz and 40 kHz.

$$C_{FF} = 1 / (2 \times \pi \times R1 \times F_Z)$$

(5)

The phase lead provided by  $C_{\rm FF}$  diminishes as the DC gain approaches unity, or  $V_{\rm OUT}$  approaches  $V_{\rm ADJ}.$  This is because  $C_{\rm FF}$  also forms a pole with a frequency of:

$$F_{P} = 1 / (2 \times \pi \times C_{FF} \times (R1 \parallel R2))$$

(6)

It's important to note that at higher output voltages, where R1 is much larger than R2, the pole and zero are far apart in frequency. At lower output voltages the frequency of the pole and the zero mover closer together. The phase lead provided from C<sub>FF</sub> diminishes quickly as the output voltage is reduced, and has no effect when V<sub>OUT</sub> = V<sub>ADJ</sub>. For this reason, relying

on this compensation technique alone is adequate only for higher output voltages.

Table 1 lists some suggested, best fit, standard ±1% resistor values for R1 and R2, and a standard ±10% capacitor values for C<sub>FF</sub>, for a range of V<sub>OUT</sub> values. Other values of R1, R2, and C<sub>FF</sub> are available that will give similar results.

| V <sub>OUT</sub> | R <sub>1</sub> | R <sub>2</sub> | C <sub>FF</sub> | Fz       |

|------------------|----------------|----------------|-----------------|----------|

| 0.80V            | 1.07 kΩ        | 1.78 kΩ        | 4700 pF         | 31.6 kHz |

| 1.00V            | 1.00 kΩ        | 1.00 kΩ        | 4700 pF         | 33.8 kHz |

| 1.20V            | 1.40 kΩ        | 1.00 kΩ        | 3300 pF         | 34.4 kHz |

| 1.50V            | 2.00 kΩ        | 1.00 kΩ        | 2700 pF         | 29.5 kHz |

| 1.80V            | 2.94 kΩ        | 1.13 kΩ        | 1500 pF         | 36.1kHz  |

| 2.00V            | 1.02 kΩ        | 340Ω           | 4700 pF         | 33.2 kHz |

| 2.50V            | 1.02 kΩ        | 255Ω           | 4700 pF         | 33.2 kHz |

| 3.00V            | 1.00 kΩ        | 200Ω           | 4700 pF         | 33.8 kHz |

| 3.30V            | 2.00 kΩ        | 357Ω           | 2700 pF         | 29.5 kHz |

Please refer to Application Note AN-1378 Method For Calculating Output Voltage Tolerances in Adjustable Regulators for additional information on how resistor tolerances affect the calculated  $V_{OUT}$  value.

#### **ENABLE OPERATION**

The Enable ON threshold is typically 1.2V, and the OFF threshold is typically 1.0V. To ensure reliable operation the Enable pin voltage must rise above the maximum  $V_{EN(ON)}$  threshold and must fall below the minimum  $V_{EN(OFF)}$  threshold. The Enable threshold has typically 200mV of hysteresis to improve noise immunity.

The Enable pin (EN) has no internal pull-up or pull-down to establish a default condition and, as a result, this pin must be terminated either actively or passively.

If the Enable pin is driven from a single ended device (such as the collector of a discrete transistor) a pull-up resistor to V<sub>IN</sub>, or a pull-down resistor to ground, will be required for proper operation. A 1 k $\Omega$  to 100 k $\Omega$  resistor can be used as the pull-up or pull-down resistor to establish default condition for the EN pin. The resistor value selected should be appropriate to swamp out any leakage in the external single ended device, as well as any stray capacitance.

If the Enable pin is driven from a source that actively pulls high and low (such as a CMOS rail to rail comparator output), the pull-up, or pull-down, resistor is not required.

If the application does not require the Enable function, the pin should be connected directly to the adjacent  $V_{\rm IN}$  pin.

#### **POWER DISSIPATION/HEAT-SINKING**

A heat-sink may be required depending on the maximum power dissipation ( $P_{D(MAX)}$ ), maximum ambient temperature ( $T_{A(MAX)}$ )of the application, and the thermal resistance ( $\theta_{JA}$ ) of the package. Under all possible conditions, the junction temperature ( $T_{J}$ ) must be within the range specified in the Operating Ratings. The total power dissipation of the device is given by:

$$P_{D} = ((V_{IN} - V_{OUT}) \times I_{OUT}) + ((V_{IN}) \times I_{GND})$$

(7)

where  $I_{GND}$  is the operating ground current of the device (specified under Electrical Characteristics).

The maximum allowable junction temperature rise  $(\Delta T_J)$  detemperature ( $T_A$ (MAX)) of the application, and the maximum allowable junction temperature ( $T_{J(MAX)}$ ):

$$\Delta T_{\rm J} = T_{\rm J(MAX)} - T_{\rm A(MAX)} \tag{8}$$

The maximum allowable value for junction to ambient Thermal Resistance,  $\theta_{JA}$ , can be calculated using the formula:

$$\theta_{JA} = \Delta T_J / P_{D(MAX)}$$

(9)

LP38512-ADJ is available in TO-263 THIN and PSOP-8 surface mount packages. For a comparison of the TO-263 THIN package to the standard TO-263 package see Application Note *AN-1797 TO-263 THIN Package*. The  $\theta_{JA}$  thermal resistance depends on amount of copper area, or heat sink, attached to the DAP, and on air flow. See Application Note *AN-1520 A Guide to Board Layout for Best Thermal Resistance for Exposed Packages* for guidelines.

#### Heat-Sinking the TO-263 THIN Package

The DAP of the TO-263 THIN package is soldered to the copper plane for heat sinking. The TO-263 THIN package has a  $\theta_{JA}$  rating of 67°C/W, and a  $\theta_{JC}$  rating of 2°C/W. The  $\theta_{JA}$  rating of 67°C/W includes the device DAP soldered to an area of 0.055 square inches (0.22 in x 0.25 in) of 1 ounce copper on a two sided PCB, with no airflow. See JEDEC standard EIA/JESD51-3 for more information.

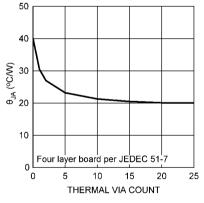

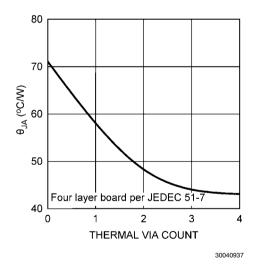

Figure 1 shows a curve for the  $\theta_{JA}$  of TO-263 THIN package for different thermal via counts under the exposed DAP, using a four layer PCB for heat sinking. The thermal vias connect the copper area directly under the exposed DAP to the first internal copper plane only. See JEDEC standards EIA/JESD51-5 and EIA/JESD51-7 for more information.

30040935

# FIGURE 1. $\theta_{JA}$ vs Thermal Via Count for the TO-263 THIN Package on 4–Layer PCB

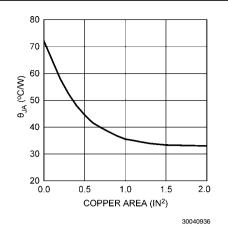

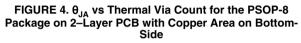

*Figure 2* shows the thermal performance when the Thin TO-263 is mounted to a two layer PCB where the copper area is predominately directly under the exposed DAP.As shown in the figure, increasing the copper area beyond 1 square inch produces very little improvement.

FIGURE 2.  $\theta_{JA}$  vs Copper Area for the TO-263 THIN Package

#### Heat-Sinking The PSOP-8 Package

The DAP of the PSOP-8 package is soldered to the copper plane for heat sinking. The LP38512MR package has a  $\theta_{JA}$  rating of 168°C/W, and a  $\theta_{JC}$  rating of 11°C/W. The  $\theta_{JA}$  rating of 168°C/W includes the device DAP soldered to an area of 0.008 square inches (0.09 in x 0.09 in) of 1 ounce copper on a two sided PCB, with no airflow. See JEDEC standard EIA/ JESD51-3 for more information.

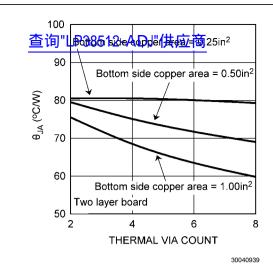

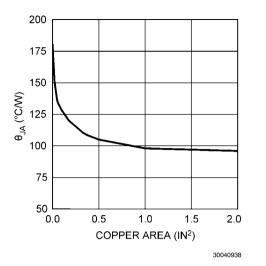

*Figure 3* shows a curve for different thermal via counts under the exposed DAP, using a four layer PCB for heat sinking. The thermal vias connect the copper area directly under the exposed DAP to the first internal copper plane only. See JEDEC standards EIA/JESD51-5 and EIA/JESD51-7 for more information.

#### FIGURE 3. $\theta_{JA}$ vs Thermal Via Count for the PSOP-8 Package on 2–Layer PCB with Copper Area on Bottom-Side

*Figure 4* shows thermal performance for a two layer board using thermal vias to a copper area on the bottom of the PCB. The copper area on the top of the PCB, which is soldered to the exposed DAP, is 0.10in x 0.20in, which is approximately the same dimensions as the body of the PSOP-8 package. The copper area on the bottom of the PCB is a square area and is centered directly under the PSOP-8 package.

*Figure 5* shows thermal performance for a two layer board with the DAP soldered to copper area on the of the PCB only.

Increasing the copper area soldered to the DAP to 1 square inch of 1 ounce copper, using a dog-bone type layout, will produce a typical  $\theta_{JA}$  rating of 98°C/W.

FIGURE 5.  $\theta_{JA}$  vs Copper Area for the PSOP-8 Package on 2–Layer PCB with Copper Area on Top-Side

查询"LP38512-ADJ"供应商

# Notes

LP38512-ADJ

# 查询"LP38512-ADJ"供应商

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools          | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes               | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs       | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                 | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards             | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging               | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance        | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors            | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support        | www.national.com/feedback      |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy        | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions               | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™             | www.national.com/solarmagic    |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | Analog University®      | www.national.com/AU            |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com