# Ľ

# 查询"NJM2207S"供应商

### VIDEO SUPER IMPOSER

### **■** GENERAL DESCRIPTION

The NJM2207 is video signal superimposer, with synchronous separation circuit, vertical sinchronous reproduce circuit and two video high performance switches for switching from video signal to character signal and backgroud signal.

The NJM2207 is suitable for simply indicating the date time, TV channel and others.

#### **■ FEATURES**

Operating Voltage

(+4.75V~+13V)

With Synchronous Separation Circuit

With Vertical Sinchronous Reproduce Circuit

Package Outline

DIP-14, DMP-14, ZIP-16

Bipolar Technology

### ■ RECOMMENDED OPERATING CONDITION

Operating Voltage

4.75~13V

#### **■ PACKAGE OUTLINE**

NJM2207D

NJM2207 S

NJM2207M

### ■ ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER                   | SYMBOL | RATINGS        | UNIT |

|-----------------------------|--------|----------------|------|

| Supply Voltage              | V*     | 17             | V    |

| Power Dissipation           | Po     | (ZIP16) 500    | mW   |

|                             |        | (DIP14) 700    | mW   |

|                             |        | (DMP14) 300    | mW   |

| Operating Temperature Range | Topr   | <b>−40~+85</b> | °C   |

| Storage Temperature Range   | Tstg   | -40~+125       | °C   |

### **■ ELECTRICAL CHARACTERISTICS**

(Ta=25°C, V+=5V)

| PARAMETER         | SYMBOL          | TEST CONDITION | MIN. | TYP. | MAX. | UNIT: |

|-------------------|-----------------|----------------|------|------|------|-------|

| Operating Current | I <sub>cc</sub> |                | _    | 6.5  | 9    | mA    |

Video Signal Processing Section (Video Input  $2V_{pp}$ , Source Resistance=75 $\Omega$ )

| OFF-SET Voltage (Back-ground Input)  | V <sub>BOS</sub> | Cross Voltage In Ext. 10kΩ Resistor        | _   | _    | 0.1      | l v |

|--------------------------------------|------------------|--------------------------------------------|-----|------|----------|-----|

| OFF-SET Voltage (Char. Input)        | V <sub>cos</sub> | Cross Voltage In Ext. 10kΩ Resistor.       | _   | _    | 0.1      | V   |

| OFF-Voltage (Background Cont. Input) | V <sub>BL</sub>  |                                            | _   | _    | 0.4      | V   |

| OFF-Voltage (Char. Cont Input)       | V <sub>CI.</sub> |                                            | -   | _    | 0.4      | v   |

| ON-Voltage (Background Cont. Input)  | VBH              |                                            | 2.0 | _    | _        | V   |

| ON-Voltage (Char. Cont. Input)       | V <sub>CH</sub>  |                                            | 2.0 | _    | _        | v   |

| Transfer Gain                        | G <sub>v</sub>   | $R_L=5k\Omega$                             | 11  | _    | +1       | dB  |

| Frequency Response                   | Gf               | $f=10MHz$ , $R_L=5k\Omega$                 |     | -0.2 | <u> </u> | dB  |

| Crosstalk In Each Signal             | C <sub>T</sub>   | Video Input (f=3.58MHz)                    | _   | 50   |          | İ   |

|                                      |                  | Background Input (f=3.48MHz)               | 1   | l    | 1        | !   |

|                                      |                  | Char. Input (f=3.68MHz)                    |     |      |          | ļ   |

|                                      |                  | Each Signal, is Sine-Wave $R_1 = 5k\Omega$ |     | 1    |          |     |

| Video Differential Phase             | DP               | $R_L=5k\Omega$                             | _   | l –  | 3        | Deg |

| Video Differential Gain              | DG               | $R_L=5k\Omega$                             | _   | _    | 3        | %   |

|                                      |                  |                                            |     | l    |          |     |

# ■ ELECTRICAL CHARACTERISTICS SYNC. SEPARATION SECTION

(Ta=25°C, V⁺=5V)

| PARAMETER                            | SYMBOL              | TEST CONDITION                       | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------|---------------------|--------------------------------------|------|------|------|------|

| *Sync. Sepa. Input Threshold Voltage | V <sub>(SP</sub>    | Source Resistance Rg=75Ω             | 100  | 140  | 180  | mV   |

| H-Sync. High Level                   | V <sub>HH</sub>     | $R_L = 100 k\Omega$ Pin 3 (13)       | 4.0  | _    |      | l v  |

| H-Sync. High Level                   | · V <sub>HH2</sub>  | $R_L = 2.2 k\Omega$ Pin 3 (13)       | 3.6  | 4.1  | _    | v    |

| H-Sync. Low Level                    | VHL                 | $R_L = 2.2k\Omega$ Pin 3 (13)        | _    | _    | 0.1  | V    |

| H-Sync. High Level                   | ViiII               | $R_L = 100 k\Omega$ Pin 4 (14)       | 4.9  | _    | _    | V    |

| H-Sync. Low Level                    | $V_{\overline{H}L}$ | $R_1 = 100 k\Omega$ Pin 4 (14)       |      |      | 0.3  | v    |

| V-Sync.High Level                    | V <sub>VIII</sub>   | $R_L = 100 k\Omega$ Pin 7 (2)        | 4.0  | _    | _    | V    |

| V-Sync. High Level                   | V <sub>VH2</sub>    | $R_1 = 10k\Omega$ Pin 7 (2)          | 3.6  | 4.1  | l _  | v    |

| V-Sync. Low Level                    | V <sub>VL</sub>     | $R_L = 10k\Omega$ Pin 7 (2)          |      | _    | 0.1  | v    |

| V-Sync. High Level                   | $V_{\overline{V}H}$ | $R_L = 100 \text{k}\Omega$ Pin 9 (4) | 4.9  |      |      | l v  |

| V-Sync. Low Level                    | V <sub>VL</sub>     | $R_L = 100 k\Omega$ Pin 9 (4)        | -    | _    | 0.3  | V    |

| Schmitt Trigger                      |                     |                                      | ĺ    |      |      |      |

| Threshold High Level                 | V <sub>VTH</sub>    | Pin 5 Input Voltage (1)              | 1:9  | 2.1  | 2.3  | l v  |

| Threshold Low Level                  | V <sub>VTL</sub>    | Pin 5 Input Voltage (1)              | 1.1  | 1.3  | 1.5  | v    |

(Note): ( ) to DIP-14/DMP-14 \* A version (100mV Typ.)

#### **■ TEST CIRCUIT**

Video (Background SYNC (Com SYNC) Output Control) B(背景入力) VCC2 C(Character Input) +87 SEPA IN VCC1 Vour 100k  $\frac{1}{\mu}$  0.01 $\mu$ **≸**5k 1μ 4.7μ **≥** 100k 5k ≸ 5k  $10\mu$ SWA(2) 733 VIN 45Ω **@** √10k → 2.5 V -∕VV— 10k ≩ 32Ω SWB(1) SWB(2) 0 **→** 0 0 100k ≱ ₹100k **≱**10k O V (V SYNC) (Com SYNC) H O -8V Vyru Character Background

Offset Offset

Check Terminal Check Terminal νc (THRESH INPUT) (V SYNC)

5

### **■ TYPICAL APPLICATION**

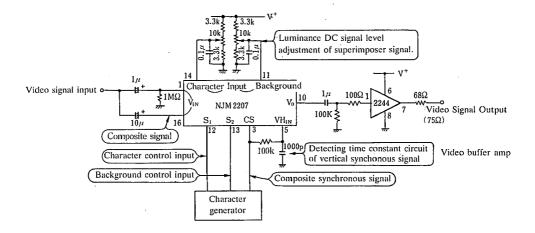

Note 1: Pin Connection to ZIP-16 (Pin 2, Pin 15: NC). ( ) to DIP-14/DMP-14

Note 2: Syn. Sepa. Input Threshold voltage increases 40mV (typ.) when putting  $1M\Omega$  in to Pin 1 (Pin 12).

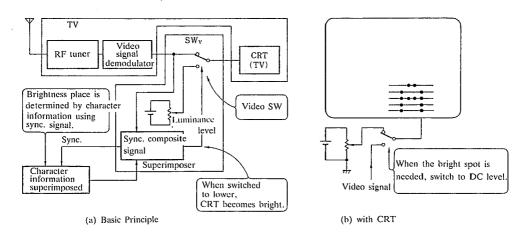

#### ■ PRINCIPLE OF CHARACTER SUPERIMPOSER

Basic principle is shown at Fig. 1.

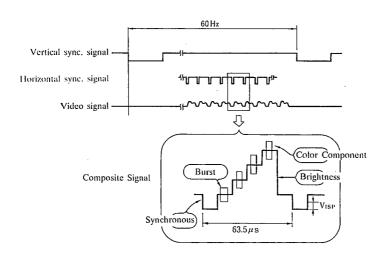

Usual TV has video (composite) signal output and input terminals to connect VCR or others. There is all information about picture on video composite signal (Ref. to Fig. 2). Its time signal of horizontal and vertical synchronous signal indicates the brighten place of TV tube. For brightening TV tube regardless video signal, the video input signal has to be switched to DC level (luminance level) on that scanning time. On this method, character is shown with background of usual picture.

Fig.1 Principle of Character Superimposer

Fig.2 Composite Video Signal

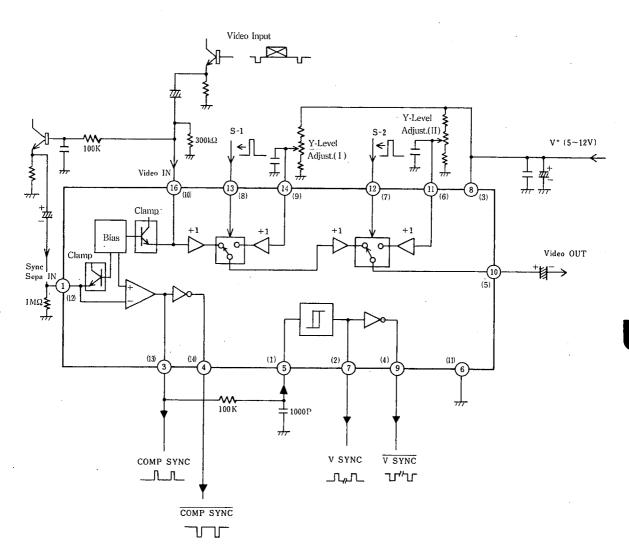

### **■ CIRCUIT CONFIGURATION**

Date superimposer circuit configuration on TV is shown at Fig. 3. The NJM2207 includes video switches which convert, usual video signal (horizontal and vertical synchronous signal, video) to signal, of superimposed character given by character generator.

Fig.3 Typical circuit of date superimposer

# **NJM2207**

查询"NJM2207S"供应商

# **MEMO**

[CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.