2.7V to 11V

1.25 mA

90 ns

120 ns

80 dBc

15 MHz

10 nV/√Hz

-40°C to +125°C

## LMH6618 130 MHz, 1.25 mA Rail-to-Rail Input and Output Operational **Amplifier with Shutdown**

## **General Description**

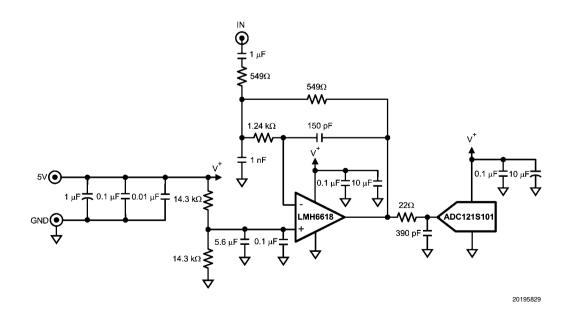

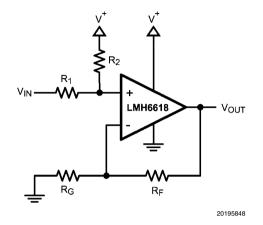

Typical Application

The LMH6618 is a 130 MHz rail-to-rail input and output amplifier designed for ease of use in a wide range of applications requiring high speed. low supply current, low noise, and the ability to drive complex ADC and video loads. The operating voltage range extends from 2.7V to 11V and the supply current is typically 1.25 mA at 5V.

The amplifier's voltage feedback design topology provides balanced inputs and high open loop gain for ease of use and accuracy in applications such as active filter design. Offset voltage is typically 0.1 mV and settling time to 0.01% is 120 ns which combined with an 80 dBc SFDR at 1 MHz makes the part suitable for use as an input buffer for popular 10-bit and 12-bit mega-sample ADCs.

The input common mode range extends 200 mV beyond the supply rails. The output swings to within 270 mV of the supply rails for a 150 $\Omega$  load and 83 mV of the supply rail for a 1 k $\Omega$ load providing true single supply operation and maximum signal dynamic range on low power rails. The amplifier output will source and sink 35 mA and drive up to 15 pF loads without the need for external compensation.

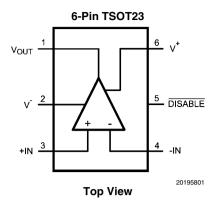

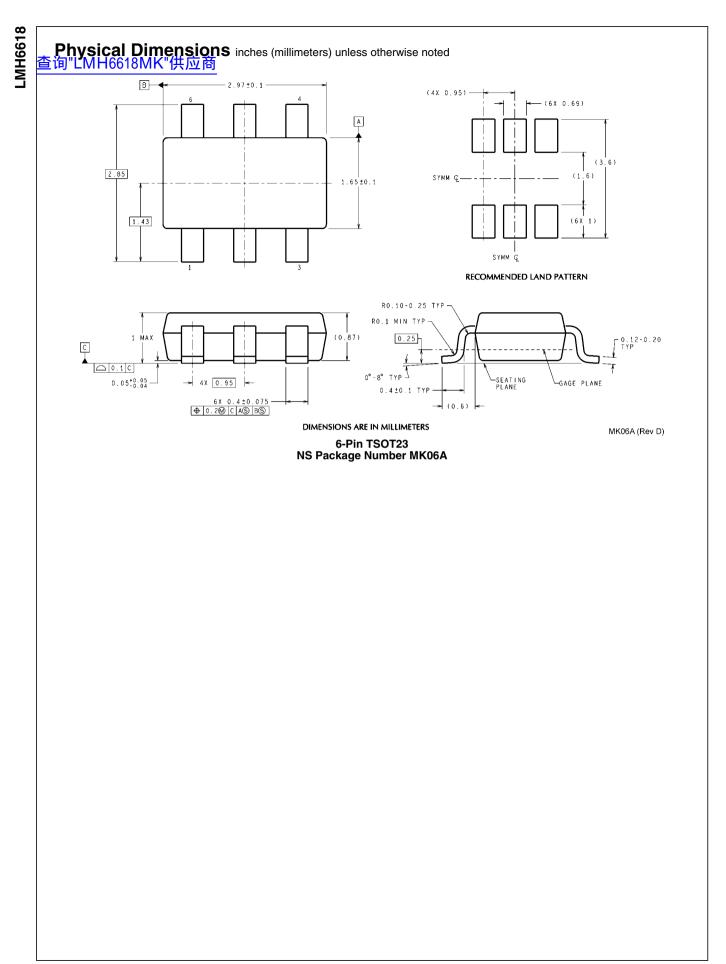

The LMH6618 has an active low disable pin which reduces the supply current to 72 µA and is offered in the space saving 6-Pin TSOT23 package. The LMH6618 is available with a -40°C to +125°C extended industrial temperature grade.

#### **Features**

$V_S = 5V$ ,  $R_I = 1 k\Omega$ ,  $T_A = 25^{\circ}C$  and  $A_V = +1$ , unless otherwise specified.

- Operating voltage range

- Supply current

- 130 MHz -Small signal bandwidth 55 V/µs

- -Slew rate

- Settling time to 0.1%

- Settling time to 0.01%

- SFDR  $(f = 1 \text{ MHz}, A_V = +1, V_{OUT} = 2 V_{PP})$

- 0.1 dB bandwidth ( $A_V = +2$ )

- Low voltage noise

- -Industrial temperature grade

- Rail-to-Rail input and output

## Applications

- ADC driver

- -DAC buffer

- Active filters

- High speed sensor amplifier

- Current sense amplifier

- -Portable video

- -STB, TV video amplifier

WEBENCH® is a registered trademark of National Semiconductor Corporation.

Absolute Maximum Ratings (Note 1)

Distributors for availability and specifications. ESD Tolerance (Note 2)

| LOD TOIETAILCE (NOLE Z) |       |

|-------------------------|-------|

| Human Body Model        |       |

| For input pins only     | 2000V |

| For all other pins      | 2000V |

| Machine Model           | 200V  |

| For all other pins      | 2000V |

## Operating Ratings (Note 1)

| Supply Voltage ( $V_S = V^+ - V^-$ )         | 2.7V to 11V     |

|----------------------------------------------|-----------------|

| Ambient Temperature Range (Note 3)           | -40°C to +125°C |

| Package Thermal Resistance ( $\theta_{JA}$ ) |                 |

| 6-Pin TSOT23                                 | 231°C/W         |

|                                              | 231°C/W         |

+3V Electrical Characteristics Unless otherwise specified, all limits are guaranteed for  $T_J = +25^{\circ}C$ , V<sup>+</sup> = 3V, V<sup>-</sup> = 0V, DISABLE = 3V, V<sub>CM</sub> = V<sub>O</sub> = V<sup>+</sup>/2, A<sub>V</sub> = +1 (R<sub>F</sub> = 0 $\Omega$ ), otherwise R<sub>F</sub> = 2 k $\Omega$  for A<sub>V</sub> ≠ +1, R<sub>L</sub> = 1 k $\Omega$  II 5 pF. Boldface Limits apply at temperature extremes. (Note 4)

| Symbol                         | Parameter                             | Condition                                                                                 | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8)     | Units  |

|--------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------|-----------------|-----------------|---------------------|--------|

| Frequenc                       | y Domain Response                     |                                                                                           | (               | (               | (                   |        |

| SSBW                           | -3 dB Bandwidth Small Signal          | $A_V = 1, R_L = 1 \text{ k}\Omega, V_{OUT} = 0.2 V_{PP}$                                  | 1               | 120             |                     |        |

|                                |                                       | $A_V = 2, -1, R_L = 1 \ k\Omega, V_{OUT} = 0.2 \ V_{PP}$                                  |                 | 56              |                     | MHz    |

| GBW                            | Gain Bandwidth                        | $A_V = 10, R_F = 2 k\Omega, R_G = 221\Omega, R_L = 1 k\Omega,$<br>$V_{OUT} = 0.2 V_{PP}$  | 55              | 71              |                     | MHz    |

| LSBW                           | –3 dB Bandwidth Large Signal          | $A_V = 1, R_L = 1 k\Omega, V_{OUT} = 2 V_{PP}$                                            |                 | 13              |                     |        |

|                                |                                       | $A_V = 2, R_L = 150\Omega, V_{OUT} = 2 V_{PP}$                                            |                 | 13              |                     | MHz    |

| Peak                           | Peaking                               | $A_{V} = 1, C_{L} = 5 \text{ pF}$                                                         |                 | 1.5             |                     | dB     |

| 0.1<br>dBBW                    | 0.1 dB Bandwidth                      | $A_V = 2, V_{OUT} = 0.5 V_{PP},$<br>$R_F = R_G = 825\Omega$                               |                 | 15              |                     | MHz    |

| DG                             | Differential Gain                     | $A_V = +2$ , 4.43 MHz, 0.6V < V <sub>OUT</sub> < 2V,<br>$R_L = 150\Omega$ to V+/2         |                 | 0.1             |                     | %      |

| DP                             | Differential Phase                    | $A_V = +2, 4.43 \text{ MHz}, 0.6V < V_{OUT} < 2V,$<br>$R_L = 150\Omega \text{ to } V^+/2$ |                 | 0.1             |                     | deg    |

| Time Don                       | nain Response                         |                                                                                           |                 |                 |                     |        |

| t <sub>r</sub> /t <sub>f</sub> | Rise & Fall Time                      | 2V Step, A <sub>V</sub> = 1                                                               |                 | 36              |                     | ns     |

| SR                             | Slew Rate                             | 2V Step, A <sub>V</sub> = 1                                                               | 36              | 46              |                     | V/µs   |

| t <sub>s_0.1</sub>             | 0.1% Settling Time                    | 2V Step, $A_V = -1$                                                                       |                 | 90              |                     |        |

| t <sub>s_0.01</sub>            | 0.01% Settling Time                   | 2V Step, $A_V = -1$                                                                       |                 | 120             |                     | ns     |

| Noise and                      | Distortion Performance                |                                                                                           |                 |                 |                     |        |

| SFDR                           | Spurious Free Dynamic Range           | $f_{C} = 100 \text{ kHz}, V_{OUT} = 2 V_{PP}, R_{L} = 1 \text{ k}\Omega$                  |                 | 100             |                     |        |

|                                |                                       | $f_{C}$ = 1 MHz, $V_{OUT}$ = 2 $V_{PP}$ , $R_{L}$ = 1 k $\Omega$                          |                 | 80              |                     | dBc    |

|                                |                                       | $f_{C} = 5 \text{ MHz}, V_{OUT} = 2 V_{PP}, R_{L} = 1 \text{ k}\Omega$                    |                 | 58              |                     |        |

| e <sub>n</sub>                 | Input Voltage Noise                   | f = 100 kHz                                                                               |                 | 10              |                     | nV/√Hz |

| i <sub>n</sub>                 | Input Current Noise                   | f = 100 kHz                                                                               |                 | 1               |                     | pA/√Hz |

| Input, DC                      | Performance                           | •                                                                                         |                 |                 |                     |        |

| V <sub>OS</sub>                | Input Offset Voltage                  | V <sub>CM</sub> = 0.5V (pnp active)<br>V <sub>CM</sub> = 2.5V (npn active)                |                 | 0.1             | ±0.6<br><b>±1.0</b> | mV     |

| TCV <sub>OS</sub>              | Input Offset Voltage Average<br>Drift | (Note 5)                                                                                  |                 | 0.8             |                     | µV/°C  |

| I <sub>B</sub>                 | Input Bias Current                    | V <sub>CM</sub> = 0.5V (pnp active)                                                       |                 | -1.4            | -2.6                | ^      |

|                                |                                       | V <sub>CM</sub> = 2.5V (npn active)                                                       |                 | +1.0            | +1.8                | μA     |

| I <sub>O</sub>                 | Input Offset Current                  |                                                                                           |                 | 0.01            | ±0.27               | μA     |

| C <sub>IN</sub>                | Input Capacitance                     |                                                                                           |                 | 1.5             |                     | pF     |

| R <sub>IN</sub>                | Input Resistance                      |                                                                                           |                 | 8               |                     | MΩ     |

| Symbol           | Parameter<br>查询"LMH6618MK"供应商                      | Condition                                   | Min<br>(Note 8)   | Typ<br>(Note 7) | Max<br>(Note 8)   | Units |

|------------------|----------------------------------------------------|---------------------------------------------|-------------------|-----------------|-------------------|-------|

| CMVR             | Input Voltage Range                                |                                             | -0.2              |                 | 3.2               | V     |

| CMRR             | Common Mode Rejection Ratio                        | V <sub>CM</sub> Stepped from –0.1V to 1.4V  | 78                | 96              |                   | 10    |

|                  |                                                    | V <sub>CM</sub> Stepped from 2.0V to 3.1V   | 81                | 107             |                   | dB    |

| A <sub>OL</sub>  | Open Loop Gain                                     | $R_L = 1 \text{ k}\Omega \text{ to } V^+/2$ |                   | 98              |                   | 10    |

|                  |                                                    | $R_{L} = 150\Omega$ to V+/2                 |                   | 82              |                   | dB    |

| Output D         | C Characteristics                                  |                                             | ŀ                 |                 |                   |       |

| Vo               | Output Swing High<br>(Voltage from V+ Supply Rail) | $R_L = 1 \ k\Omega$ to V+/2                 | 56<br><b>62</b>   | 50              |                   |       |

|                  |                                                    | $R_L$ =150 $\Omega$ to V+/2                 | 172<br><b>198</b> | 160             |                   |       |

|                  | Output Swing Low<br>(Voltage from V- Supply Rail)  | $R_L = 1 \ k\Omega$ to V+/2                 |                   | 60              | 66<br><b>74</b>   | mV    |

|                  |                                                    | $R_L = 150\Omega$ to V+/2                   |                   | 170             | 184<br><b>217</b> |       |

|                  |                                                    | $R_L = 150\Omega$ to V-                     |                   | 29              | 39<br><b>43</b>   |       |

| I <sub>OUT</sub> | Linear Output Current                              | $V_{OUT} = V^{+}/2$ (Note 6)                | ±25               | ±35             |                   | mA    |

| R <sub>o</sub>   | Output Resistance                                  | f = 1 MHz                                   |                   | 0.17            |                   | Ω     |

| Enable P         | in Operation                                       |                                             |                   |                 |                   |       |

|                  | Enable High Voltage Threshold                      | Enabled                                     | 2.0               |                 |                   | V     |

|                  | Enable Pin High Current                            | V <sub>DISABLE</sub> = 3V                   |                   | 0.04            |                   | μA    |

|                  | Enable Low Voltage Threshold                       | Disabled                                    |                   |                 | 1.0               | V     |

|                  | Enable Pin Low Current                             | $V_{\overline{\text{DISABLE}}} = 0V$        |                   | 1               |                   | μA    |

| T <sub>on</sub>  | Turn-On Time                                       |                                             |                   | 25              |                   | ns    |

| T <sub>off</sub> | Turn-Off Time                                      |                                             |                   | 90              |                   | ns    |

| Power Su         | ipply Performance                                  |                                             |                   |                 |                   |       |

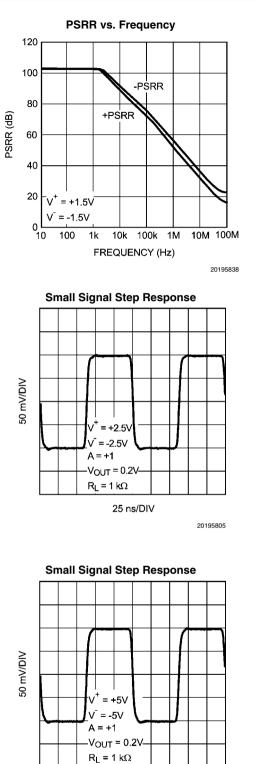

| PSRR             | Power Supply Rejection Ratio                       | DC, $V_{CM} = 0.5V$ , $V_{S} = 2.7V$ to 11V | 84                | 104             |                   | dB    |

| I <sub>S</sub>   | Supply Current                                     | $R_L = \infty$                              |                   | 1.2             | 1.5<br><b>1.7</b> | mA    |

| I <sub>SD</sub>  | Disable Shutdown Current                           | DISABLE = 0V                                |                   | 59              | 85                | μA    |

+5V Electrical Characteristics Unless otherwise specified, all limits are guaranteed for  $T_J = +25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $\overline{DISABLE} = 5V$ ,  $V_{CM} = V_O = V^+/2$ ,  $A_V = +1$  ( $R_F = 0\Omega$ ), otherwise  $R_F = 2 \ k\Omega$  for  $A_V \neq +1$ ,  $R_L = 1 \ k\Omega \parallel 5 \ pF$ . Boldface Limits apply at temperature extremes.

| Symbol    | Parameter                    | Condition                                                                      | Min      | Тур      | Max      | Units |

|-----------|------------------------------|--------------------------------------------------------------------------------|----------|----------|----------|-------|

|           |                              |                                                                                | (Note 8) | (Note 7) | (Note 8) |       |

| Frequence | y Domain Response            |                                                                                |          |          |          |       |

| SSBW      | -3 dB Bandwidth Small Signal | $A_V = 1, R_L = 1 \text{ k}\Omega, V_{OUT} = 0.2 V_{PP}$                       |          | 130      |          | MHz   |

|           |                              | $A_V = 2, -1, R_L = 1 \text{ k}\Omega, V_{OUT} = 0.2 V_{PP}$                   |          | 53       |          | IVIHZ |

| GBW       | Gain Bandwidth               | $A_V = 10, R_F = 2 \text{ k}\Omega, R_G = 221\Omega, R_L = 1 \text{ k}\Omega,$ | 54       | 64       |          | MHz   |

|           |                              | $V_{OUT} = 0.2 V_{PP}$                                                         |          |          |          |       |

| LSBW      | -3 dB Bandwidth Large Signal | $A_V = 1, R_L = 1 \text{ k}\Omega, V_{OUT} = 2 \text{ V}_{PP}$                 |          | 15       |          | N411- |

|           |                              | $A_{V} = 2, R_{L} = 150\Omega, V_{OUT} = 2 V_{PP}$                             |          | 15       |          | MHz   |

| Peak      | Peaking                      | $A_{V} = 1, C_{L} = 5 \text{ pF}$                                              |          | 0.5      |          | dB    |

| 0.1       | 0.1 dB Bandwidth             | $A_V = 2, V_{OUT} = 0.5 V_{PP},$                                               |          | 15       |          | MHz   |

| dBBW      |                              | $R_F = R_G = 1 \ k\Omega$                                                      |          |          |          |       |

| DG        | Differential Gain            | A <sub>V</sub> = +2, 4.43 MHz, 0.6V < V <sub>OUT</sub> < 2V,                   |          | 0.1      |          | %     |

|           |                              | $R_1 = 150\Omega$ to V+/2                                                      |          |          |          |       |

LMH6618

| ω        |

|----------|

| <b>—</b> |

| G        |

| õ        |

| Ŧ        |

| _        |

| 5        |

| 2        |

|          |

| _        |

| Symbol<br>查询"LN                | Parameter<br>/H6618MK"供应商                                | Condition                                                                                | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8)   | Units   |  |

|--------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------|-----------------|-------------------|---------|--|

| DP                             | Differential Phase                                       | A <sub>V</sub> = +2, 4.43 MHz, 0.6V < V <sub>OUT</sub> < 2V,                             |                 | 0.1             |                   | deg     |  |

|                                |                                                          | $R_{L} = 150\Omega$ to V+/2                                                              |                 |                 |                   |         |  |

| Time Do                        | main Response                                            |                                                                                          | •               | •               |                   |         |  |

| t <sub>r</sub> /t <sub>f</sub> | Rise & Fall Time                                         | 2V Step, A <sub>V</sub> = 1                                                              |                 | 30              |                   | ns      |  |

| SR                             | Slew Rate                                                | 2V Step, A <sub>V</sub> = 1                                                              | 44              | 55              |                   | V/µs    |  |

| t <sub>s_0.1</sub>             | 0.1% Settling Time                                       | 2V Step, $A_V = -1$                                                                      |                 | 90              |                   |         |  |

| t <sub>s_0.01</sub>            | 0.01% Settling Time                                      | 2V Step, $A_V = -1$                                                                      |                 | 120             |                   | ns      |  |

| Distortio                      | n and Noise Performance                                  |                                                                                          |                 | •               |                   | 2       |  |

| SFDR                           | Spurious Free Dynamic Range                              | $f_{C} = 100 \text{ kHz}, V_{OUT} = 2 \text{ V}_{PP}, \text{ R}_{L} = 1 \text{ k}\Omega$ |                 | 100             |                   |         |  |

|                                |                                                          | $f_{C} = 1 \text{ MHz}, V_{OUT} = 2 \text{ V}_{PP}, \text{ R}_{L} = 1 \text{ k}\Omega$   |                 | 80              |                   | dBc     |  |

|                                |                                                          | $f_{C} = 5 \text{ MHz}, V_{O} = 2 \text{ V}_{PP}, \text{ R}_{L} = 1 \text{ k}\Omega$     |                 | 58              |                   |         |  |

| e <sub>n</sub>                 | Input Voltage Noise                                      | f = 100 kHz                                                                              |                 | 10              |                   | nV/√H:  |  |

| i <sub>n</sub>                 | Input Current Noise                                      | f = 100 kHz                                                                              |                 | 1               |                   | pA/√H:  |  |

|                                | C Performance                                            |                                                                                          |                 |                 |                   | p p n n |  |

| V <sub>os</sub>                | Input Offset Voltage                                     | V <sub>CM</sub> = 0.5V (pnp active)                                                      | 1               | 0.1             | ±0.6              |         |  |

| 05                             | ,                                                        | $V_{CM} = 4.5V$ (npn active)                                                             |                 |                 | ±1.0              | mV      |  |

| TCV <sub>OS</sub>              | Input Offset Voltage Average                             | (Note 5)                                                                                 |                 | 0.8             |                   | μV/°C   |  |

| 00                             | Drift                                                    |                                                                                          |                 |                 |                   |         |  |

| I <sub>B</sub>                 | Input Bias Current                                       | V <sub>CM</sub> = 0.5V (pnp active)                                                      |                 | -1.5            | -2.4              |         |  |

|                                |                                                          | V <sub>CM</sub> = 4.5V (npn active)                                                      |                 | +1.0            | +1.9              | μA      |  |

| I <sub>o</sub>                 | Input Offset Current                                     |                                                                                          |                 | 0.01            | ±0.26             | μA      |  |

| C <sub>IN</sub>                | Input Capacitance                                        |                                                                                          |                 | 1.5             |                   | pF      |  |

| R <sub>IN</sub>                | Input Resistance                                         |                                                                                          |                 | 8               |                   | MΩ      |  |

| CMVR                           | Input Voltage Range                                      | DC, CMRR ≥ 65 dB                                                                         | -0.2            |                 | 5.2               | V       |  |

| CMRR                           | Common Mode Rejection Ratio                              | V <sub>CM</sub> Stepped from –0.1V to 3.4V                                               | 81              | 98              |                   |         |  |

|                                |                                                          | V <sub>CM</sub> Stepped from 4.0V to 5.1V                                                | 84              | 108             |                   | dB      |  |

| AOL                            | Open Loop Gain                                           | $R_L = 1 \ k\Omega$ to V+/2                                                              |                 | 100             |                   |         |  |

|                                |                                                          | $R_{\rm L} = 150\Omega$ to V+/2                                                          |                 | 83              |                   | dB      |  |

| Output F                       | C Characteristics                                        |                                                                                          |                 |                 |                   |         |  |

| <u> </u>                       | Output Swing High                                        | $R_{I} = 1 k\Omega$ to V+/2                                                              | 73              | 60              |                   |         |  |

| -0                             | (Voltage from V <sup>+</sup> Supply Rail)                |                                                                                          | 82              |                 |                   |         |  |

|                                |                                                          | $R_1 = 150\Omega$ to V+/2                                                                | 255             | 230             |                   |         |  |

|                                |                                                          | -                                                                                        | 295             |                 |                   |         |  |

|                                | Output Swing Low                                         | $R_L = 1 \ k\Omega$ to V+/2                                                              |                 | 75              | 83                | mV      |  |

|                                | (Voltage from V- Supply Rail)                            |                                                                                          |                 | 0.50            | 96                |         |  |

|                                |                                                          | $R_L = 150\Omega$ to V+/2                                                                |                 | 250             | 270<br><b>321</b> |         |  |

|                                |                                                          | $P_{-} = 1500 \text{ to } V_{-}$                                                         |                 | 32              | 43                |         |  |

|                                |                                                          | $R_L = 150\Omega$ to V-                                                                  |                 |                 | 43<br>45          |         |  |

| I <sub>OUT</sub>               | Linear Output Current                                    | V <sub>OUT</sub> = V <sup>+</sup> /2 (Note 6)                                            | ±25             | ±35             |                   | mA      |  |

|                                | Output Resistance                                        | f = 1 MHz                                                                                |                 | 0.17            |                   | Ω       |  |

|                                | Pin Operation                                            | 1                                                                                        |                 |                 | 1                 |         |  |

| -                              | -                                                        | Enabled                                                                                  | 3.0             |                 |                   | V       |  |

| -                              | Enable High Voltage Threshold                            |                                                                                          |                 |                 |                   |         |  |

| -                              | Enable High Voltage Threshold<br>Enable Pin High Current |                                                                                          |                 | 1.2             |                   | μA      |  |

| -                              |                                                          | V <sub>DISABLE</sub> = 5V<br>Disabled                                                    |                 | 1.2             | 2.0               | μA<br>V |  |

| R <sub>O</sub><br>Enable F     | Enable Pin High Current                                  | V <sub>DISABLE</sub> = 5V<br>Disabled                                                    |                 | 1.2<br>2.5      | 2.0               |         |  |

| -                              | Enable Pin High Current<br>Enable Low Voltage Threshold  | V <sub>DISABLE</sub> = 5V                                                                |                 |                 | 2.0               | V       |  |

| Symbol                   | Parameter<br>查询"LMH6618MK"供应函 | Condition                                   | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8)   | Units |  |

|--------------------------|-------------------------------|---------------------------------------------|-----------------|-----------------|-------------------|-------|--|

| Power Supply Performance |                               |                                             |                 |                 |                   |       |  |

| PSRR                     | Power Supply Rejection Ratio  | DC, $V_{CM} = 0.5V$ , $V_{S} = 2.7V$ to 11V | 84              | 104             |                   | dB    |  |

| I <sub>S</sub>           | Supply Current                | $R_L = \infty$                              |                 | 1.25            | 1.5<br><b>1.7</b> | mA    |  |

| I <sub>SD</sub>          | Disable Shutdown Current      | DISABLE = 0V                                |                 | 72              | 105               | μA    |  |

**±5V Electrical Characteristics** Unless otherwise specified, all limits are guaranteed for  $T_J = +25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = -5V$ ,  $\overline{DISABLE} = 5V$ ,  $V_{CM} = V_O = 0V$ ,  $A_V = +1$  ( $R_F = 0\Omega$ ), otherwise  $R_F = 2 \ k\Omega$  for  $A_V \neq +1$ ,  $R_L = 1 \ k\Omega \parallel 5 \ pF$ . Boldface Limits apply at temperature extremes.

| Symbol                         | Parameter                             | Condition                                                                                                     | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8)     | Units  |

|--------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------------|--------|

| Frequenc                       | y Domain Response                     |                                                                                                               | (               | ( /             | (                   |        |

| SSBW                           | -3 dB Bandwidth Small Signal          | $A_{V} = 1, R_{L} = 1 \text{ k}\Omega, V_{OUT} = 0.2 V_{PP}$                                                  |                 | 140             |                     |        |

|                                |                                       | $A_V = 2, -1, R_L = 1 \text{ k}\Omega, V_{OUT} = 0.2 V_{PP}$                                                  |                 | 53              |                     | MHz    |

| GBW                            | Gain Bandwidth                        | $A_{V} = 10, R_{F} = 2 \text{ k}\Omega, R_{G} = 221\Omega, R_{L} = 1 \text{ k}\Omega,$ $V_{OUT} = 0.2 V_{PP}$ | 54              | 65              |                     | MHz    |

| LSBW                           | –3 dB Bandwidth Large Signal          | $A_V = 1$ , $B_L = 1$ k $\Omega$ , $V_{OUT} = 2$ $V_{PP}$                                                     |                 | 16              |                     |        |

|                                |                                       | $A_V = 2, R_L = 150\Omega, V_{OUT} = 2 V_{PP}$                                                                |                 | 15              |                     | MHz    |

| Peak                           | Peaking                               | $A_V = 1, C_L = 5 \text{ pF}$                                                                                 |                 | 0.05            |                     | dB     |

| 0.1<br>dBBW                    | 0.1 dB Bandwidth                      | $A_V = 2, V_{OUT} = 0.5 V_{PP},$<br>$R_F = R_G = 1.21 \text{ k}\Omega$                                        |                 | 15              |                     | MHz    |

| DG                             | Differential Gain                     | $A_V = +2$ , 4.43 MHz, 0.6V < V <sub>OUT</sub> < 2V,<br>R <sub>I</sub> = 150Ω to V+/2                         |                 | 0.1             |                     | %      |

| DP                             | Differential Phase                    | $A_V = +2, 4.43 \text{ MHz}, 0.6V < V_{OUT} < 2V,$<br>$R_L = 150\Omega \text{ to V}^+/2$                      |                 | 0.1             |                     | deg    |

| Time Don                       | nain Response                         |                                                                                                               |                 |                 |                     |        |

| t <sub>r</sub> /t <sub>f</sub> | Rise & Fall Time                      | 2V Step, A <sub>V</sub> = 1                                                                                   |                 | 30              |                     | ns     |

| SR                             | Slew Rate                             | 2V Step, A <sub>V</sub> = 1                                                                                   | 45              | 57              |                     | V/µs   |

| t <sub>s_0.1</sub>             | 0.1% Settling Time                    | 2V Step, $A_V = -1$                                                                                           |                 | 90              |                     | 20     |

| t <sub>s_0.01</sub>            | 0.01% Settling Time                   | 2V Step, $A_V = -1$                                                                                           |                 | 120             |                     | ns     |

| Noise and                      | Distortion Performance                |                                                                                                               |                 |                 |                     |        |

| SFDR                           | Spurious Free Dynamic Range           | $f_{C}$ = 100 kHz, $V_{OUT}$ = 2 $V_{PP}$ , $R_{L}$ = 1 k $\Omega$                                            |                 | 100             |                     |        |

|                                |                                       | $f_{C} = 1 \text{ MHz}, V_{OUT} = 2 \text{ V}_{PP}, \text{ R}_{L} = 1 \text{ k}\Omega$                        |                 | 80              |                     | dBc    |

|                                |                                       | $f_c = 5 \text{ MHz}, V_{OUT} = 2 V_{PP}, R_L = 1 \text{ k}\Omega$                                            |                 | 58              |                     |        |

| e <sub>n</sub>                 | Input Voltage Noise                   | f = 100 kHz                                                                                                   |                 | 10              |                     | nV/√Hz |

| i <sub>n</sub>                 | Input Current Noise                   | f = 100 kHz                                                                                                   |                 | 1               |                     | pA/√Hz |

| Input DC                       | Performance                           |                                                                                                               | ļ               |                 |                     | P. 4 . |

| V <sub>OS</sub>                | Input Offset Voltage                  | $V_{CM} = -4.5V$ (pnp active)<br>$V_{CM} = 4.5V$ (npn active)                                                 |                 | 0.1             | ±0.6<br><b>±1.0</b> | mV     |

| TCV <sub>OS</sub>              | Input Offset Voltage Average<br>Drift | (Note 5)                                                                                                      |                 | 0.9             |                     | µV/°C  |

| I <sub>B</sub>                 | Input Bias Current                    | $V_{CM} = -4.5V$ (pnp active)                                                                                 |                 | -1.5            | -2.4                | ۵      |

|                                |                                       | V <sub>CM</sub> = 4.5V (npn active)                                                                           |                 | +1.0            | +1.9                | μA     |

| I <sub>o</sub>                 | Input Offset Current                  |                                                                                                               |                 | 0.01            | ±0.26               | μA     |

| C <sub>IN</sub>                | Input Capacitance                     |                                                                                                               |                 | 1.5             |                     | pF     |

| R <sub>IN</sub>                | Input Resistance                      |                                                                                                               |                 | 8               |                     | MΩ     |

| CMVR                           | Input Voltage Range                   | DC, CMRR ≥ 65 dB                                                                                              | -5.2            |                 | 5.2                 | V      |

| ω |

|---|

| - |

| G |

| ō |

| I |

| ₹ |

| 4 |

| Symbol<br>≦询"LⅣ  | Parameter<br>H6618MK"供应商                           | Condition                                     | Min<br>(Note 8)   | Typ<br>(Note 7) | Max<br>(Note 8)   | Units |  |

|------------------|----------------------------------------------------|-----------------------------------------------|-------------------|-----------------|-------------------|-------|--|

| CMRR             | Common Mode Rejection Ratio                        | V <sub>CM</sub> Stepped from –5.1V to 3.4V    | 84                | 100             |                   | -10   |  |

|                  |                                                    | V <sub>CM</sub> Stepped from 4.0V to 5.1V     | 83                | 108             |                   | dB    |  |

| A <sub>OL</sub>  | Open Loop Gain                                     | $R_L = 1 \text{ k}\Omega \text{ to } V^+/2$   |                   | 95              |                   |       |  |

|                  |                                                    | $R_{\rm L} = 150\Omega$ to V+/2               |                   | 84              |                   | dB    |  |

| Output D         | C Characteristics                                  |                                               |                   | !               | ·                 |       |  |

| Vo               | Output Swing High<br>(Voltage from V+ Supply Rail) | $R_L = 1 \ k\Omega$ to GND                    | 111<br><b>126</b> | 100             |                   |       |  |

|                  |                                                    | $R_L = 150\Omega$ to GND                      | 457<br><b>526</b> | 430             |                   |       |  |

|                  | Output Swing Low<br>(Voltage from V- Supply Rail)  | $R_L = 1 \ k\Omega$ to GND                    |                   | 110             | 121<br><b>136</b> | mV    |  |

|                  |                                                    | $R_L = 150\Omega$ to GND                      |                   | 440             | 474<br><b>559</b> |       |  |

|                  |                                                    | $R_L = 150\Omega$ to V-                       |                   | 35              | 51<br><b>52</b>   |       |  |

| I <sub>OUT</sub> | Linear Output Current                              | V <sub>OUT</sub> = V <sup>+</sup> /2 (Note 6) | ±25               | ±35             |                   | mA    |  |

| R <sub>o</sub>   | Output Resistance                                  | f = 1 MHz                                     |                   | 0.17            |                   | Ω     |  |

| Enable Pi        | n Operation                                        | •                                             | ·                 | •               |                   |       |  |

|                  | Enable High Voltage Threshold                      | Enabled                                       | 5.5               |                 |                   | V     |  |

|                  | Enable Pin High Current                            | $V_{\overline{\text{DISABLE}}} = +5V$         |                   | 16              |                   | μA    |  |

|                  | Enable Low Voltage Threshold                       | Disabled                                      |                   |                 | 4.5               | V     |  |

|                  | Enable Pin Low Current                             | $V_{\overline{\text{DISABLE}}} = -5V$         |                   | 17              |                   | μA    |  |

| T <sub>on</sub>  | Turn-On Time                                       |                                               |                   | 25              |                   | ns    |  |

| T <sub>off</sub> | Turn-Off Time                                      |                                               |                   | 90              |                   | ns    |  |

| Power Su         | pply Performance                                   |                                               |                   |                 |                   |       |  |

| PSRR             | Power Supply Rejection Ratio                       | DC, $V_{CM} = -4.5V$ , $V_{S} = 2.7V$ to 11V  | 84                | 104             |                   | dB    |  |

| S                | Supply Current                                     | $R_L = \infty$                                |                   | 1.35            | 1.6<br><b>1.9</b> | mA    |  |

| SD               | Disable Shutdown Current                           | $\overline{\text{DISABLE}} = -5V$             |                   | 103             | 140               | μA    |  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics. Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)

Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

Note 3: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

**Note 4:** Boldface limits apply to temperature range of  $-40^{\circ}$ C to  $125^{\circ}$ C

Note 5: Voltage average drift is determined by dividing the change in  $V_{OS}$  by temperature change.

Note 6: Do not short circuit the output. Continuous source or sink currents larger than the IOUT typical are not recommended as it may damage the part.

Note 7: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 8: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlations using the Statistical Quality Control (SQC) method.

LMH6618

## Congention-Diagwam洪应商

## **Ordering Information**

| Package      | Part Number | Package Marking | Transport Media        | NSC Drawing |

|--------------|-------------|-----------------|------------------------|-------------|

|              | LMH6618MK   |                 | 1k Units Tape and Reel | MK06A       |

| 6-Pin TSOT23 | LMH6618MKX  | AE4A            | 3k Units Tape and Reel | IVINUOA     |

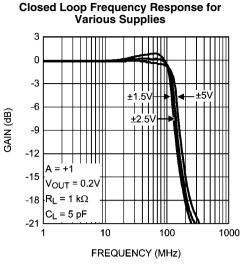

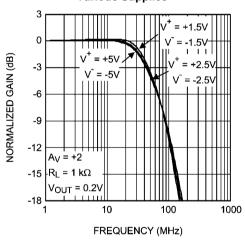

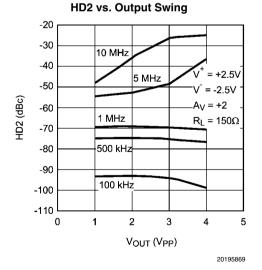

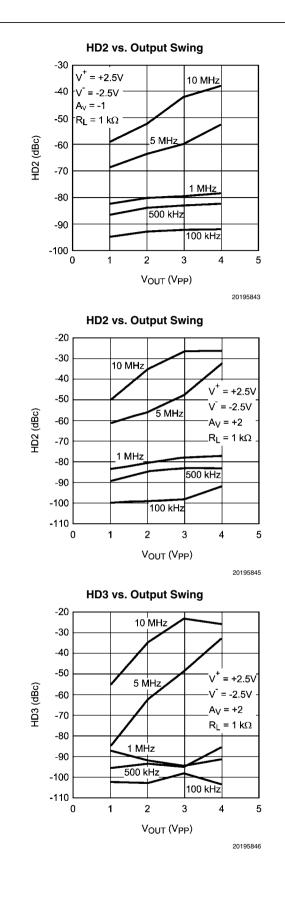

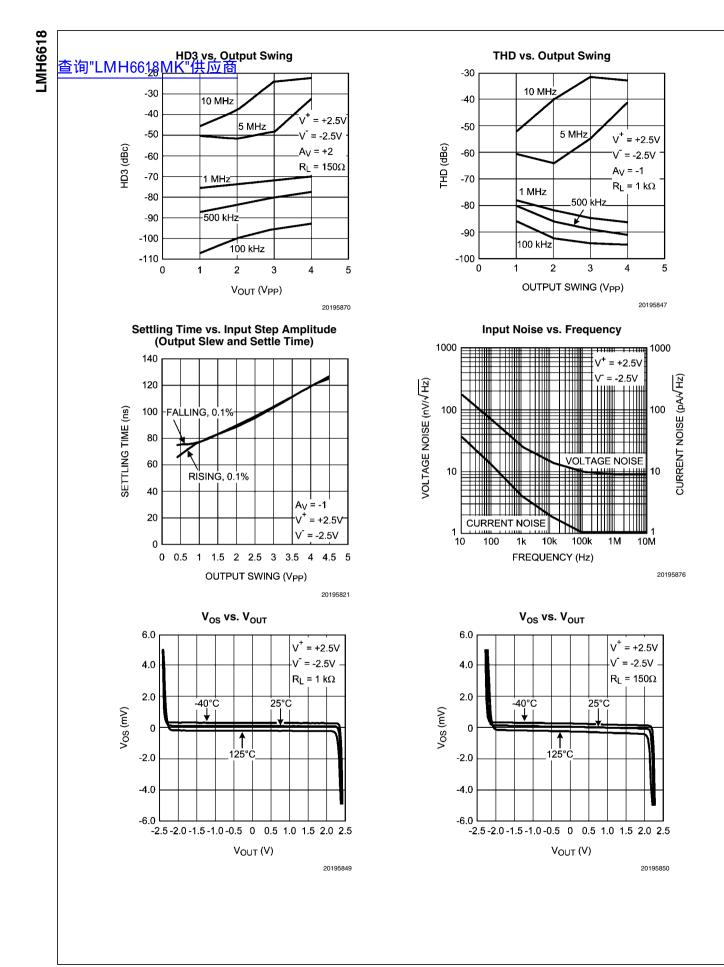

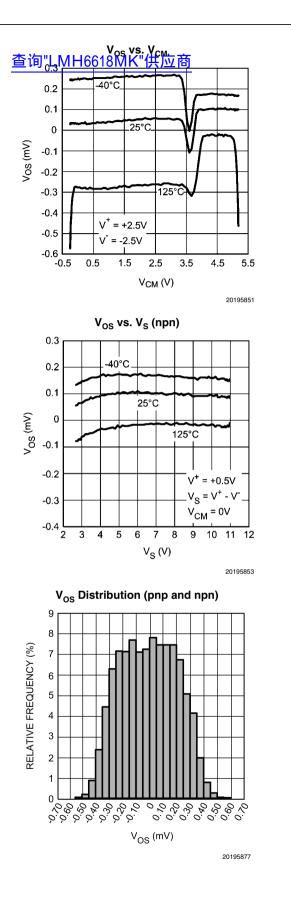

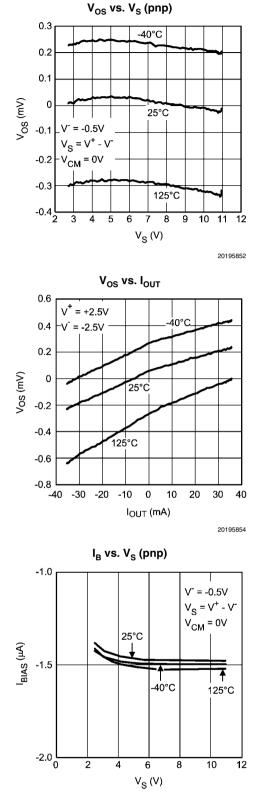

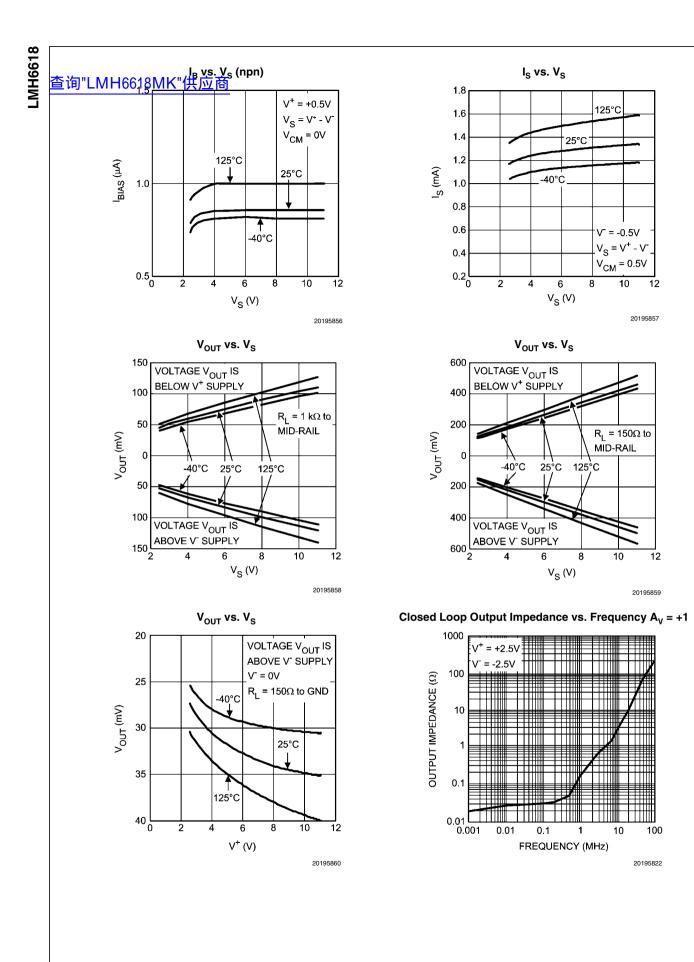

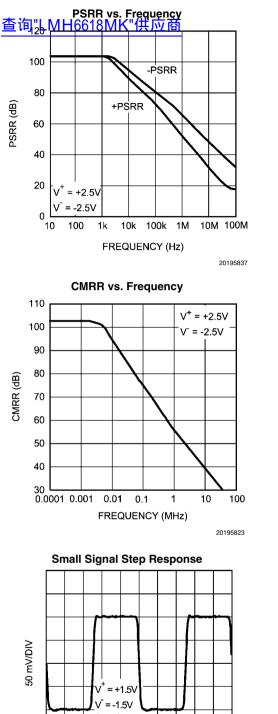

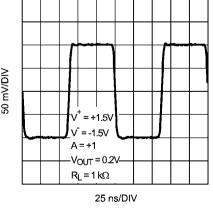

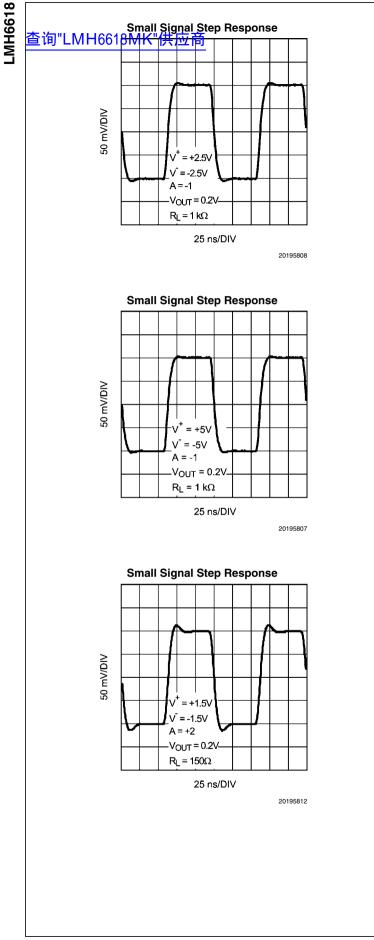

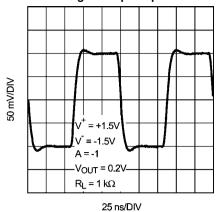

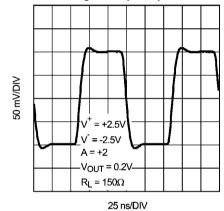

# **Typical Performance Characteristics** At T<sub>J</sub> = 25°C, A<sub>V</sub> = +1 (R<sub>F</sub> = 0Ω), otherwise R<sub>F</sub> = 2 kΩ for A<sub>V</sub> ≠ +1, 冒询啮蛤幼hengites协会前的应商

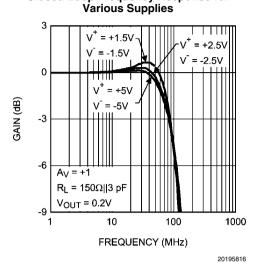

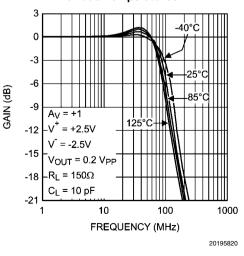

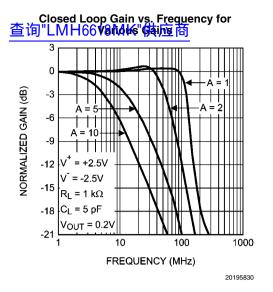

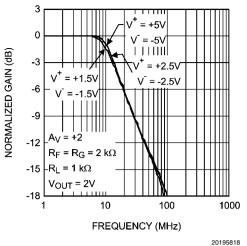

**Closed Loop Frequency Response for**

20195831

**Closed Loop Frequency Response for** Various Supplies

20195815

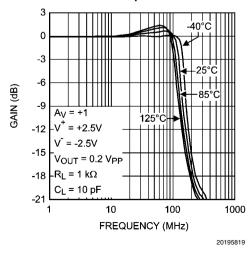

**Closed Loop Frequency Response for** Various Temperatures

**Closed Loop Frequency Response for** Various Temperatures

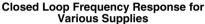

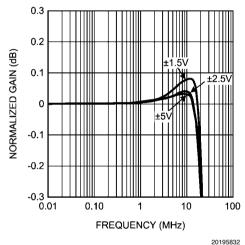

±0.1 dB Gain Flatness for Various Supplies

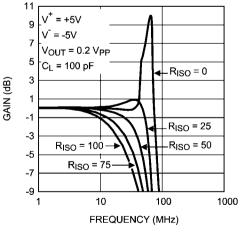

Small Signal Frequency Response with Capacitive Load and Various R<sub>ISO</sub>

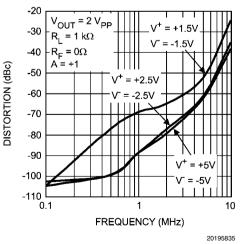

Large Signal Frequency Response

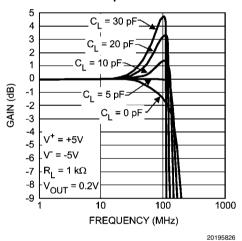

**Small Signal Frequency Response with** Various Capacitive Load

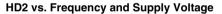

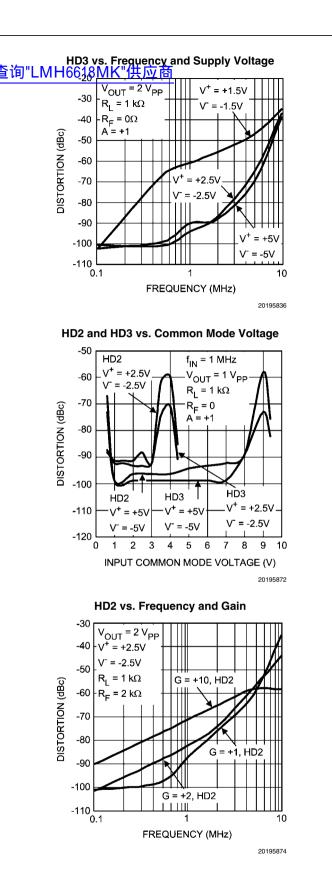

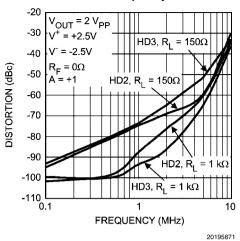

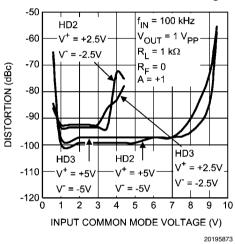

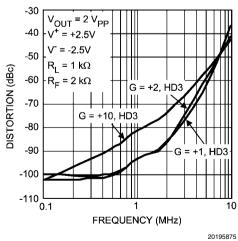

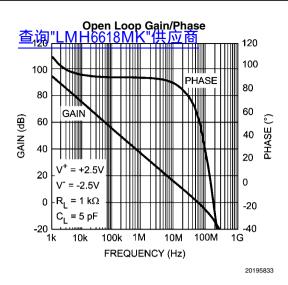

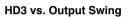

HD2 and HD3 vs. Frequency and Load

HD2 and HD3 vs. Common Mode Voltage

25 ns/DIV

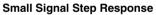

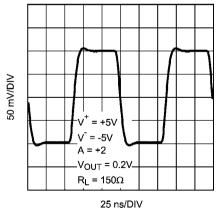

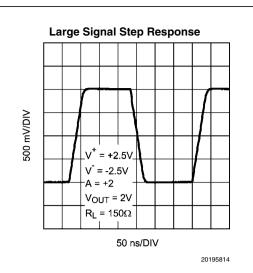

**Small Signal Step Response**

**Small Signal Step Response**

20195811

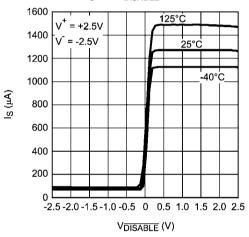

I<sub>S</sub> vs. V<sub>disable</sub>

## Application Information

道"LMH6618MK"(共应商 the LMH6618 is based on National Semiconductor's proprietary VIP10 dielectrically isolated bipolar process. This device family architecture features the following:

- Complimentary bipolar devices with exceptionally high f<sub>t</sub> (~8GHz) even under low supply voltage (2.7V) and low bias current.

- Common emitter push-push output stage. This architecture allows the output to reach within millivolts of either supply rail.

- Consistent performance from any supply voltage (2.7V -11V) with little variation with supply voltage for the most important specifications (e.g. BW, SR, I<sub>OUT</sub>.)

- Significant power saving compared to competitive devices on the market with similar performance.

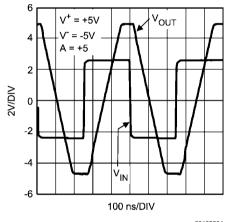

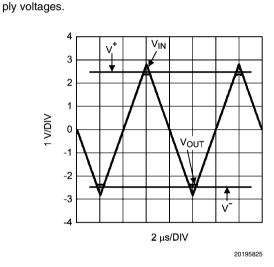

With 3V supplies and a common mode input voltage range that extends beyond either supply rail, the LMH6618 is well suited to many low voltage/low power applications. Even with 3V supplies, the -3 dB BW (at  $A_V = +1$ ) is typically 120 MHz. The LMH6618 is designed to avoid output phase reversal. With input over-drive, the output is kept near the supply rail (or as close to it as mandated by the closed loop gain setting and the input voltage). *Figure 1* shows the input and output voltage when the input voltage significantly exceeds the sup-

#### FIGURE 1. Input and Output Shown with CMVR Exceeded

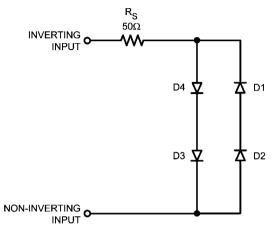

If the input voltage range is exceeded by more than a diode drop beyond either rail, the internal ESD protection diodes will start to conduct. The current flow in these ESD diodes should be externally limited.

The LMH6618 can be shutdown by connecting the  $\overline{\text{DISABLE}}$  pin to a voltage 0.5V below the supply midpoint

which will reduce the supply current to typically less than 100  $\mu$ A. The DISABLE pin is "active low" and should be connected through a resistor to V<sup>+</sup> for normal operation. Shutdown is guaranteed when the DISABLE pin is 0.5V below the supply midpoint at any operating supply voltage and temperature. In the shutdown mode, essentially all internal device biasing is turned off in order to minimize supply current flow and the output goes into high impedance mode. During shutdown, the input stage has an equivalent circuit as shown in *Figure 2*.

20195839

#### FIGURE 2. Input Equivalent Circuit During Shutdown

When the LMH6618 is shutdown, there may be current flow through the internal diodes shown, caused by input potential, if present. This current may flow through the external feedback resistor and result in an apparent output signal. In most shutdown applications the presence of this output is inconsequential. However, if the output is "forced" by another device, the other device will need to conduct the current described in order to maintain the output potential.

To keep the output at or near ground during shutdown when there is no other device to hold the output low, a switch using a transistor can be used to shunt the output to ground.

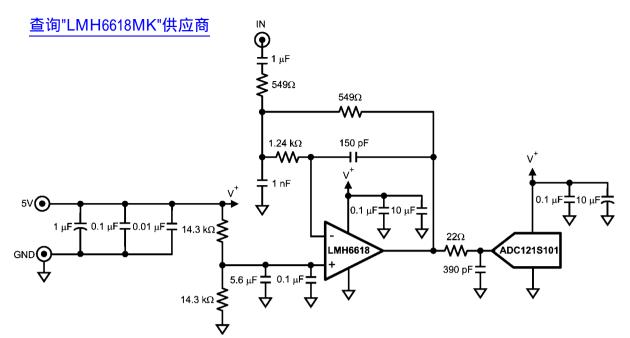

#### SINGLE CHANNEL ADC DRIVER

The low noise and wide bandwidth make the LMH6618 an excellent choice for driving a 12-bit ADC. *Figure 3* shows the schematic of the LMH6618 driving an ADC121S101. The AD-C121S101 is a single channel 12-bit ADC. The LMH6618 is set up in a 2nd order multiple-feedback configuration with a gain of -1. The -3 db point is at 500 kHz and the -0.01 dB point is at 100 kHz. *Table 1* shows the performance data of the LMH6618 and the ADC121S101.

#### FIGURE 3. LMH6618 Driving an ADC121S101

#### TABLE 1. Performance Data for the LMH6618 Driving an ADC121S101

| Parameter        | Measured Value |  |

|------------------|----------------|--|

| Signal Frequency | 100 kHz        |  |

| Signal Amplitude | 4.5V           |  |

| SINAD            | 71.5 dB        |  |

| SNR              | 71.87 dB       |  |

| THD              | -82.4 dB       |  |

| SFDR             | 90.97 dB       |  |

| ENOB             | 11.6 bits      |  |

When the op amp and the ADC are using the same supply, it is important that both devices are well bypassed. A 0.1  $\mu F$  ceramic capacitor and a 10  $\mu F$  tantalum capacitor should be located as close as possible to each supply pin. A sample

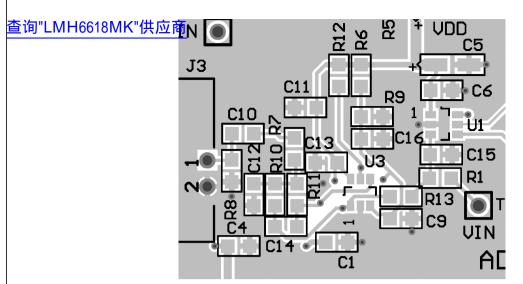

layout is shown in *Figure 4*. The 0.1  $\mu$ F capacitors (C13 and C6) and the 10  $\mu$ F capacitors (C11 and C5) are located very close to the supply pins of the LMH6618 and the AD-C121S101.

LMH6618

20195840

FIGURE 4. LMH6618 and ADC121S101 Layout

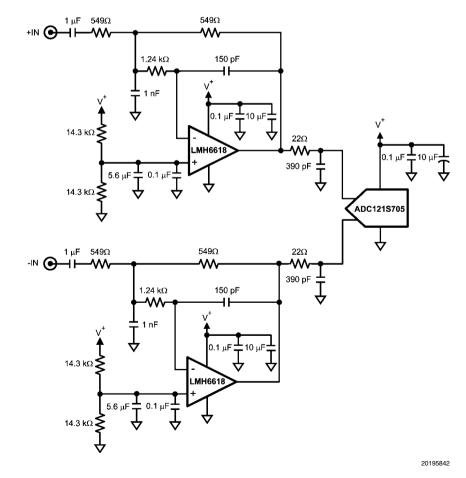

#### DIFFERENTIAL ADC DRIVER

The circuit in *Figure 3* can be used to drive both inputs of a differential ADC. *Figure 5* shows the LMH6618 driving an AD-

C121S705. The ADC121S705 is a fully differential 12-bit ADC. Performance with this circuit is similar to the circuit in *Figure 3*.

FIGURE 5. LMH6618 Driving an ADC121S705

#### DC LEVEL SHIFTING

Often 查该的 Inv++66648小和 (快运运营) evel shifted while using a single supply for the op amp. The circuit in *Figure 6* can do both of these tasks. The procedure for specifying the resistor values is as follows.

- 1. Determine the input voltage.

- 2. Calculate the input voltage midpoint,  $V_{INMID} = V_{INMIN} + (V_{INMAX} V_{INMIN})/2$ .

- 3. Determine the output voltage needed.

- 4. Calculate the output voltage midpoint,  $V_{OUTMID} = V_{OUTMIN} + (V_{OUTMAX} V_{OUTMIN})/2$ .

- 5. Calculate the gain needed, gain = (V\_{OUTMAX} V\_{OUTMIN})/ (V\_{INMAX} V\_{INMIN})

- 6. Calculate the amount the voltage needs to be shifted from input to output,  $\Delta V_{OUT} = V_{OUTMID} \text{gain x } V_{INMID}$ .

- 7. Set the supply voltage to be used.

- 8. Calculate the noise gain, noise gain = gain +  $\Delta V_{OUT}/V_S$ .

- 9. Set R<sub>F</sub>.

- 10. Calculate  $R_1$ ,  $R_1 = R_F$ /gain.

- 11. Calculate  $R_2$ ,  $R_2 = R_F/(noise gain-gain)$ .

- 12. Calculate  $R_G$ ,  $R_G = R_F/(noise gain 1)$ .

Check that both the  $\rm V_{\rm IN}$  and  $\rm V_{\rm OUT}$  are within the voltage ranges of the LMH6618.

- The following example is for a  $\rm V_{IN}$  of 0V to 1V with a  $\rm V_{OUT}$  of 2V to 4V.

- 1.  $V_{IN} = 0V$  to 1V.

- 2.  $V_{INMID} = 0V + (1V 0V)/2 = 0.5V.$

- 3.  $V_{OUT} = 2V \text{ to } 4V.$

- 4.  $V_{OUTMID} = 2V + (4V 2V)/2 = 3V.$

- 5. Gain = (4V 2V)/(1V 0V) = 2

- 6.  $\Delta V_{OUT} = 3V 2 \times 0.5V = 2.$

- 7. For the example the supply voltage will be +5V.

- 8. Noise gain = 2 + 2/5V = 2.4.

- 9.  $R_F = 2 k\Omega$

- 10.  $R_1 = 2 k\Omega/2 = 1 k\Omega$

- 11.  $R_2 = 2 k\Omega/(2.4-2) = 5 k\Omega$ .

- 12.  $R_G = 2 k\Omega/(2.4 1) = 1.43 k\Omega$ .

FIGURE 6. DC Level Shifting

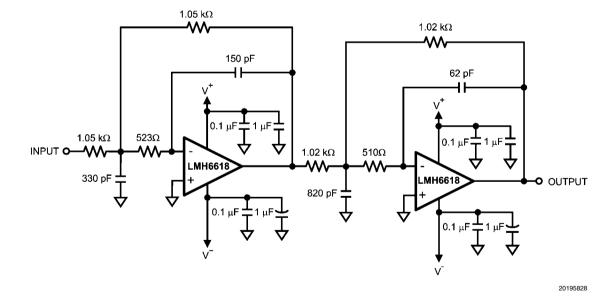

#### 4th ORDER MULTIPLE FEEDBACK LOW-PASS FILTER

*Figure 7* shows the LMH6618 used as the amplifier in a multiple feedback low-pass filter. This filter is set up to have a gain of +1 and a -3 dB point of 1 MHz. Values can be determined by using the WEBENCH® Active Filter Designer found at amplifiers.national.com.

FIGURE 7. 4th Order Multiple Feedback Low-Pass Filter

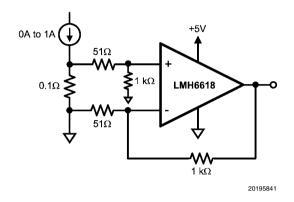

#### CURRENT SENSE AMPLIFIER

With its raises and the term of term of the term of term of term of term of the term of the term of term of term of term of the term of term of term of term of the term of term of term of the term of term

FIGURE 8. Current Sense Amplifier

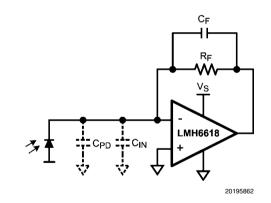

#### TRANSIMPEDANCE AMPLIFIER

By definition, a photodiode produces either a current or voltage output from exposure to a light source. A Transimpedance Amplifier (TIA) is utilized to convert this low-level current to a usable voltage signal. The TIA often will need to be compensated to insure proper operation.

#### FIGURE 9. Photodiode Modeled with Capacitance Elements

*Figure 9* shows the LMH6618 modeled with photodiode and the internal op amp capacitances. The LMH6618 allows circuit operation of a low intensity light due to its low input bias current by using larger values of gain (R<sub>F</sub>). The total capacitance (C<sub>T</sub>) on the inverting terminal of the op amp includes the photodiode capacitance (C<sub>PD</sub>) and the input capacitance of the op amp (C<sub>IN</sub>). This total capacitance (C<sub>T</sub>) plays an important role in the stability of the circuit. The noise gain of this circuit determines the stability and is defined by:

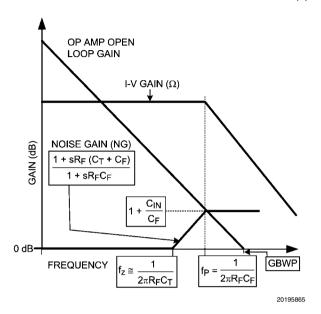

$$NG = \frac{1 + sR_F (C_T + C_F)}{1 + sC_FR_F}$$

(1)

Where,

$$f_Z \cong \frac{1}{2\pi R_F C_T}$$

and  $f_P = \frac{1}{2\pi R_F C_F}$  (2)

#### FIGURE 10. Bode Plot of Noise Gain Intersecting with Op Amp Open-Loop Gain

*Figure 10* shows the bode plot of the noise gain intersecting the op amp open loop gain. With larger values of gain,  $C_T$  and  $R_F$  create a zero in the transfer function. At higher frequencies the circuit can become unstable due to excess phase shift around the loop.

A pole at  $f_P$  in the noise gain function is created by placing a feedback capacitor ( $C_P$ ) across  $R_F$ . The noise gain slope is flattened by choosing an appropriate value of  $C_F$  for optimum performance.

Theoretical expressions for calculating the optimum value of  $C_F$  and the expected -3 dB bandwidth are:

$$C_{\rm F} = \sqrt{\frac{C_{\rm T}}{2\pi R_{\rm F}(\rm GBWP)}}$$

(3)

$$f_{-3 dB} = \sqrt{\frac{GBWP}{2\pi R_F C_T}}$$

(4)

*Equation 4* indicates that the -3 dB bandwidth of the TIA is inversely proportional to the feedback resistor. Therefore, if the bandwidth is important then the best approach would be to have a moderate transimpedance gain stage followed by a broadband voltage gain stage.

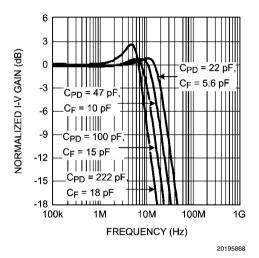

Table 2 shows the measurement results of the LMH6618 with different photodiodes having various capacitances ( $C_{PD}$ ) and a feedback resistance ( $R_{E}$ ) of 1 k $\Omega$ .

|      |      | 6    | Cruera | fanau              | formura               | Peaking |

|------|------|------|--------|--------------------|-----------------------|---------|

| (pF) | (pF) | (pF) | (pF)   | -3 dB CAL<br>(MHz) | ' -3 dB MEAS<br>(MHz) | (dB)    |

| 22   | 24   | 7.7  | 5.6    | 23.7               | 20                    | 0.9     |

| 47   | 49   | 10.9 | 10     | 16.6               | 15.2                  | 0.8     |

| 100  | 102  | 15.8 | 15     | 11.5               | 10.8                  | 0.9     |

| 222  | 224  | 23.4 | 18     | 7.81               | 8                     | 2.9     |

#### 查询"I MH6618MK"在员器 (Figure 1) Compensation and Performance Results

Note:

GBWP = 65 MHz  $C_T = C_{PD} + C_{IN}$   $C_{IN} = 2 \text{ pF}$   $V_S = \pm 2.5 \text{ V}$

*Figure 11* shows the frequency response for the various photodiodes in *Table 2*.

portant to note that the various noise sources (i.e. op amp noise voltage, feedback resistor thermal noise, input noise current, photodiode noise current) do not all operate over the same frequency band. Therefore, when the noise at the output is calculated, this should be taken into account. The op amp noise voltage will be gained up in the region between the noise gain's zero and pole ( $f_z$  and  $f_p$  in *Figure 10*). The higher the values of  $R_F$  and  $C_T$ , the sooner the noise gain peaking starts and therefore its contribution to the total output noise will be larger. It is obvious to note that it is advantageous to minimize  $C_{IN}$  by proper choice of op amp or by applying a reverse bias across the diode at the expense of excess dark current and noise.

When analyzing the noise at the output of the TIA, it is im-

FIGURE 11. Frequency Response for Various Photodiode and Feedback Capacitors

查询"LMH6618MK"供应商

# Notes

LMH6618

查询"LMH6618MK"供应商

## Notes

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tei: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560