# Am2841/3341/2841A

64 x 4 First-In First-Out Memories

查询"3341ADC"供应商

## Distinctive Characteristics

- Plug-In replacement for Fairchild 3341

- Asynchronous buffer for up to 64 four-bit words

- Easily expandable to larger buffers

- Am2841 has 1 MHz guaranteed data rate

- Am2841A has 1.2 MHz guaranteed data rate

- 100% reliability assurance testing in compliance with MIL-STD-883

- Special input circuit provides true TTL compatibility

## FUNCTIONAL DESCRIPTION

The Am3341/Am2841/Am2841A is an asynchronous first-in first-out memory stack, organized as 64 four-bit words. The device accepts a four-bit parallel word  $D_0$ – $D_3$  under control of the shift in (SI) input. Data entered into the FIFO immediately ripples through the device to the outputs  $Q_0$ – $Q_3$ . Up to 64 words may be entered before any words are read from the memory. The stored words line up at the output end in the order in which they were written. A read command on the shift out input (SO) causes the next to the last word of data to move to the output and all data shifts one place down the stack. Input ready (IR) and output ready (OR) signals act as memory full and memory empty flags and also provide the necessary pulses for interconnecting FIFOs to obtain deeper stacks.

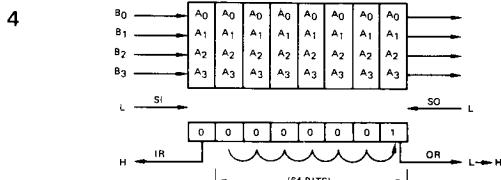

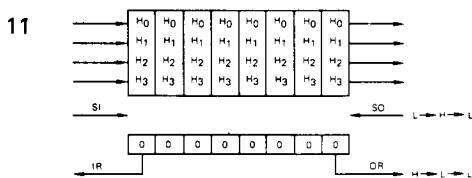

Parallel expansion to wider words only requires that rows of FIFOs be placed side by side.

Reading and writing operations are completely independent, so the device can be used as a buffer between two digital machines operating asynchronously and at widely differing clock rates. Special input circuits are provided on all inputs to pull the input signals up to an MOS  $V_{IH}$  when a TTL  $V_{OH}$  is reached, providing true TTL compatibility without the inconvenience and extra power drain of external pull-up resistors. A detailed description of the operation is on pages 4 and 5 of this data sheet. The Am2841 and Am2841A are functionally identical to the Am3341, but are higher performance devices.

6

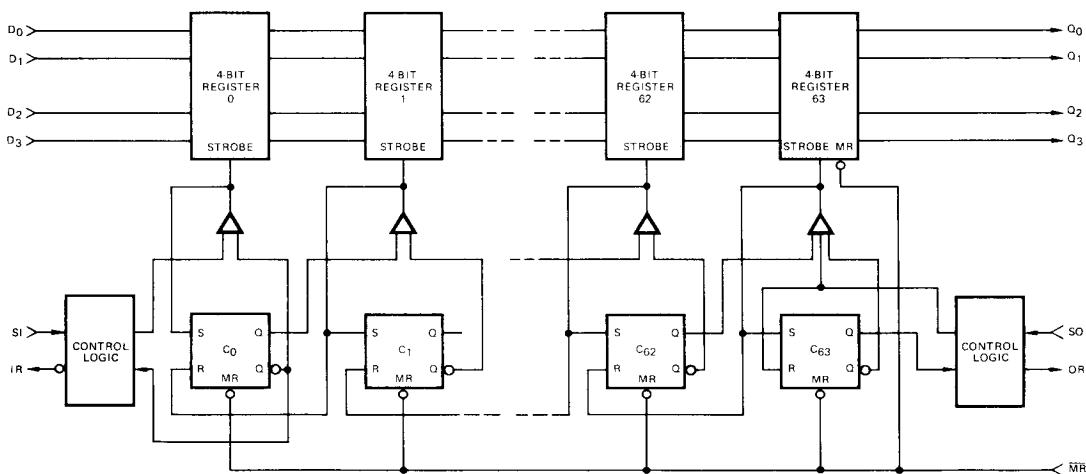

## LOGIC BLOCK DIAGRAM

MOS-469

## ORDERING INFORMATION

| Package Type | Temperature Range | Am3341 Order Number | Am2841 Order Number | Am2841A Order Number |

|--------------|-------------------|---------------------|---------------------|----------------------|

| Molded DIP   | 0°C to +70°C      | AM3341PC            | AM2841PC            | AM2841APC            |

| Hermetic DIP | 0°C to +70°C      | AM3341DC            | AM2841DC            | AM2841ADC            |

| Hermetic DIP | -55°C to +125°C   |                     | AM2841DM            |                      |

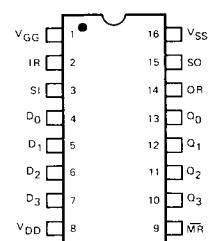

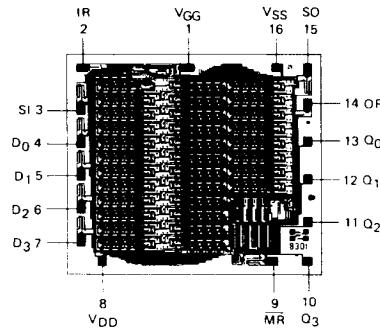

## CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

MOS-470

## MAXIMUM RATING (Above which the useful life may be impaired)

|                                  |                                               |  |  |  |

|----------------------------------|-----------------------------------------------|--|--|--|

| Storage Temperature              | -65°C to +150°C                               |  |  |  |

| Temperature (Ambient) Under Bias | -55°C to +125°C                               |  |  |  |

| V <sub>DD</sub> Supply Voltage   | V <sub>SS</sub> -7V to V <sub>SS</sub> +0.3V  |  |  |  |

| V <sub>GG</sub> Supply Voltage   | V <sub>SS</sub> -20V to V <sub>SS</sub> +0.3V |  |  |  |

| DC Input Voltage                 | V <sub>SS</sub> -10V to V <sub>SS</sub> +0.3V |  |  |  |

查询3341ADC"供应商

## OPERATING RANGE

| Part No.      | Ambient Temperature | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>GG</sub> |

|---------------|---------------------|-----------------|-----------------|-----------------|

| Am3341PC, DC  | 0°C to +70°C        | +5.0 ±5%        | GND             | -12.0 ±5%       |

| Am2841PC, DC  |                     |                 |                 |                 |

| Am2841APC, DC |                     |                 |                 |                 |

| Am2841DM      | -55°C to +125°C     | +5.0 ±5%        | GND             | -12.0 ±5%       |

## ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted)

| Parameters       | Description                      | Conditions                              |                        | Min.                 | Typ. (Note 1) | Max.                 | Units |

|------------------|----------------------------------|-----------------------------------------|------------------------|----------------------|---------------|----------------------|-------|

| V <sub>OH</sub>  | Output HIGH Voltage              | I <sub>OH</sub> = .300mA                |                        | V <sub>SS</sub> -1.0 |               |                      | Volts |

| V <sub>OL</sub>  | Output LOW Voltage               | I <sub>OL</sub> = 1.6 mA                |                        |                      |               | 0.4                  | Volts |

| V <sub>IH</sub>  | Input HIGH Level                 |                                         |                        | V <sub>SS</sub> -1.0 |               |                      | Volts |

| V <sub>IL</sub>  | Input LOW Level                  |                                         |                        |                      |               | 0.8                  | Volts |

| I <sub>IL</sub>  | Input Leakage Current            | V <sub>IN</sub> = 0V                    |                        |                      |               | 1.0                  | μA    |

| I <sub>IH</sub>  | Input HIGH Current               | V <sub>IN</sub> = V <sub>SS</sub> -1.0V |                        | 250                  |               |                      | μA    |

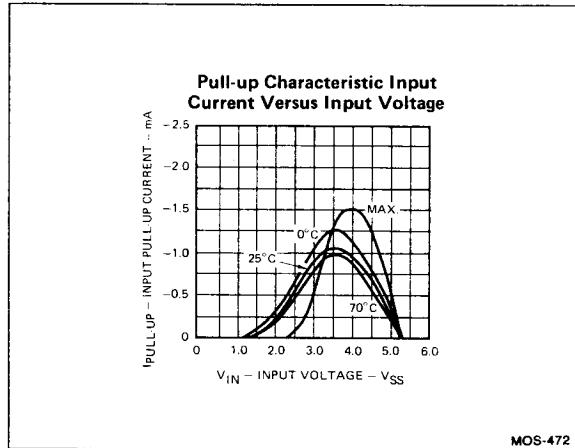

| V <sub>PUP</sub> | Input Pull-up Initiation Voltage | (Note 2)                                | V <sub>SS</sub> = MIN. |                      |               | 2.0                  | Volts |

|                  |                                  |                                         | V <sub>SS</sub> = MAX. |                      |               | 2.2                  | Volts |

| V <sub>BAR</sub> | Voltage at Peak Input Current    | (Note 2)                                |                        |                      |               | V <sub>SS</sub> -1.5 | Volts |

| I <sub>BAR</sub> | Maximum Input Current            | (Note 2)                                |                        |                      |               | 1.6                  | mA    |

| I <sub>GG</sub>  | V <sub>GG</sub> Current          | T <sub>A</sub> = 0°C to +70°C           |                        |                      | 7             | 12                   | mA    |

|                  |                                  | T <sub>A</sub> = -55°C to +125°C        |                        |                      |               | 16                   | mA    |

| I <sub>DD</sub>  | V <sub>DD</sub> Current          | T <sub>A</sub> = 0°C to +70°C           |                        |                      | 30            | 45                   | mA    |

|                  |                                  | T <sub>A</sub> = -55°C to +125°C        |                        |                      |               | 60                   | mA    |

Notes: 1. Typical limits are at V<sub>SS</sub> = 5.0V, V<sub>GG</sub> = -12.0V, T<sub>A</sub> = 25°C

2. See graph of input V-I characteristics.

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted)

| Parameters       | Definition                       | Test Conditions | Am3341 |      |      | Am2841 |      |      | Am2841A |      |      |

|------------------|----------------------------------|-----------------|--------|------|------|--------|------|------|---------|------|------|

|                  |                                  |                 | Min.   | Typ. | Max. | Min.   | Typ. | Max. | Min.    | Typ. | Max. |

| f <sub>max</sub> | Maximum SI or SO Frequency       |                 | 0.75   |      |      | 1.0    |      |      | 1.2     |      |      |

| t <sub>IR+</sub> | Delay, SI HIGH to IR LOW         |                 | 90     | 250  | 550  | 80     |      | 400  | 80      |      | 350  |

| t <sub>IR-</sub> | Delay, SI LOW to IR HIGH         |                 | 138    | 275  | 550  | 100    |      | 550  | 100     |      | 450  |

| t <sub>OV+</sub> | Minimum Time SI and IR both HIGH |                 | 100    |      |      | 80     |      |      | 80      |      |      |

| t <sub>OV-</sub> | Minimum Time SI and IR both LOW  |                 | 100    |      |      | 80     |      |      | 80      |      |      |

| t <sub>DSI</sub> | Data Release Time                |                 | 400    |      |      | 200    |      |      | 200     |      |      |

| t <sub>DD</sub>  | Data Set-up Time                 |                 | 25     |      |      | 0      |      |      | 0       |      |      |

| t <sub>OR+</sub> | Delay, SO HIGH to OR LOW         |                 | 90     | 250  | 500  | 70     | 200  | 450  | 80      | 200  | 370  |

| t <sub>OR-</sub> | Delay, SO LOW to OR HIGH         |                 | 170    | 350  | 850  | 70     | 200  | 550  | 70      | 200  | 450  |

| t <sub>PT</sub>  | Ripple through Time              | FIFO Empty      |        | 10   | 32   | 8      | 16   |      | 8       | 16   | μs   |

| t <sub>DH</sub>  | Delay, OR LOW to Data Out        | SO = LOW        | 75     |      |      | 75     |      |      | 75      |      |      |

| t <sub>MRW</sub> | Minimum Reset Pulse Width        |                 |        |      | 400  |        |      | 400  |         |      | 400  |

| t <sub>DA</sub>  | Delay, Data Out to OR HIGH       | SO = HIGH       | 0      | 30   |      | 0      | 20   |      | 0       | 20   |      |

| Cl               | Input Capacitance (Except MR)    |                 |        |      | 7    |        |      | 7    |         |      | 7 pF |

| C <sub>MR</sub>  | Input Capacitance MR             |                 |        |      | 15   |        |      | 7    |         |      | 7 pF |

Note: Switching times over the entire temperature range are such that two devices at approximately the same ambient temperature can drive each other.

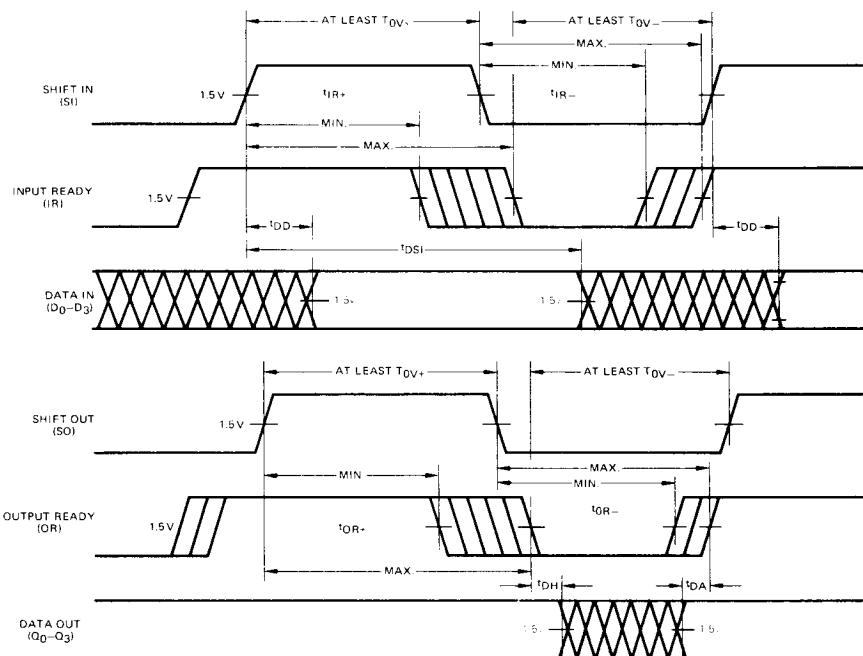

## TIMING DIAGRAM

查询"3341ADC"供应商

6

MOS-471

## USER NOTES

1. When the memory is empty the last word read will remain on the outputs until the master reset is strobed or a new data word falls through to the output. However, OR will remain LOW, indicating data at the output is not valid.

2. When the output data changes as a result of a pulse on SO, the OR signal always goes LOW before there is any change in output data and always stays LOW until after the new data has appeared on the outputs, so anytime OR is HIGH, there is good, stable data on the outputs.

3. If SO is held HIGH while the memory is empty and a word is written into the input, then that word will fall through the memory to the output. OR will go HIGH for one internal cycle (at least  $t_{OR+}$ ) and then will go back LOW again. The stored word will remain on the outputs. If more words are written into the FIFO, they will line up behind the first word and will not appear on the outputs until SO has been brought LOW.

4. When the master reset is brought LOW, the control register and the outputs are cleared. IR goes HIGH and OR goes LOW. If SI is HIGH when the master reset goes HIGH then the data on the inputs will be written into the memory and IR will return to the LOW state until SI is brought LOW. If SI is LOW when the master reset is ended, then IR will go HIGH, but the data on the inputs will not enter the memory until SI goes HIGH.

## 查询"3341ADC"供应商

MOS-472

### DESCRIPTION OF THE Am3341 FIFO OPERATION

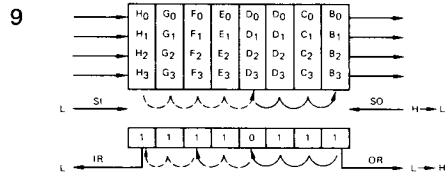

The Am3341 FIFO consists internally of 64 four-bit data registers and one 64-bit control register, as shown in the logic block diagram. A "1" in a bit of the control register indicates that a four-bit data word is stored in the corresponding data register. A "0" in a bit of the control register indicates that the corresponding data register does not contain valid data. The control register directs the movement of data through the data registers. Whenever the  $n^{\text{th}}$  bit of the control register contains a "1" and the  $(n+1)^{\text{th}}$  bit contains a "0", then a strobe is generated causing the  $(n+1)^{\text{th}}$  data register to read the contents of the  $n^{\text{th}}$  data register, simultaneously setting the  $(n+1)^{\text{th}}$  control register bit and clearing the  $n^{\text{th}}$  control register bit, so that the control flag moves with the data. In this fashion data in the data register moves down the stack of data registers toward the output as long as there are "empty" locations ahead of it. The fall-through operation stops when the data reaches a register  $n$  with a "1" in the  $(n+1)^{\text{th}}$  control register bit, or the end of the register.

Data is initially loaded from the four data inputs  $D_0$ – $D_3$  by applying a LOW-to-HIGH transition on the shift in (SI) input. A "1" is placed in the first control register bit simultaneously. The first control register bit is returned, buffered, to the input ready (IR) output, and this pin goes LOW indicating that data has been entered into the first data register and the input is now "busy", unable to accept more data. When SI next goes LOW, the fall-through process begins (assuming that at least the second location is empty). The data in the first register is copied into the second, and the first control register bit is cleared. This causes IR to go HIGH, indicating the inputs are available for another data word.

The data falling through the register stacks up at the output end. At the output the last control register bit is buffered and brought out as Output Ready (OR). A HIGH on OR indicates there is a "1" in the last control register bit and therefore there is valid data on the four data outputs  $Q_0$ – $Q_3$ . An input signal, shift out (SO), is used to shift the data out of the FIFO. A LOW-to-HIGH transition on SO clears the last register bit, causing OR to go LOW, indicating that the data on the outputs may no longer be valid. When SO goes LOW, the "0" which is now present at the last control register bit allows the data in the next to the last register to move into the last register position and on to the outputs. The "0" in the control register then "bubbles" back toward the input as the data shifts toward the output.

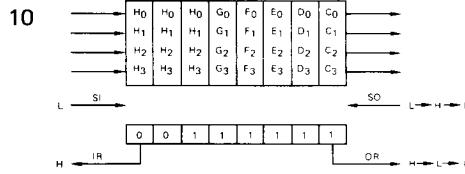

If the memory is emptied by reading out all the data, then when the last word is being read out and SO goes HIGH, OR will go LOW as before, but when SO next goes LOW, there is no data to move into the last location, so OR remains LOW until more data arrives at the output. Similarly, when the memory is full data written into the first location will not shift into the second when SI goes LOW, and IR will remain LOW instead of returning to a HIGH state.

The pairs of input and output control signals are designed so that the SO input of one FIFO can be driven by the IR output of another, and the OR output of the first FIFO can drive the SI input of the second, allowing simple expansion of the FIFO to any depth. Wider buffers are formed by allowing parallel rows of FIFOs to operate together, as shown in the application on the last page.

An over-riding master reset ( $\overline{MR}$ ) is used to reset all control register bits and remove the data from the output (i.e. reset the outputs to all LOW).

查询"3341ADC"供应商

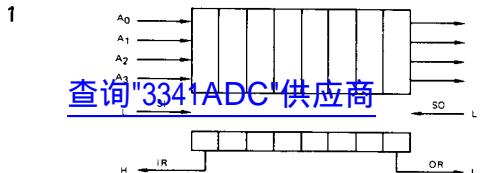

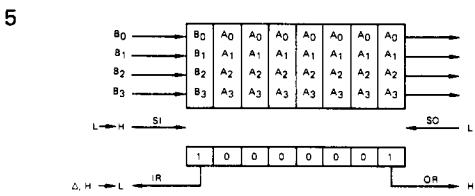

**INITIAL CONDITION**

FIFO empty, SI LOW IR HIGH, word "A" on inputs.

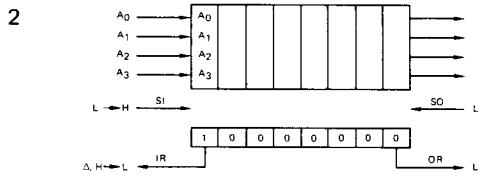

Write input into first stage by raising SI. ( $\Delta$  = delay) IR goes LOW indicating data has been entered.

Release data into FIFO by lowering SI. After delay, data moves to second location, and IR goes HIGH indicating input available for new data word.

Data spontaneously ripple through registers to end of FIFO, causing OR to go HIGH. The time required for data to fall completely through the FIFO is the "Ripple-through Time".

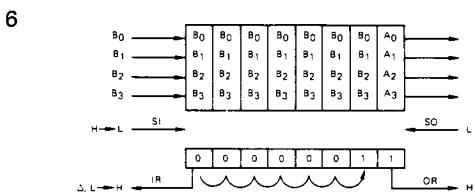

Word "B" written into FIFO

SI goes LOW allowing word "B" to fall through.

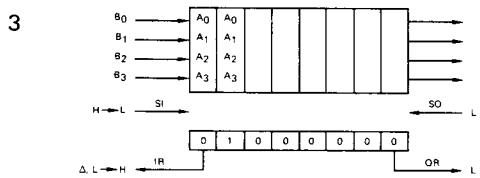

Word "C" written in same manner, and so on. When buffer is full, all control bits are 1's and IR stays LOW.

**FIRST READ OPERATION**

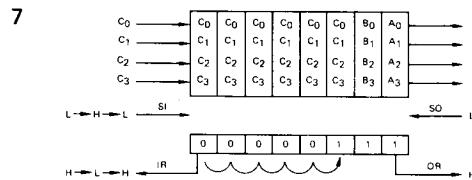

SO goes HIGH, indicating "Ready to Read". OR then goes LOW indicating "Data Read".

When SO goes LOW, the "0" in the last control bit bubbles toward the memory input. OR goes HIGH as the new word arrives at the output. IR goes HIGH when "0" reaches input.

Read word "B" out, word "C" moves to output, and so on.

Read word "H". OR stays LOW because FIFO is empty. Word "H" remains in output until new word falls through.

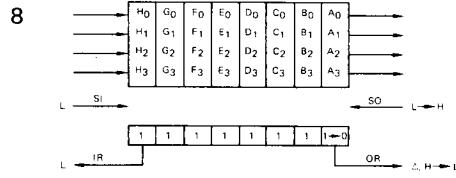

## APPLICATION

[查询"3341ADC"供应商](#)

The composite input ready indicates both devices are ready to receive data. The shift in pulse must be wide enough for all devices to load data under worst case conditions.

## 8 X 192 FIFO Buffer Using Am3341/Am2841

MOS-473

## Metallization and Pad Layout

126 x 138 Mils