# HT1623/HT1623G

# RAM Mapping 48×8 LCD Controller for I/O MCU

# PATENTED PAT No.: 099352

#### **Technical Document**

Application Note

#### **Features**

- Operating voltage: 2.7V~5.2V

- · Built-in RC oscillator

- External 32.768kHz crystal or 32kHz frequency source input

- 1/4 bias, 1/8 duty, frame frequency is 64Hz

- Max. 48×8 patterns, 8 commons, 48 segments

- Built-in internal resistor type bias generator

- 3-wire serial interface

- 8 kinds of time base or WDT selection

- Time base or WDT overflow output

- · Built-in LCD display RAM

- · R/W address auto increment

- Two selection buzzer frequencies (2kHz or 4kHz)

- · Power down command reduces power consumption

- · Software configuration feature

- Data mode and Command mode instructions

- · Three data accessing modes

- · VLCD pin to adjust LCD operating voltage

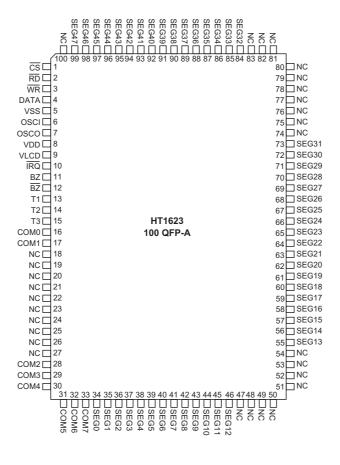

- HT1623: 100-pin QFP package HT1623G: Gold bumped chip

#### **General Description**

HT1623 is a peripheral device specially designed for I/O type MCU used to expand the display capability. The max. display segment of the device are 384 patterns (48×8). It also supports serial interface, buzzer sound, watchdog timer or time base timer functions. The HT1623 is a memory mapping and multi-function LCD controller. The software configuration feature of the

HT1623 make it suitable for multiple LCD applications including LCD modules and display subsystems. Only three lines are required for the interface between the host controller and the HT1623. The HT162X series have many kinds of products that match various applications.

#### **Selection Table**

| HT162X        | HT1620 | HT1621 | HT1622 | HT16220 | HT1623   | HT1625    | HT1626 |

|---------------|--------|--------|--------|---------|----------|-----------|--------|

| СОМ           | 4      | 4      | 8      | 8       | 8        | 8         | 16     |

| SEG           | 32     | 32     | 32     | 32      | 48       | 64        | 48     |

| Built-in Osc. | _      | √      | √      | _       | V        | $\sqrt{}$ | √      |

| Crystal Osc.  | √      | √      | _      | √       | <b>V</b> | √         | √      |

Rev. 1.70 1 November 9, 2010

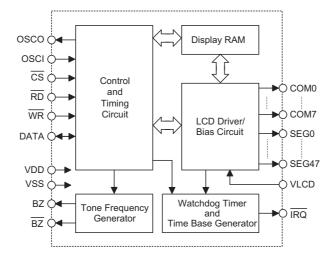

#### **Block Diagram**

# **Pin Assignment**

Rev. 1.70 2 November 9, 2010

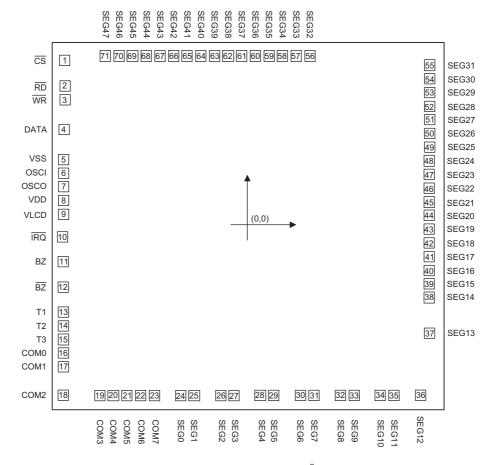

# **Pad Assignment**

Chip size:  $113 \times 106 \text{ (mil)}^2$

Bump height:  $18\mu m \pm 3\mu m$

Min. Bump spacing:  $23.102\mu m$

Bump size:  $76\times76\mu\text{m}^2$

Rev. 1.70 3 November 9, 2010

<sup>\*</sup> The IC substrate should be connected to VDD in the PCB layout artwork.

Pad Coordinates Unit: μm

| Pad No. | Х         | Υ         | Pad No. | Х         | Υ        |

|---------|-----------|-----------|---------|-----------|----------|

| 1       | -1328.790 | 1200.109  | 37      | 1322.060  | -779.760 |

| 2       | -1328.790 | 1008.378  | 38      | 1322.060  | -522.546 |

| 3       | -1328.785 | 909.341   | 39      | 1322.060  | -423.524 |

| 4       | -1337.200 | 696.447   | 40      | 1322.060  | -324.425 |

| 5       | -1337.162 | 475.635   | 41      | 1322.060  | -225.404 |

| 6       | -1337.925 | 376.661   | 42      | 1322.060  | -126.305 |

| 7       | -1337.925 | 277.639   | 43      | 1322.060  | -27.285  |

| 8       | -1337.887 | 178.570   | 44      | 1322.060  | 71.814   |

| 9       | -1337.925 | 79.595    | 45      | 1322.060  | 170.835  |

| 10      | -1343.075 | -79.689   | 46      | 1322.060  | 269.935  |

| 11      | -1337.925 | -260.141  | 47      | 1322.060  | 368.956  |

| 12      | -1337.925 | -444.992  | 48      | 1322.060  | 468.055  |

| 13      | -1337.925 | -625.740  | 49      | 1322.060  | 567.076  |

| 14      | -1337.925 | -724.760  | 50      | 1322.060  | 666.174  |

| 15      | -1337.925 | -823.859  | 51      | 1322.060  | 765.195  |

| 16      | -1337.925 | -922.880  | 52      | 1322.060  | 864.294  |

| 17      | -1337.925 | -1021.979 | 53      | 1322.060  | 963.315  |

| 18      | -1337.887 | -1228.075 | 54      | 1322.060  | 1062.415 |

| 19      | -1076.690 | -1228.075 | 55      | 1322.060  | 1161.436 |

| 20      | -977.669  | -1228.075 | 56      | 451.081   | 1226.600 |

| 21      | -878.570  | -1228.075 | 57      | 352.060   | 1226.600 |

| 22      | -779.549  | -1228.075 | 58      | 252.960   | 1226.600 |

| 23      | -680.449  | -1228.075 | 59      | 153.939   | 1226.600 |

| 24      | -488.720  | -1228.075 | 60      | 54.840    | 1226.600 |

| 25      | -389.620  | -1228.075 | 61      | -44.181   | 1226.600 |

| 26      | -197.889  | -1228.075 | 62      | -143.279  | 1226.600 |

| 27      | -98.790   | -1228.075 | 63      | -242.301  | 1226.600 |

| 28      | 92.941    | -1228.075 | 64      | -341.399  | 1226.600 |

| 29      | 192.040   | -1228.075 | 65      | -440.420  | 1226.600 |

| 30      | 383.771   | -1228.075 | 66      | -539.520  | 1226.600 |

| 31      | 482.871   | -1228.075 | 67      | -638.541  | 1226.600 |

| 32      | 674.600   | -1228.075 | 68      | -737.640  | 1226.600 |

| 33      | 773.701   | -1228.075 | 69      | -836.661  | 1226.600 |

| 34      | 965.431   | -1228.075 | 70      | -935.760  | 1226.600 |

| 35      | 1064.531  | -1228.075 | 71      | -1034.781 | 1226.600 |

| 36      | 1256.260  | -1228.075 |         |           |          |

# **Pad Description**

| Pad No. | Pad Name   | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | CS         | I   | Chip selection input with pull-high resistor. When the $\overline{\text{CS}}$ is logic high, the data and command read from or written to the HT1623 are disabled. The serial interface circuit is also reset But if the $\overline{\text{CS}}$ is at logic low level and is input to the $\overline{\text{CS}}$ pad, the data and command transmission between the host controller and the HT1623 are all enabled. |  |

| 2       | RD         | I   | READ clock input with pull-high resistor. Data in the RAM of the HT1623 are clocked out on the falling edge of the $\overline{\text{RD}}$ signal. The clocked out data will appear on the data line. The host controller can use the next rising edge to latch the clocked out data.                                                                                                                                |  |

| 3       | WR         | ı   | WRITE clock input with pull-high resistor. Data on the DATA line are latched into the HT1623 on the rising edge of the $\overline{WR}$ signal.                                                                                                                                                                                                                                                                      |  |

| 4       | DATA       | I/O | Serial data input or output with pull-high resistor                                                                                                                                                                                                                                                                                                                                                                 |  |

| 5       | VSS        | _   | Negative power supply, ground                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 6       | OSCI       | I   | The OSCI and OSCO pads are connected to a 32.768kHz crystal in order to                                                                                                                                                                                                                                                                                                                                             |  |

| 7       | osco       | 0   | generate a system clock. If the system clock comes from an external clock source, the external clock source should be connected to the OSCI pad. But if an on-chip RC oscillator is selected instead, the OSCI and OSCO pads can be left open.                                                                                                                                                                      |  |

| 8       | VDD        | _   | Positive power supply                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 9       | VLCD       | I   | LCD operating voltage input pad.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 10      | ĪRQ        | 0   | Time base or watchdog timer overflow flag, NMOS open drain output                                                                                                                                                                                                                                                                                                                                                   |  |

| 11, 12  | BZ, BZ     | 0   | 2kHz or 4kHz tone frequency output pair                                                                                                                                                                                                                                                                                                                                                                             |  |

| 13~15   | T1~T3      | I   | Not connected                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 16~23   | COM0~COM7  | 0   | LCD common outputs                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 24~71   | SEG0~SEG47 | 0   | LCD segment outputs                                                                                                                                                                                                                                                                                                                                                                                                 |  |

# **Absolute Maximum Ratings**

| Supply Voltage0.3V to 5.5V                                  | Storage Temperature50°C to 125°C  |

|-------------------------------------------------------------|-----------------------------------|

| Input VoltageV <sub>SS</sub> -0.3V to V <sub>DD</sub> +0.3V | Operating Temperature25°C to 75°C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Rev. 1.70 5 November 9, 2010

# **D.C. Characteristics**

Ta=25°C

| Country land                       | Devenueton                          |                 | Test Conditions          |      | Trees | Mess | I In !4 |

|------------------------------------|-------------------------------------|-----------------|--------------------------|------|-------|------|---------|

| Symbol                             | Parameter                           | V <sub>DD</sub> | Conditions               | Min. | Тур.  | Max. | Unit    |

| $V_{DD}$                           | Operating Voltage                   | _               | _                        | 2.7  | _     | 5.2  | V       |

|                                    | On and the original to              | 3V              | No load or LCD ON        | _    | 155   | 310  | μΑ      |

| I <sub>DD1</sub> Operating Current |                                     | 5V              | On-chip RC oscillator    | _    | 260   | 420  | μΑ      |

|                                    |                                     |                 | No load or LCD ON        | _    | 150   | 310  | μΑ      |

| I <sub>DD2</sub>                   | Operating Current                   | 5V              | Crystal oscillator       |      | 250   | 420  | μА      |

| I                                  | Operating Current                   | 3V              | No load or LCD OFF       | _    | 8     | 30   | μΑ      |

| I <sub>DD11</sub>                  | Operating Current                   | 5V              | On-chip RC oscillator    | _    | 20    | 60   | μΑ      |

|                                    | On anation Comment                  | 3V              | No load or LCD OFF       | _    | _     | 20   | μΑ      |

| I <sub>DD22</sub>                  | Operating Current                   | 5V              | Crystal oscillator       |      | _     | 35   | μΑ      |

| ı                                  | Chandle Command                     | 3V              | No lood Daws daws made   |      | 1     | 10   | μΑ      |

| I <sub>STB</sub>                   | Standby Current                     | 5V              | No load, Power down mode |      | 2     | 20   | μΑ      |

| V                                  | land the second                     | 3V              |                          | 0    | _     | 0.6  | V       |

| V <sub>IL</sub>                    | Input Low Voltage                   | 5V              | DATA, WR, CS, RD         | 0    | _     | 1.0  | V       |

| V                                  | Least I Pate Walter as              | 3V              | DATA, WR, CS, RD         | 2.4  | _     | 3    | V       |

| V <sub>IH</sub>                    | Input High Voltage                  | 5V              | DATA, WR, CS, RD         | 4.0  | _     | 5    | V       |

| ı                                  | DZ DZ IDO                           | 3V              | V <sub>OL</sub> =0.3V    | 0.9  | 1.8   | _    | mA      |

| I <sub>OL1</sub>                   | $BZ, \overline{BZ}, \overline{IRQ}$ | 5V              | V <sub>OL</sub> =0.5V    | 1.7  | 3     | _    | mA      |

|                                    | D7 D7                               | 3V              | V <sub>OH</sub> =2.7V    | -0.9 | -1.8  | _    | mA      |

| I <sub>OH1</sub>                   | BZ, <del>BZ</del>                   | 5V              | V <sub>OH</sub> =4.5V    | -1.7 | -3    | _    | mA      |

|                                    | DATA                                | 3V              | V <sub>OL</sub> =0.3V    | 0.9  | 1.8   | _    | mA      |

| I <sub>OL2</sub>                   | DATA                                | 5V              | V <sub>OL</sub> =0.5V    | 1.7  | 3     | _    | mA      |

|                                    | DATA                                | 3V              | V <sub>OH</sub> =2.7V    | -0.9 | -1.8  | _    | mA      |

| I <sub>OH2</sub>                   | DATA                                | 5V              | V <sub>OH</sub> =4.5V    | -1.7 | -3    | _    | mA      |

|                                    | LOD Common Sink Commont             | 3V              | V <sub>OL</sub> =0.3V    | 80   | 160   | _    | μА      |

| I <sub>OL3</sub>                   | LCD Common Sink Current             | 5V              | V <sub>OL</sub> =0.5V    | 180  | 360   | _    | μΑ      |

| ı                                  | LOD Common Course Course            | 3V              | V <sub>OH</sub> =2.7V    | -40  | -80   | _    | μΑ      |

| Іонз                               | LCD Common Source Current           | 5V              | V <sub>OH</sub> =4.5V    | -90  | -180  | _    | μΑ      |

| 1                                  | LCD Compat Sint Compat              | 3V              | V <sub>OL</sub> =0.3V    | 50   | 100   | _    | μΑ      |

| I <sub>OL4</sub>                   | LCD Segment Sink Current            | 5V              | V <sub>OL</sub> =0.5V    | 120  | 240   | _    | μΑ      |

| 1                                  | LCD Comment Course Course           | 3V              | V <sub>OH</sub> =2.7V    | -30  | -60   | _    | μΑ      |

| I <sub>OH4</sub>                   | LCD Segment Source Current          | 5V              | V <sub>OH</sub> =4.5V    | -70  | -140  | _    | μΑ      |

|                                    | Dull blak Deeler                    | 3V              | DATA WD 00 55            | 100  | 200   | 300  | kΩ      |

| R <sub>PH</sub>                    | Pull-high Resistor                  | 5V              | DATA, WR, CS, RD         | 50   | 100   | 150  | kΩ      |

#### A.C. Characteristics

Ta=25°C

| Symbol                          | Parameter                                                                                                      |                 | Test Conditions       | Min.    | Turn               | Max.   | Unit  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|---------|--------------------|--------|-------|--|

| Symbol                          | Farameter                                                                                                      | V <sub>DD</sub> | Conditions            | IVIIII. | Тур.               | IVIAX. | Oilit |  |

| f <sub>SYS1</sub>               | System Clock 5V On-                                                                                            |                 | On-chip RC oscillator | 24      | 32                 | 40     | kHz   |  |

| f <sub>SYS2</sub>               | System Clock                                                                                                   | _               | External clock source | _       | 32                 | _      | kHz   |  |

| f <sub>LCD1</sub>               | LCD Frame Frequency                                                                                            |                 | On-chip RC oscillator | 48      | 64                 | 80     | Hz    |  |

| f <sub>LCD2</sub>               | LCD Frame Frequency                                                                                            | _               | External clock source | _       | 64                 | _      | Hz    |  |

| t <sub>COM</sub>                | LCD Common Period                                                                                              | _               | n: Number of COM      | _       | n/f <sub>LCD</sub> | _      | sec   |  |

| £                               | 0 : 15 1 01 1 (115 5: )                                                                                        | 3V              | D / 500/              | 4       | _                  | 150    | kHz   |  |

| f <sub>CLK1</sub>               | Serial Data Clock (WR Pin)                                                                                     | 5V              | Duty cycle 50%        | 4       | _                  | 300    | kHz   |  |

| £.                              | 0 : 10 1 01 1 (55 5: )                                                                                         | 3V              | B                     | _       | _                  | 75     | kHz   |  |

| f <sub>CLK2</sub>               | Serial Data Clock (RD Pin)                                                                                     | 5V              | Duty cycle 50%        | _       | _                  | 150    | kHz   |  |

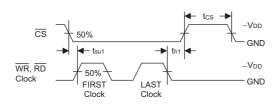

| t <sub>CS</sub>                 | Serial Interface Reset Pulse Width (Figure 3)                                                                  | _               | CS                    | 700     | 800                | _      | ns    |  |

|                                 | WR, RD Input Pulse Width (Figure 1)                                                                            | 3V              | Write mode            | 3.34    | _                  | 125    | μѕ    |  |

|                                 |                                                                                                                |                 | Read mode             | 6.67    | _                  | _      |       |  |

| t <sub>CLK</sub>                |                                                                                                                | 5V              | Write mode            | 1.67    | _                  | 125    |       |  |

|                                 |                                                                                                                |                 | Read mode             | 3.34    | _                  | _      | μS    |  |

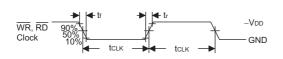

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Time Serial Data Clock Width (Figure 1)                                                              | _               | _                     | _       | 120                | 160    | ns    |  |

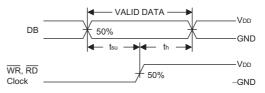

| t <sub>su</sub>                 | Setup Time DATA to WR, RD Clock<br>Width (Figure 2)                                                            | _               | _                     | 60      | 120                | _      | ns    |  |

| t <sub>h</sub>                  | Hold Time DATA to WR, RD Clock Width (Figure 2)                                                                | _               | _                     | 1000    | 1200               | _      | ns    |  |

| t <sub>su1</sub>                | Setup Time for CS to WR, RD Clock<br>Width (Figure 3)                                                          | _               | _                     | 500     | 600                | _      | ns    |  |

| t <sub>h1</sub>                 | Hold Time for $\overline{\text{CS}}$ to $\overline{\text{WR}}$ , $\overline{\text{RD}}$ Clock Width (Figure 3) | _               | _                     | 50      | 100                | _      | ns    |  |

| £                               | Tone Frequency (2kHz)                                                                                          | <b>5</b> \/     | On this BO and Haten  | 1.5     | 2.0                | 2.5    | kHz   |  |

| f <sub>TONE</sub>               | Tone Frequency (4kHz)                                                                                          | 5V              | On-chip RC oscillator | 3.0     | 4.0                | 5.0    | kHz   |  |

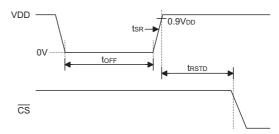

| t <sub>OFF</sub>                | V <sub>DD</sub> OFF Times (Figure 4)                                                                           | _               | VDD drop down to 0V   | 20      | _                  | _      | ms    |  |

| t <sub>SR</sub>                 | V <sub>DD</sub> Rising Slew Rate (Figure 4)                                                                    | _               | _                     | 0.05    | _                  | _      | V/ms  |  |

| t <sub>RSTD</sub>               | Delay Time after Reset (Figure 4)                                                                              | _               | _                     | 1       | _                  | _      | ms    |  |

|                                 | 1                                                                                                              |                 | 1                     |         |                    |        |       |  |

Note: 1. If the conditions of Power-on Reset timing are not satisfied in power On/Off sequence, the internal Power-on Reset (POR) circuit will not operate normally.

<sup>2.</sup> If the VDD drops below the minimum voltage of operating voltage spec. during operating, the conditions of Power-on Reset timing must be satisfied also. That is, the VDD must drop to 0V and keep at 0V for 20ms (min.) before rising to the normal operating voltage.

Figure 1

Figure 3

Figure 2

Figure 4. Power-on Reset Timing

#### **Functional Description**

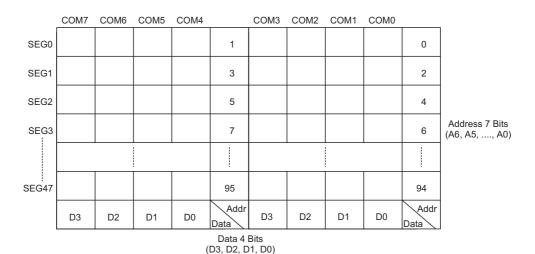

#### **Display Memory - RAM Structure**

The static display RAM is organized into  $96\times4$  bits and stores the display data. The contents of the RAM are directly mapped to the contents of the LCD driver. Data in the RAM can be accessed by theREAD, WRITE and READ-MODIFY-WRITE commands. The following is a mapping from the RAM to the LCD patterns.

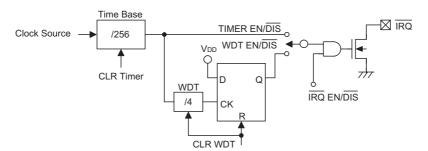

#### Time Base and Watchdog Timer - WDT

The time base generator and WDT share the same divided (/256) counter. TIMER DIS/EN/CLR, WDT DIS/EN/CLR and  $\overline{\text{IRQ}}$  EN/DIS are independent from each other. Once the WDT time-out occurs, the  $\overline{\text{IRQ}}$  pin will remain at logic low level until the CLR WDT or the  $\overline{\text{IRQ}}$  DIS command is issued.

If an external clock is selected as the source of system frequency, the SYS DIS command turns out invalid and the power down mode fails to be carried out until the external clock source is removed.

#### **Buzzer Tone Output**

A simple tone generator is implemented in the HT1623. The tone generator can output a pair of differential driving signals on the BZ and  $\overline{\text{BZ}}$  which are used to generate a single tone.

#### **Command Format**

The HT1623 can be configured by the software setting. There are two mode commands to configure the HT1623 resource and to transfer the LCD display data.

**RAM Mapping**

**Timer and WDT Configurations**

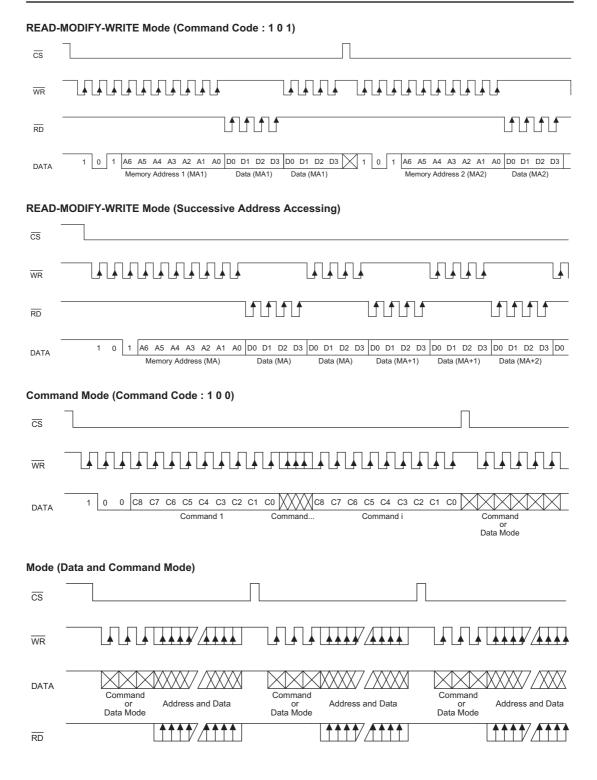

The following are the data mode ID and the command mode ID:

| Operation         | Mode    | ID  |

|-------------------|---------|-----|

| READ              | Data    | 110 |

| WRITE             | Data    | 101 |

| READ-MODIFY-WRITE | Data    | 101 |

| COMMAND           | Command | 100 |

If successive commands have been issued, the command mode ID can be omitted. While the system is operating in the non-successive command or the non-successive address data mode, the  $\overline{\text{CS}}$  pin should be set to "1" and the previous operation mode will be reset also. The  $\overline{\text{CS}}$  pin returns to "0", a new operation mode ID should be issued first.

| Name     | Command Code | Function                                    |

|----------|--------------|---------------------------------------------|

| TONE OFF | 0000-1000-X  | Turn-off tone output                        |

| TONE 4K  | 010X-XXXX-X  | Turn-on tone output, tone frequency is 4kHz |

| TONE 2K  | 0110-XXXX-X  | Turn-on tone output, tone frequency is 2kHz |

Rev. 1.70 9 November 9, 2010

**Timing Diagrams**

# READ Mode (Command Code: 110) cs WR RD 0 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 0 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 DATA Memory Address 1 (MA1) Data (MA1) Memory Address 2 (MA2) **READ Mode (Successive Address Reading)** CS WR RD 0 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 D0 DATA Data (MA) Data (MA+1) Data (MA+2) Memory Address (MA) Data (MA+3) WRITE Mode (Command Code: 101) cs WR 1 0 1 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 0 1 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 DATA Memory Address 1 (MA1) Data (MA1) Memory Address 2 (MA2) WRITE Mode (Successive Address Writing) cs WR 1 0 1 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 D3 D0 DATA Memory Address (MA) Data (MA) Data (MA+1) Data (MA+2)

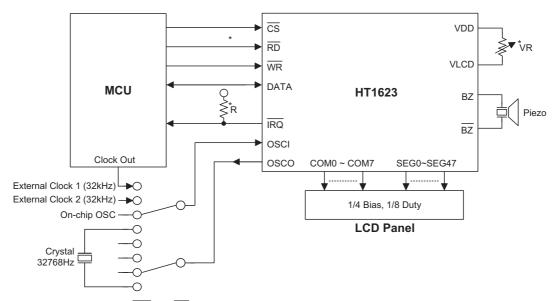

# **Application Circuits**

Note: The connection of  $\overline{IRQ}$  and  $\overline{RD}$  pin can be selected depending on the requirement of the MCU.

The voltage applied to  $V_{\text{LCD}}$  pin must be equal to or lower than  $V_{\text{DD}}$ .

Adjust VR to fit LCD display, at V<sub>DD</sub>=5V, V<sub>LCD</sub>=4V, VR=15k $\Omega\pm20\%$ .

Adjust R (external pull-high resistance) to fit user's time base clock.

# **Command Summary**

| Name                  | ID  | Command Code           | D/C                                                     | Function                                                                         | Def. |

|-----------------------|-----|------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------|------|

| READ                  | 110 | A6A5A4A3A2A1A0D0D1D2D3 | D                                                       | Read data from the RAM                                                           |      |

| WRITE                 | 101 | A6A5A4A3A2A1A0D0D1D2D3 | D                                                       | Write data to the RAM                                                            |      |

| READ-MODIFY-<br>WRITE | 101 | A6A5A4A3A2A1A0D0D1D2D3 | D Read and Write data to the RAM                        |                                                                                  |      |

| SYS DIS               | 100 | 0000-0000-X            | C Turn off both system oscillator and LCD bia generator |                                                                                  | Yes  |

| SYS EN                | 100 | 0000-0001-X            | С                                                       | Turn on system oscillator                                                        |      |

| LCD OFF               | 100 | 0000-0010-X            | С                                                       | Turn off LCD display                                                             | Yes  |

| LCD ON                | 100 | 0000-0011-X            | С                                                       | Turn on LCD display                                                              |      |

| TIMER DIS             | 100 | 0000-0100-X            | С                                                       | Disable time base output                                                         | Yes  |

| WDT DIS               | 100 | 0000-0101-X            | С                                                       | Disable WDT time-out flag output                                                 | Yes  |

| TIMER EN              | 100 | 0000-0110-X            | С                                                       | Enable time base output                                                          |      |

| WDT EN                | 100 | 0000-0111-X            | С                                                       | Enable WDT time-out flag output                                                  |      |

| TONE OFF              | 100 | 0000-1000-X            | С                                                       | Turn off tone outputs                                                            | Yes  |

| CLR TIMER             | 100 | 0000-1101-X            | С                                                       | Clear the contents of the time base generator                                    |      |

| CLR WDT               | 100 | 0000-1111-X            | С                                                       | Clear the contents of the WDT stage                                              |      |

| RC 32K                | 100 | 0001-10XX-X            | С                                                       | System clock source, on-chip RC oscillator                                       | Yes  |

| EXT (XTAL) 32K        | 100 | 0001-11XX-X            | С                                                       | System clock source, external 32kHz clock source or crystal oscillator 32.768kHz |      |

| TONE 4K               | 100 | 010X-XXXX-X            | С                                                       | Tone frequency output: 4kHz                                                      |      |

Rev. 1.70 12 November 9, 2010

| Name    | ID  | Command Code | D/C                                                           | Function                                                            | Def. |

|---------|-----|--------------|---------------------------------------------------------------|---------------------------------------------------------------------|------|

| TONE 2K | 100 | 0110-XXXX-X  | С                                                             | Tone frequency output: 2kHz                                         |      |

| IRQ DIS | 100 | 100X-0XXX-X  | С                                                             | Disable IRQ output                                                  | Yes  |

| IRQ EN  | 100 | 100X-1XXX-X  | С                                                             | Enable IRQ output                                                   |      |

| F1      | 100 | 101X-0000-X  | С                                                             | Time base clock output: 1Hz<br>The WDT time-out flag after: 4s      |      |

| F2      | 100 | 101X-0001-X  | С                                                             | Time base clock output: 2Hz<br>The WDT time-out flag after: 2s      |      |

| F4      | 100 | 101X-0010-X  | C Time base clock output: 4Hz The WDT time-out flag after: 1s |                                                                     |      |

| F8      | 100 | 101X-0011-X  | С                                                             | Time base clock output: 8Hz The WDT time-out flag after: 1/2s       |      |

| F16     | 100 | 101X-0100-X  | С                                                             | Time base clock output: 16Hz The WDT time-out flag after: 1/4s      |      |

| F32     | 100 | 101X-0101-X  | С                                                             | Time base clock output: 32Hz The WDT time-out flag after: 1/8s      |      |

| F64     | 100 | 101X-0110-X  | С                                                             | Time base clock output: 64Hz<br>The WDT time-out flag after: 1/16s  |      |

| F128    | 100 | 101X-0111-X  | С                                                             | Time base clock output: 128Hz<br>The WDT time-out flag after: 1/32s | Yes  |

| TEST    | 100 | 1110-0000-X  | С                                                             | Test mode, user don't use.                                          |      |

| NORMAL  | 100 | 1110-0011-X  | С                                                             | Normal mode                                                         | Yes  |

Note: X: Don't care

A6~A0 : RAM address D3~D0 : RAM data

D/C : Data/Command mode

Def. : Power on reset default

All the bold forms, namely **1 1 0, 1 0 1**, and **1 0 0**, are mode commands. Of these, **1 0 0** indicates the command mode ID. If successive commands have been issued, the command mode ID except for the first command will be omitted. The source of the tone frequency and of the time base or WDT clock frequency can be derived from an on-chip 32kHz RC oscillator, a 32.768kHz crystal oscillator, or an external 32kHz clock. Calculation of the frequency is based on the system frequency sources as stated above. It is recommended that the host controller should initialize the HT1623 after power on reset, for power on reset may fail, which in turn leads to the malfunctioning of the HT1623.

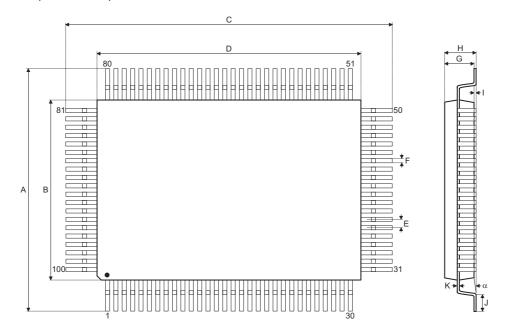

# **Package Information**

# 100-pin QFP (14mm×20mm) Outline Dimensions

| Complete | Dimensions in inch |       |       |  |  |  |  |

|----------|--------------------|-------|-------|--|--|--|--|

| Symbol   | Min.               | Nom.  | Max.  |  |  |  |  |

| Α        | 0.728              | _     | 0.756 |  |  |  |  |

| В        | 0.547              | _     | 0.555 |  |  |  |  |

| С        | 0.965              | _     | 0.992 |  |  |  |  |

| D        | 0.783              | _     | 0.791 |  |  |  |  |

| E        | _                  | 0.026 | _     |  |  |  |  |

| F        | _                  | 0.012 | _     |  |  |  |  |

| G        | 0.098              | _     | 0.122 |  |  |  |  |

| Н        | _                  | _     | 0.134 |  |  |  |  |

| I        | _                  | 0.004 | _     |  |  |  |  |

| J        | 0.039              | _     | 0.055 |  |  |  |  |

| K        | 0.004              | _     | 0.008 |  |  |  |  |

| α        | 0°                 | _     | 7°    |  |  |  |  |

Rev. 1.70 14 November 9, 2010

| Symbol | Dimensions in mm |      |       |  |  |  |  |

|--------|------------------|------|-------|--|--|--|--|

| Symbol | Min.             | Nom. | Max.  |  |  |  |  |

| Α      | 18.50            | _    | 19.20 |  |  |  |  |

| В      | 13.90            | _    | 14.10 |  |  |  |  |

| С      | 24.50            | _    | 25.20 |  |  |  |  |

| D      | 19.90            | _    | 20.10 |  |  |  |  |

| E      | _                | 0.65 | _     |  |  |  |  |

| F      | _                | 0.30 | _     |  |  |  |  |

| G      | 2.50             | _    | 3.10  |  |  |  |  |

| Н      | _                | _    | 3.40  |  |  |  |  |

| I      | _                | 0.1  | _     |  |  |  |  |

| J      | 1.00             | _    | 1.40  |  |  |  |  |

| К      | 0.10             | _    | 0.20  |  |  |  |  |

| α      | 0°               | _    | 7°    |  |  |  |  |

Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070 Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

#### Holtek Semiconductor Inc. (Shenzhen Sales Office)

5F, Unit A, Productivity Building, No.5 Gaoxin M 2nd Road, Nanshan District, Shenzhen, China 518057 Tel: 86-755-8616-9908, 86-755-8616-9308

Fax: 86-755-8616-9722

### Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538

Tel: 1-510-252-9880 Fax: 1-510-252-9885 http://www.holtek.com

#### Copyright © 2010 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.70 November 9, 2010