#### **Features**

#### MCU Features

- MCU Operating voltage:

f<sub>SYS</sub>= 4MHz: 2.2V~3.6V

f<sub>SYS</sub>= 8MHz: 3.0V~3.6V

- Power Down modes and wake-up functions to reduce power consumption

- · Oscillator types

- External high frequency Crystal

- External RC

- Internal RC

- External low frequency crystal

- Watchdog Timer Internal RC Oscillator

- Three operational modes: Normal, Slow, Sleep

- Fully integrated internal 4MHz, 8MHz oscillator requires no external components

- OTP Program Memory: 1K×15

- RAM Data Memory: 96×8

- · Watchdog Timer function

- · All instructions executed in one or two instruction cycles

- · Table read instructions

- 63 powerful instructions

- 6-level subroutine nesting

- · Bit manipulation instruction

- · Low voltage reset function

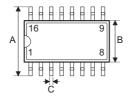

- 16-pin NSOP package type

- Up to 8 bidirectional I/O lines

- 4 channel 12-bit ADC

- 1 channel 8-bit PWM

- External interrupt input shared with an I/O line

- Two 8-bit programmable Timer/Event Counter with overflow interrupt and prescaler

- · Time-Base function

- Programmable Frequency Divider PFD

#### **RF Transmitter Features**

- Complete UHF ASK/OOK transmitter

- Frequency range 300MHz to 450MHz

- Data rates more than 10k bps

- Output Power up to 10dBm

- Low voltage operation down to 2.2V

- Data tracking function for power saving

- Reference clock output for MCU IRC clock synchronisation

Rev. 1.30 1 November 23, 2010

### **General Description**

These devices provide a combination of a fully featured MCU plus an RF transmitter function, giving them great flexibility for use in wide range of wireless I/O control applications such as industrial control, consumer products, subsystem controllers, etc.

Analog features include a multi-channel 12-bit A/D converter. Multiple and extremely flexible Timer/Event Counters provide full timing functions. Protective features such as an internal Watchdog Timer and Low Voltage Reset coupled with excellent noise immunity and ESD protection ensure that reliable operation is maintained in hostile electrical environments. An extensive choice of oscillator functions are provided including a fully integrated system oscillator which requires no external components for its implementation. The ability to operate and switch dynamically between a range of operating modes using different clock sources gives users the ability to optimise microcontroller operation and minimise power consumption. The devices also include flexible I/O programming features Time-Base functions and a range of other features.

The RF transmitter is a high performance and easy to use transmitter operating in the 300MHz to 450MHz frequency band. One only needs to add a crystal reference frequency, and a limited number of external components to create a complete and versatile RF transmitter system. The device is capable of delivering more than +9dBm into a  $50\Omega$  load. Such a power level enables a small form factor transmitter to operate near the maximum limit of the transmission regulations. The device can operate with ASK - Amplitude Shift Keying, and OOK - On-Off Keying, UHF receiver types from wide-band super-regenerative radios to narrow-band, high performance super-heterodyne receivers. The data rate is higher than 10kbps, allowing the device to support more complicated control protocols.

For enhanced power saving, the device includes a data tracking function. The data tracking function enables the PLL to be activated as long as high transient data input trigger signals are received. The PLL will also be automatically switched off if there are no data input transients for a time exceeding approximately 300ms. As there is a reference clock input on line PB0, the MCU can use its internal RC clock rather than using an additional crystal for the system clock. These features add up to ensure that the devices can offer excellent capabilities in terms of functionality and power-saving as well as being highly cost effective in a huge range of remote wireless applications

#### **Selection Guide**

| Part No.  | Program<br>Memory | Data<br>Memory | I/O | 8-bit<br>Timer | Time<br>Base | RF<br>Transmitter | A/D      | PWM     | Stack | Package |

|-----------|-------------------|----------------|-----|----------------|--------------|-------------------|----------|---------|-------|---------|

| HT48R01T3 | 1K×15             | 96×8           | 9   | 2              | 1            | √                 | _        | _       | 6     | 16NSOP  |

| HT46R01T3 | 1K×15             | 96×8           | 9   | 2              | 1            | √                 | 12-bit×4 | 8-bit×1 | 6     | 16NSOP  |

Rev. 1.30 2 November 23, 2010

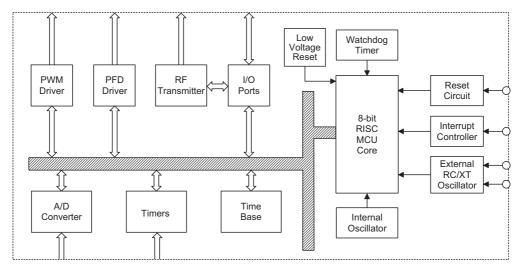

## **Block Diagram**

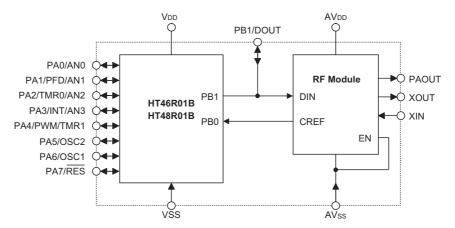

The following block diagram illustrates the dual-chip structure of the devices, where an individual MCU and RF Transmitter devices are combined into a single package.

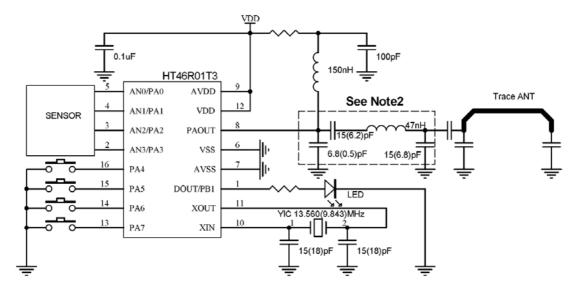

**Internal Chip Interconnection Diagram**

Note: The PWM and AN0~AN3 shared-pin functions only exist in the HT46R01T3 device.

Note: The PWM and A/D Converter functions only exist in the HT46R01T3 device.

Rev. 1.30 November 23, 2010

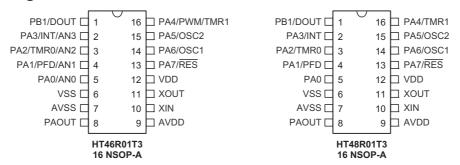

## **Pin Assignment**

## **Pin Description**

### HT46R01T3

| Pin Name     | Function | ОРТ          | I/T | O/T  | Description                                                |

|--------------|----------|--------------|-----|------|------------------------------------------------------------|

| PA0/AN0      | PA0      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|              | AN0      | ADCR         | AN  | _    | A/D channel 0                                              |

|              | PA1      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA1/PFD/AN1  | PFD      | CTRL0        | _   | CMOS | PFD output                                                 |

|              | AN1      | ADCR         | AN  | _    | A/D channel 1                                              |

|              | PA2      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA2/TMR0/AN2 | TC0      | _            | ST  | _    | External Timer 0 clock input                               |

|              | AN2      | ADCR         | AN  | _    | A/D channel 2                                              |

|              | PA3      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA3/INT/AN3  | INT      | _            | ST  | _    | External interrupt input                                   |

|              | AN3      | ADCR         | AN  | _    | A/D channel 3                                              |

|              | PA4      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA4/TMR1/PWM | TC1      | _            | ST  | _    | External Timer 1 clock input                               |

|              | PWM      | CTRL0        | _   | CMOS | PWM output                                                 |

| PA5/OSC2     | PA5      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|              | OSC2     | СО           | _   | osc  | Oscillator pin                                             |

| PA6/OSC1     | PA6      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|              | OSC1     | СО           | osc |      | Oscillator pin                                             |

| PA7/RES      | PA7      | PAWK         | ST  | NMOS | General purpose I/O. Register enabled wake-up.             |

| PA//KES      | RES      | СО           | ST  | _    | Reset input                                                |

Rev. 1.30 4 November 23, 2010

| Pin Name | Function | ОРТ  | I/T | O/T  | Description                                                                                                                                        |

|----------|----------|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| PB1/DOUT | PB1      | PBPU | ST  | CMOS | General purpose I/O. Register enabled pull-up. Internally connected to DIN pin on RF module. Must be setup as output for interfacing to RF module. |

|          | DOUT     | _    | _   | _    | Data output from MCU to RF module<br>Connected internally to PB1                                                                                   |

| PAOUT    | PAOUT    | _    | _   | NSO  | RF power amplifier output                                                                                                                          |

| XOUT     | XOUT     | _    | _   | HXT  | RF chip crystal pin                                                                                                                                |

| XIN      | XIN      | _    | HXT | _    | RF chip crystal pin                                                                                                                                |

| VDD      | VDD      | _    | PWR | _    | MCU power supply                                                                                                                                   |

| VSS      | VSS      | _    | PWR | _    | MCU ground                                                                                                                                         |

| AVDD     | AVDD     | _    | PWR | _    | RF chip power supply                                                                                                                               |

| AVSS     | AVSS     |      | PWR | _    | RF chip ground                                                                                                                                     |

Note: I/T: Input type

O/T: Output type

OPT: Optional by configuration option (CO) or register option

PWR: Power

CO: Configuration option ST: Schmitt Trigger input CMOS: CMOS output NSO: Non-standard output

## HT48R01T3

| Pin Name | Function      | ОРТ          | I/T | O/T  | Description                                                |

|----------|---------------|--------------|-----|------|------------------------------------------------------------|

| PA0      | PA0           | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA1/PFD  | PA1           | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|          | PFD           | CTRL0        | _   | CMOS | PFD output                                                 |

| PA2/TMR0 | PA2           | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|          | TC0           | _            | ST  | _    | External Timer 0 clock input                               |

| PA3/INT  | PA3 PAPU PAWK |              | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|          | INT           | _            | ST  | _    | External interrupt input                                   |

| PA4/TMR1 | PA4           | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|          | TC1           | _            | ST  | _    | External Timer 1 clock input                               |

| PA5/OSC2 | PA5           | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|          | OSC2          | СО           | _   | osc  | Oscillator pin                                             |

| PA6/OSC1 | PA6           | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|          | OSC1          | со           | osc |      | Oscillator pin                                             |

| Pin Name | Function | ОРТ  | I/T | O/T                                                              | Description                                                                                                                                        |

|----------|----------|------|-----|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| DAZ/DEC  | PA7      | PAWK | ST  | NMOS                                                             | General purpose I/O. Register enabled wake-up.                                                                                                     |

| PA7/RES  | RES      | СО   | ST  | _                                                                | Reset input                                                                                                                                        |

| PB1/DOUT | PB1      | PBPU | ST  | CMOS                                                             | General purpose I/O. Register enabled pull-up. Internally connected to DIN pin on RF module. Must be setup as output for interfacing to RF module. |

|          |          |      | _   | Data output from MCU to RF module<br>Connected internally to PB1 |                                                                                                                                                    |

| PAOUT    | PAOUT    | _    | _   | NSO RF power amplifier output                                    |                                                                                                                                                    |

| XOUT     | XOUT     | _    | _   | HXT                                                              | RF chip crystal pin                                                                                                                                |

| XIN      | XIN      | _    | HXT | _                                                                | RF chip crystal pin                                                                                                                                |

| VDD      | VDD      | _    | PWR | _                                                                | MCU power supply                                                                                                                                   |

| VSS      | VSS      | _    | PWR | _                                                                | MCU ground                                                                                                                                         |

| AVDD     | AVDD     | _    | PWR | _                                                                | RF chip power supply                                                                                                                               |

| AVSS     | AVSS     | _    | PWR | _                                                                | RF chip ground                                                                                                                                     |

Note: I/T: Input type

O/T: Output type

OPT: Optional by configuration option (CO) or register option

PWR: Power

CO: Configuration option ST: Schmitt Trigger input CMOS: CMOS output NSO: Non-standard output

## **Internally Connected Pins**

In addition to the internal connection between MCU pin, PB1, and RF Transmitter pin, DIN, the MCU pin, PB0, and RF Transmitter pin, CREF, are also internally connected. However it should be noted that PB0/CREF is not connected to any external pins on the device package.

| Pin Name | Function | ОРТ  | I/T | O/T                                                                                                         | Description                                                                                                                                                                                |

|----------|----------|------|-----|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB0/CREF | PB0      | PBPU | ST  | CMOS                                                                                                        | General Purpose I/O. Register enabled pull-high resistor. Internally connected to CREF pin on RF module. Must be setup as an input for interfacing to RF module. Not available on package. |

|          | CREF — — |      | _   | RF Transmitter generated pulses for synchronisation. Connected internally to PB0. Not available on package. |                                                                                                                                                                                            |

Rev. 1.30 6 November 23, 2010

## **D.C. Characteristics**

[a=25°C

| 0                 | Damanatan                                            |                 | Test Conditions                                  | B.#1               | <b>T</b> |                    | 1124 |

|-------------------|------------------------------------------------------|-----------------|--------------------------------------------------|--------------------|----------|--------------------|------|

| Symbol            | Parameter                                            | V <sub>DD</sub> | Conditions                                       | Min.               | Тур.     | Max.               | Unit |

| $V_{DD}$          | Operating Voltage                                    |                 | f <sub>SYS</sub> =4MHz                           | 2.2                | _        | 3.6                | V    |

| <b>V</b> DD       | Operating voltage                                    |                 | f <sub>SYS</sub> =8MHz                           | 3.3                | _        | 3.6                | V    |

| $AV_{DD}$         | RF Transmitter Power Supply                          | _               | _                                                | 2.0                | _        | 3.6                | V    |

| I <sub>DD1</sub>  | Operating current (Crystal OSC, RC OSC)              | 3V              | No load, f <sub>SYS</sub> =4MHz,<br>ADC disable  | _                  | 1        | 2                  | mA   |

| I <sub>DD2</sub>  | Operating Current (internal RC+RTC OSC, Normal Mode) | 3V              | No load, f <sub>SYS</sub> =4MHz,<br>ADC disable  | _                  | 1        | 2                  | mA   |

| I <sub>STB1</sub> | Standby Current<br>(WDT OSC on, RTC off)             | 3V              | No load, system HALT                             | _                  | _        | 5                  | μА   |

| I <sub>STB2</sub> | Standby Current<br>(WDT OSC off, RTC off)            | 3V              | No load, system HALT                             | _                  | _        | 1                  | μА   |

| I <sub>STB3</sub> | Standby Current<br>(WDT OSC off, RTC on)             | 3V              | No load, system HALT,<br>RTC osc slowly start-up | _                  | _        | 5                  | μА   |

| V <sub>IL1</sub>  | Input Low Voltage for PA, PB,<br>TMR0, TMR1, INT     | _               | _                                                | 0                  | _        | 0.3V <sub>DD</sub> | V    |

| V <sub>IH1</sub>  | Input High Voltage for PA, PB, TMR0, TMR1, INT       | _               | _                                                | 0.7V <sub>DD</sub> | _        | V <sub>DD</sub>    | V    |

| V <sub>IL2</sub>  | Input Low Voltage (RES)                              | _               | _                                                | 0                  | _        | 0.4V <sub>DD</sub> | V    |

| V <sub>IH2</sub>  | Input High Voltage (RES)                             | _               | _                                                | 0.9V <sub>DD</sub> | _        | V <sub>DD</sub>    | V    |

| V <sub>LVR1</sub> | Low Voltage Reset 1                                  | _               | Configuration option=2.1V                        | 1.98               | 2.10     | 2.22               | V    |

| V <sub>LVR2</sub> | Low Voltage Reset 2                                  | _               | Configuration option=3.15V                       | 2.98               | 3.15     | 3.32               | V    |

| I <sub>OL</sub>   | I/O Port Sink Current for PA, PB                     | 3V              | V <sub>OL</sub> =0.1V <sub>DD</sub>              | 4                  | 8        | _                  | mA   |

| I <sub>OH</sub>   | I/O Port Source Current for PA, PB                   | 3V              | V <sub>OH</sub> =0.9V <sub>DD</sub>              | -2                 | -4       | _                  | mA   |

| R <sub>PH</sub>   | Pull-high Resistance for I/O                         | 3V              | _                                                | 20                 | 60       | 100                | kΩ   |

## A.C. Characteristics

Ta=25°C

| 0                | Dt.                            |                 | Test Conditions   | D.C. | <b>-</b> |      | 1114             |

|------------------|--------------------------------|-----------------|-------------------|------|----------|------|------------------|

| Symbol           | Parameter                      | V <sub>DD</sub> | Conditions        | Min. | Тур.     | Max. | Unit             |

| fHIRC            | System Clock<br>(HIRC)         | 3V              | Ta= -40°C~85°C    | -10% | 4/8      | +10% | MHz              |

| f                | Timer Input Frequency          | _               | 2.2V~3.6V         | 0    | _        | 4000 | kHz              |

| TTIMED           | (TCn)                          |                 | 3.3V~3.6V         | 0    | _        | 8000 | kHz              |

| twotosc          | Watchdog Oscillator Period     | 3V              | _                 | 45   | 90       | 180  | μS               |

| t <sub>RES</sub> | External Reset Low Pulse Width | _               | _                 | 1    | _        | _    | μS               |

| t <sub>SST</sub> | System Start-up Time Period    |                 | Wake-Up from HALT | _    | 1024     | _    | t <sub>SYS</sub> |

| t <sub>INT</sub> | Interrupt Pulse Width          | _               | _                 | 1    | _        | _    | μS               |

| t <sub>LVR</sub> | Low Voltage Width to Reset     | _               | _                 | 0.25 | 1.00     | 2.00 | ms               |

Note: 1. t<sub>SYS</sub>=1/f<sub>SYS</sub>

## A/D Converter Electrical Characteristics

Ta=25°C

| Completed                              | Downston                                              |                 | Test Conditions                                       | D.A.L.       | T    | Marr                                   | 11              |

|----------------------------------------|-------------------------------------------------------|-----------------|-------------------------------------------------------|--------------|------|----------------------------------------|-----------------|

| Symbol                                 | Parameter                                             | V <sub>DD</sub> | Conditions                                            | Min.         | Тур. | Max.                                   | Unit            |

| V <sub>ADC</sub>                       | A/D Operating Voltage                                 | _               | V <sub>REF</sub> =V <sub>ADC</sub>                    | 2.7          |      | 3.6                                    | V               |

| V <sub>ADI</sub>                       | A/D Converter Input Voltage                           | _               | _                                                     | 0            | _    | V <sub>ADC</sub> /<br>V <sub>REF</sub> | V               |

| V <sub>REF</sub>                       | A/D Converter Input reference<br>Voltage Range        |                 | V <sub>ADC</sub> =3V                                  | TBD<br>(TBC) | _    | V <sub>ADC</sub><br>+0.1               | V               |

| DNL A/D Converter Differ Non-Linearity | A/D Converter Differential                            | 2.7V            | V <sub>REF</sub> =V <sub>ADC</sub> =V <sub>DD</sub> , | -2           |      | 2                                      | LSB             |

|                                        | Non-Linearity                                         | 3V              | t <sub>AD</sub> =0.5μs                                |              |      |                                        | LOD             |

|                                        | A/D Converter Integral                                | 2.7V            | V <sub>REF</sub> =V <sub>ADC</sub> =V <sub>DD</sub> , |              |      | 4                                      | LSB             |

| INL                                    | Non-Linearity                                         | 3V              | t <sub>AD</sub> =0.5µs (calculated on best-fit line)  | -4           |      |                                        |                 |

| I <sub>ADC</sub>                       | Additional Power Consumption if A/D Converter is Used | 3V              | No load, t <sub>AD</sub> =0.5μs                       | _            | 0.5  | _                                      | mA              |

| t <sub>AD</sub>                        | A/D Converter Clock Period                            | 2.7V~<br>3.6V   | _                                                     | 0.5          |      | 10                                     | μs              |

| t <sub>ADC</sub>                       | A/D Converter Sampling Time (see note)                | 2.7V~<br>3.6V   | 12-bit ADC                                            | _            | 16   | _                                      | t <sub>AD</sub> |

| t <sub>ON2ST</sub>                     | A/D Converter on to ADC Start                         | 2.7V~<br>3.6V   | _                                                     | 2            | _    |                                        | μs              |

Note: ADC conversion time  $(t_{AD})$ = n (bits ADC) + 4 (sampling time), the conversion for each bit needs one ADC  $clock(t_{AD})$ .

Rev. 1.30 8 November 23, 2010

<sup>2. \*</sup>For  $f_{\text{ERC}}$ , as the resistor tolerance will influence the frequency a precision resistor is recommended.

## **RF Transmitter Electrical Characteristics**

Specifications apply for AV  $_{DD}\!=\!3.0V,$  Ta = 25°C, Freq X'tal OSC=13.560MHz, DATA is transmitting. Bold values indicate -20°C to 70°C unless otherwise noted. 1kbps data rate 50% duty cycle. RL 50 $\Omega$  load (matched)

|                  | _ ,                             |                  | Test Conditions                                                                                       |      | _     |      |        |

|------------------|---------------------------------|------------------|-------------------------------------------------------------------------------------------------------|------|-------|------|--------|

| Symbol           | Parameter                       | AV <sub>DD</sub> | Conditions                                                                                            | Min. | Тур.  | Max. | Unit   |

| I.               | Data High Comment               | 2) /             | @315MHz, POUT=+10dBm                                                                                  | _    | 12.5  | _    | mA     |

| l <sub>l</sub>   | Data High Current               | 3V               | @433.92MHz                                                                                            | _    | 12.5  | _    | mA     |

|                  | Data Laur Commant               | 2) /             | @315MHz                                                                                               | _    | 3.0   | _    | mA     |

| l <sub>o</sub>   | Data Low Current                | 3V               | @433.92 MHz                                                                                           | _    | 3.0   | _    | mA     |

| 1                | EN Low & DIN Low Current        | 3V               | @315MHz                                                                                               | _    | 1.0   | _    | μА     |

| I <sub>STB</sub> | EN LOW & DIN LOW Current        | 30               | @433.92 MHz                                                                                           |      | 1.0   |      | μА     |

| RF and C         | rystal                          |                  |                                                                                                       |      |       |      |        |

|                  | Output power level              | 3.3V             | @315MHz *                                                                                             | _    | 9.5   | _    | dBm    |

|                  |                                 |                  | @433.92MHz *                                                                                          |      | 9.5   |      | dBm    |

|                  | Harmonics output for 315 MHz    | 3V               | @630MHz, 2nd harm                                                                                     |      | -48   |      | dBc    |

|                  |                                 | 30               | @945MHz, 3rd harm                                                                                     | _    | -60   |      | dBc    |

|                  | Harmonics Output for 433.92MHz  | 3V               | @867.84MHz, 2nd harm                                                                                  |      | -45   |      | dBc    |

|                  |                                 | O V              | @1301.76MHz, 3rd harm                                                                                 | _    | -55   | _    | dBc    |

|                  | Extinction Ratio for ASK 10Kbps | 3V               | _                                                                                                     |      | 70    |      | dBc    |

|                  | Data Rate                       | 3V               | _                                                                                                     | 10   | _     |      | kbps   |

|                  | Occupied Bandwidth              | 3V               | @315MHz                                                                                               |      | <900  |      | kHz    |

|                  | Occupied Baridwidth             | 30               | @433.92MHz                                                                                            |      | <1000 |      | kHz    |

|                  | 315MHz Single Side Band Phase   | 3V               | 100kHz from Carrier                                                                                   |      | -78   | _    | dBc/Hz |

|                  | Noise                           | 30               | 1000kHz from Carrier                                                                                  |      | -77   |      | dBc/Hz |

|                  | 433.92MHz Single Side Band      | 3V               | 100kHz from Carrier                                                                                   |      | -78   |      | dBc/Hz |

|                  | Phase Noise                     | 30               | 1000kHz from Carrier                                                                                  | _    | -76   | _    | dBc/Hz |

|                  | XTLIN, XTLOUT                   | 3V               | Pin capacitance                                                                                       |      | 2     |      | pF     |

|                  | Output Blanking                 | 3V               | Standby transition from low to high **                                                                | _    | 500   | _    | μs     |

|                  | ASK to RF Out Response Time     | 3V               | Delta between ASK input<br>transition from Low To High<br>to RF output transition from<br>low to high | _    | 1     | _    | μs     |

|                  | CDEE Clock Output From          | 2)./             | @315MHz                                                                                               | _    | 150   | _    | Hz     |

|                  | CREF Clock Output Frequency     | 3V               | @433.92MHz                                                                                            | _    | 207   | _    | Hz     |

Note: \* Depend on PC board layout

<sup>\*\*</sup> Generally limited by crystal

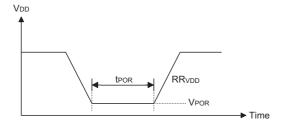

#### **Power-on Reset Characteristics**

Ta=25°C

| 0                                           | D                                             |                                                                    | Test Conditions                                                                | B.41  | T    | Maria | 1124 |

|---------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|-------|------|

| Symbol                                      | Parameter                                     | V <sub>DD</sub>                                                    | Conditions                                                                     | Min.  | Тур. | Max.  | Unit |

| V <sub>POR</sub>                            | VDD Start Voltage to Ensure<br>Power-on Reset | _                                                                  | _                                                                              | _     |      | 100   | mV   |

| RR <sub>VDD</sub>                           | VDD raising rate to Ensure<br>Power-on Reset  | _                                                                  | _                                                                              | 0.035 | _    | _     | V/ms |

| ,, Maximum V <sub>DD</sub> Start Voltage to |                                               | $Ta=25^{\circ}C,$ without $0.1\mu F$ between $V_{DD}$ and $V_{SS}$ | 0.9                                                                            | _     | 1.5  | V     |      |

| VPOR MAX                                    | V <sub>POR MAX</sub> Ensure Power-on Reset    |                                                                    | Ta=-40°C~85°C,<br>without 0.1μF between<br>V <sub>DD</sub> and V <sub>SS</sub> | 0.6   | _    | 1.8   | V    |

| ltp∩R                                       | Power-on Reset Low Pulse                      |                                                                    | without $0.1\mu F$ between $V_{DD}$ and $V_{SS}$                               | 2     | _    | _     | μs   |

|                                             | Width                                         |                                                                    | without $0.1\mu F$ between $V_{DD}$ and $V_{SS}$                               | TBD   | _    | _     | μs   |

## **Functional Description**

As these device packages contain different chips, for a detailed functional description, users must refer to the relevant datasheets for the related MCU. The following table shows which individual devices are inside each package.

| Device    | MCU      |  |  |  |  |

|-----------|----------|--|--|--|--|

| HT48R01T3 | HT48R01B |  |  |  |  |

| HT46R01T3 | HT46R01B |  |  |  |  |

#### **Multi-chip Internal Devices**

The MCU controls the RF transmitter via a two line interface using two of its I/O pins, PB0 and PB1. Pin PB1, which should be setup as an output by the MCU, is used to generate the encoding data. Pin PB0, which should be setup as an input by the MCU, is used for synchronising purposes. There are some special considerations which need to be taken into account when using these devices. These points will be mentioned in the hardware and software consideration sections.

#### **Hardware Considerations**

As these devices are composed of an individual MCU and RF Transmitter, using them together requires the user to take care of some special points.

Rev. 1.30 November 23, 2010

#### **Absolute Maximum Ratings**

The Absolute Maximum Ratings must be checked for discrepancies and the necessary care taken in device handling and usage.

#### **Power Supply**

Examination of the block diagram will reveal that the Power Supply and Ground pins of the RF Transmitter and MCU are independent and must be connected together if they are to share the same power supply. If the same power supply is to be used for both chips then care must be taken as both have different power supply requirements.

When calculating the total current consumption of the device, the internal DC specification currents for the MCU and RF parts must be added together.

The RF data to be transmitted is derived from the PB1 line. When the PB1 line is high the device will transmit allowing users to program their encoded data on this line. If the RF transmitter is in its standby mode then there will be a delay of about 500µs before transmission begins. When the device is transmitting, a synchronising signal will be generated on the CREF/PB0 pin which allows the MCU to use it to calibrate its internal RC oscillator. To avoid the RF circuits entering an unknown state, pin PB1 should be setup as an output as soon as possible after power-on.

To minimise power consumption, only when PB1 is high, can the RF signal be transmitted and the reference clock on PB0 be generated. If no data transitions are generated on PB1 for 300~500ms, the transmitter will enter a standby state and the RF circuits will be switched off along with the internal PLL to save power. The signal generated on the CREF/PB0 line will also remain at a low level. The internal PLL function is used to generate the RF frequency with a multiplier of 32 times the crystal frequency. The relationship is: RF frequency = 32 × Crystal frequency. Therefore a 9.84375MHz crystal will generate an RF frequency of 315MHz and a13.56MHz crystal will generate an RF frequency of 433.92MHz. All PLL circuits are contained within the device and the only external component required is a suitable crystal.

#### Power Down and Wake up

It is important to note that if the MCU is powered down or placed into a low power mode to conserve power, that the RF Transmitter may continue running and will consume a certain amount of power. Before powering down the MCU it is important to carefully manage the PB1 pin to ensure the RF-Transmitter enters its power down state.

#### **Programming Considerations**

As MCU lines PB0 and PB1 are used to control the RF transmitter function, care must be taken to manage these lines correctly in the application program. As line PB1 is used to send data to the RF circuitry this line must be setup as an output. To avoid erroneous operation of the RF circuits this line should be setup as an output immediately after power-on. The PB0 pin on the MCU is used to receive synchronising pulses from the RF circuits and should therefore be setup as an input.

As the MCU will be powered down independently of the RF Transmitter Peripheral Module, care must be taken to ensure that the MCU first clears its PB1 line to zero before powering down. This will allow the RF Transmitter Peripheral Module to enter its standby state and thus keep power consumption to a minimum

Rev. 1.30 11 November 23, 2010

## **Application Circuits**

Note: 1. 9.84375MHz crystal used for RF frequency of 315MHz 13.56MHz crystal used for RF frequency of 433.92MHz

- 2. The extra LC filter on the PAOUT pin can reduce second harmonics

- 3. The L and C values shown in brackets are for 433.92MHz

Rev. 1.30 12 November 23, 2010

## **Package Information**

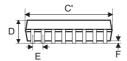

## 16-pin NSOP (150mil) Outline Dimensions

MS-012

| Comb al | Dimensions in inch |       |       |  |

|---------|--------------------|-------|-------|--|

| Symbol  | Min.               | Nom.  | Max.  |  |

| А       | 0.228              | _     | 0.244 |  |

| В       | 0.150              | _     | 0.157 |  |

| С       | 0.012              | _     | 0.020 |  |

| C'      | 0.386              | _     | 0.402 |  |

| D       | _                  | _     | 0.069 |  |

| Е       | _                  | 0.050 | _     |  |

| F       | 0.004              | _     | 0.010 |  |

| G       | 0.016              | _     | 0.050 |  |

| Н       | 0.007              | _     | 0.010 |  |

| α       | 0°                 | _     | 8°    |  |

| Cumbal | Dimensions in mm |      |       |  |

|--------|------------------|------|-------|--|

| Symbol | Min.             | Nom. | Max.  |  |

| Α      | 5.79             | _    | 6.20  |  |

| В      | 3.81             | _    | 3.99  |  |

| С      | 0.30             | _    | 0.51  |  |

| C'     | 9.80             | _    | 10.21 |  |

| D      | _                | _    | 1.75  |  |

| E      | _                | 1.27 | _     |  |

| F      | 0.10             | _    | 0.25  |  |

| G      | 0.41             | _    | 1.27  |  |

| Н      | 0.18             | _    | 0.25  |  |

| α      | 0°               | _    | 8°    |  |

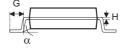

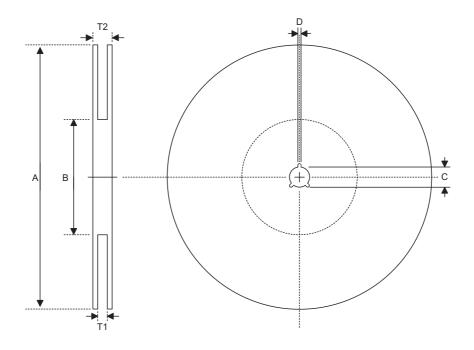

## **Reel Dimensions**

SOP 16N (150mil)

| Symbol | Description           | Dimensions in mm |

|--------|-----------------------|------------------|

| А      | Reel Outer Diameter   | 330.0±1.0        |

| В      | Reel Inner Diameter   | 100.0±1.5        |

| С      | Spindle Hole Diameter | 13.0 +0.5/-0.2   |

| D      | Key Slit Width        | 2.0±0.5          |

| T1     | Space Between Flange  | 16.8 +0.3/-0.2   |

| T2     | Reel Thickness        | 22.2±0.2         |

Rev. 1.30 14 November 23, 2010

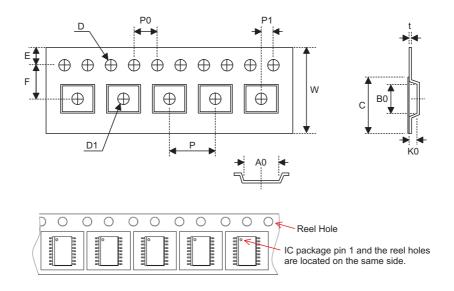

## **Carrier Tape Dimensions**

### SOP 16N (150mil)

| Symbol | Description                              | Dimensions in mm |

|--------|------------------------------------------|------------------|

| W      | Carrier Tape Width                       | 16.0±0.3         |

| Р      | Cavity Pitch                             | 8.0±0.1          |

| E      | Perforation Position                     | 1.75±0.1         |

| F      | Cavity to Perforation (Width Direction)  | 7.5±0.1          |

| D      | Perforation Diameter                     | 1.55 +0.10/-0.00 |

| D1     | Cavity Hole Diameter                     | 1.50 +0.25/-0.00 |

| P0     | Perforation Pitch                        | 4.0±0.1          |

| P1     | Cavity to Perforation (Length Direction) | 2.0±0.1          |

| A0     | Cavity Length                            | 6.5±0.1          |

| В0     | Cavity Width                             | 10.3±0.1         |

| К0     | Cavity Depth                             | 2.1±0.1          |

| t      | Carrier Tape Thickness                   | 0.30±0.05        |

| С      | Cover Tape Width                         | 13.3±0.1         |

Rev. 1.30 November 23, 2010

Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070 Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

#### Holtek Semiconductor Inc. (Shenzhen Sales Office)

5F, Unit A, Productivity Building, No.5 Gaoxin M 2nd Road, Nanshan District, Shenzhen, China 518057 Tel: 86-755-8616-9908, 86-755-8616-9308

Fax: 86-755-8616-9722

#### Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538, USA

Tel: 1-510-252-9880 Fax: 1-510-252-9885 http://www.holtek.com

#### Copyright © 2010 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.30 16 November 23, 2010