|                                         | TMP86C829B<br>TMP86CH29B<br>TMP86CM29B               | TMP86PM29A<br>TMP86PM29B              | TMP86C929AXB<br>(Emulation chip)<br>(Note 3) | TMP86FM29F                               |

|-----------------------------------------|------------------------------------------------------|---------------------------------------|----------------------------------------------|------------------------------------------|

| ROM                                     | 8 K (Mask ROM)<br>16 K (Mask ROM)<br>32 K (Mask ROM) | 32 K (OTP)                            | _                                            | 32 K (Flash)                             |

| RAM                                     | 512<br>1.5 K<br>1.5 K                                | 1.5 K                                 | _                                            | 2 K                                      |

| I/O                                     | 42                                                   | pin                                   | 42 pin (MCU part)                            | 42 pin                                   |

| External<br>Interrupt                   |                                                      | 5 pin                                 |                                              | 5 pin                                    |

| AD Converter                            | ŕ                                                    | 0-bit AD converter × 8                | 10-bit AD converter $\times$ 8 ch            |                                          |

| Timer Counter                           |                                                      | 18-bit timer $\times$ 1 ch            |                                              | 18-bit timer × 1 ch                      |

|                                         |                                                      | 8-bit timer $\times$ 4 ch             |                                              | 8-bit timer × 4 ch                       |

| Serial Interface                        |                                                      | 8-bit UART / SIO × 1                  | ch                                           | 8-bit UART / SIO × 1 ch                  |

| LCD                                     |                                                      | $32 \text{ seg} \times 4 \text{ com}$ |                                              | 32 seg × 4 com (Note 2)                  |

| Key-on<br>Wakeup                        |                                                      | 4 ch                                  |                                              | 4 ch                                     |

| Operating                               | 1.8 to 5.5 V                                         | at 4.2 MHz                            | 1.8 to 5.25 V at 4.2 MHz                     | 1.8 to 3.6 V at 4.2 MHz (External clock) |

| Voltage                                 | 2.7 to 5.5 \                                         | / at 8 MHz                            | 2.7 to 5.25 V at 8 MHz                       | 1.8 to 3.6 V at 8 MHz (Resonator)        |

| in MCU Mode                             | 4.5 to 5.5 V                                         | at 16 MHz                             | 4.5 to 5.25 V at 16 MHz                      | 2.7 to 3.6 V at 16 MHz                   |

| Operating<br>Temperature<br>in MCU Mode | –40 to 85°C                                          |                                       | 0 to 60°C                                    | –40 to 85°C                              |

| Writing to<br>Flash Memory              | _                                                    |                                       |                                              | 2.7 to 3.6V at 16 MHz<br>25°C ± 5°C      |

| CPU Wait (Note 1)                       |                                                      | N/A                                   |                                              | Available                                |

Comparison table of TMP86C829B/H29B/M29B/PM29A/PM29B/C929AXB and TMP86FM29

Note 1: The CPU wait is a CPU halt function for stabilizing of power supply of Flash memory. The CPU wait period is as follows. In the CPU wait period except RESET, CPU is halted but peripheral functions are not halted. Therefore, if the interrupt occurs during the CPU wait period, the interrupt latch is set. In this case, if the IMF has been set to "1", the interrupt service routine is executed after CPU wait period. For details refer to 2.14 "Flash Memory" in TMP86FM29 data sheet.

Thus, even if the same software is executed in 86FM29 and 86C829B/H29B/M29B/PM29A/PM29B /C929AXB, the operation process is not the same. Therefore, when the final operating confirmation on target application is executed for software development of Mask ROM Product (86C829B/H29B/M29B), not the Flash product (86FM29) but the OTP product (86PM29A/PM29B) should be used.

| Condition                                                                         | Wait Time              | Halt/Operate |             |  |  |

|-----------------------------------------------------------------------------------|------------------------|--------------|-------------|--|--|

| Condition                                                                         | Wait Time              | CPU          | Peripherals |  |  |

| After reset release                                                               | 2 <sup>10</sup> /fc[s] | Halt         | Halt        |  |  |

| Changing from STOP mode to NORMAL mode<br>(at EEPCR <mnpwdw> = "1")</mnpwdw>      | 2 <sup>10</sup> /fc[s] | Halt         | Operate     |  |  |

| Changing from STOP mode to SLOW mode<br>(at EEPCR <mnpwdw> = "1")</mnpwdw>        | 2 <sup>3</sup> /fs[s]  | Halt         | Operate     |  |  |

| Changing from IDLE0/1/2 mode to NORMAL mode<br>(at EEPCR <atpwdw> = "0")</atpwdw> | 2 <sup>10</sup> /fc[s] | Halt         | Operate     |  |  |

| Changing from SLEEP0/1/2 mode to SLOW mode<br>(at EEPCR <atpwdw> = "0")</atpwdw>  | 2 <sup>3</sup> /fs[s]  | Halt         | Operate     |  |  |

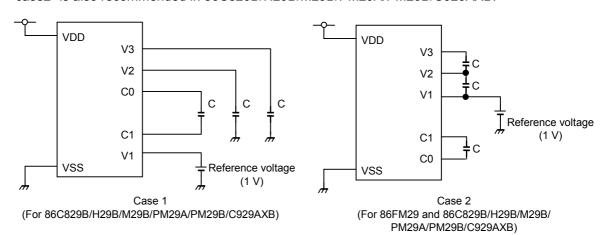

Note 2: The 86FM29 can not drive the 5V LCD panel because the electrical characteristics in 86FM29 is altered from 86C829B/H29B/M29B/PM29A/PM29B/C929AXB. The recommended operating condition of V3 pin in TMP86FM29 is 3.6V(max). For details, refer to "Electrical Characteristics". When the LCD booster circuit is used in 86FM29, connect the reference voltage and capacitor as shown in "case2". Though the method of "case1" has been recommended in 86C829B /H29B/M29B/PM29A/PM29B datasheets, the 86FM29 should not use method of "case1". Even if the method of "case1" is used in the 86C829B/H29B/M29B/PM29A/PM29B/C929AXB, the function and operation are not issue at all. However, if the "case2" is used, the booster ability becomes higher than "case1". Therefore, when the application board is designed newly in future, the method of "case2" is also recommended in 86C829B/H29B/M29B/PM29A/PM29B/C929AXB.

Note 3: Flash function, CPU wait period and serial PROM mode cannot be emulated in the 86C929AXB. If the software including the flash function is executed in 86C929AXB, the operation process differs from 86FM29.

### CMOS 8-Bit Microcontroller

# TMP86FM29UG/FG

The TMP86FM29 is the high-speed, high-performance and low power consumption 8-bit microcomputer, including FLASH, RAM, LCD driver, multi-function timer/counter, serial interface (UART/SIO), a 10-bit AD converter and two clock generators on chip.

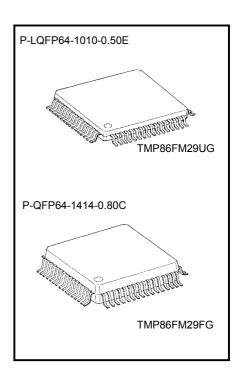

| Product No. | FLASH          | RAM           | Package             | Emulation Chip |

|-------------|----------------|---------------|---------------------|----------------|

| TMP86FM29UG | 22769 9 hite   | 1526 9 bito   | P-LQFP64-1010-0.50E |                |

| TMP86FM29FG | 32768 × 8 bits | 1536 × 8 bits | P-QFP64-1414-0.80C  | TMP86C929AXB   |

#### Feautures

- ◆ 8-bit single chip microcomputer TLCS-870/C series

- Instruction execution time: 0.25 μs (at 16 MHz)

122 μs (at 32.768 kHz)

- 132 types and 731 basic instructions

- 19 interrupt sources (External: 5, Internal: 14)

- Input/Output ports (39 pins)

(Out of which 24 pins are also used as SEG pins)

- 18-bit timer counter: 1 ch

- Timer, Event counter, Pulse width measurement, Frequencymeasurement modes

- ♦ 8-bit timer counter: 4 ch

- Timer, Event counter, PWM output, Programmable divider output, PPG output modes

- Time Base Timer

- Divider output function

030619EBP1

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products are used within specified operating ranges as set forth in the

damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

• The products described in this document are subject to the foreign exchange and foreign trade laws.

• TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

- ♦ Watchdog Timer

- Interrupt source/reset output (programmable)

- Serial interface

- 8-bit UART/SIO: 1ch

- 10-bit successive approximation type AD converter

- Analog input: 8 ch

- Four Key-On Wake-Up pins

- ◆ LCD driver/controller

- Built-in voltage booster for LCD driver

- With displaymemory

- LCD direct drive capability (max 32 seg × 4 com)

- 1/4, 1/3, 1/2 duties or static drive are programmably selectable

- Dual clock operation

- Single/Dual-clock mode

- Nine power saving operating modes

- STOP mode : Oscillation stops. Battery/Capacitor back-up. Port output hold/High-impedance.

- SLOW 1, 2 mode: Low power consumption operation using low-frequency clock (32.768 kHz)

- IDLE 0 mode : CPU stops, and peripherals operate using high-frequency clock of Time-Base-Timer. Release by falling edge of TBTCR <TBTCK> setting.

- IDLE 1 mode : CPU stops, and peripherals operate using high-frequency clock. Release by interruputs.

- IDLE 2 mode : CPU stops, and peripherals operate using high and low frequency clock. Release by interruputs.

- SLEEP 0 mode : CPU stops, and peripherals operate using low-frequency clock of Time-Base-Timer. Release by falling edge of TBTCR <TBTCK> setting.

- SLEEP 1 mode : CPU stops, and peripherals operate using low-frequency clock. Release by interrupts.

- SLEEP 2 mode : CPU stops, and peripherals operate using high and low frequency clock. Release by interrupts.

- ♦ Wide operating voltage: 1.8 to 3.6 V at 8 MHz/32.768 kHz

2.7 to 3.6 V at 16 MHz/32.768 kHz

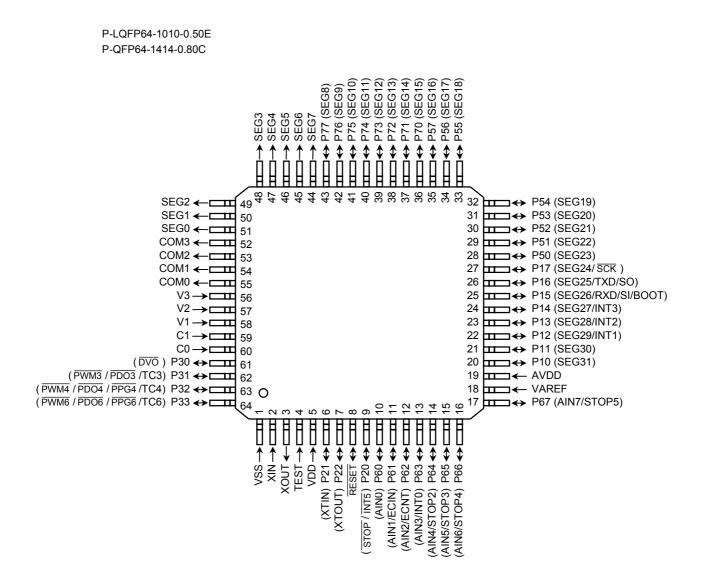

## Pin Assignments (Top View)

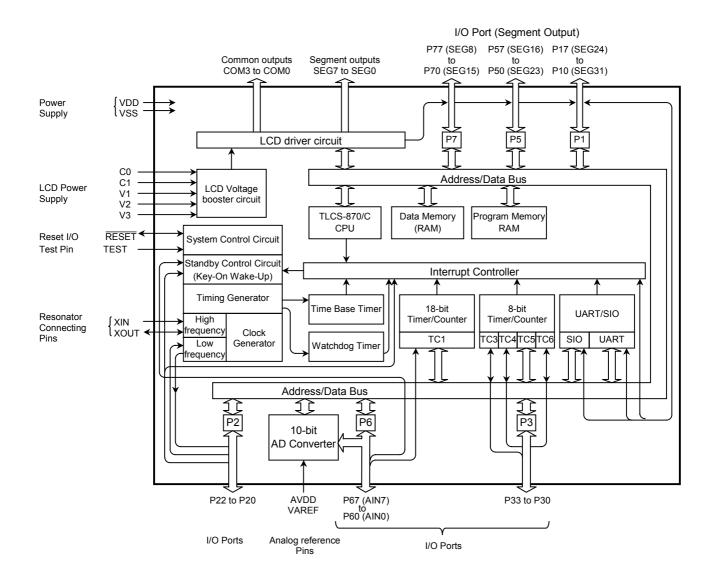

## Block Diagram

## **Pin Functions**

| Pin Name                                              | Input/Output           | Fu                                                                                     | inctions                                                 |                               |  |  |

|-------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|--|--|

| P17 (SEG24, SCK)                                      | I/O (I/O)              |                                                                                        | Serial clock input/output                                |                               |  |  |

| P16 (SEG25, TxD, SO)                                  |                        |                                                                                        | UART data output                                         |                               |  |  |

| F 10 (SEG25, TXD, SO)                                 | I/O (Output)           | 8-bit input/output port with latch.                                                    | Serial data output                                       |                               |  |  |

|                                                       |                        | When used as input port, an external                                                   | UART data input                                          |                               |  |  |

| P15 (SEG26, RxD, SI                                   | I/O (I/O)              | interrupt input, serial interface                                                      | Serial data input                                        |                               |  |  |

| BOOT)                                                 | - ( - )                | input/output and UART data                                                             | Serial PROM mode control                                 | LCD segment                   |  |  |

|                                                       |                        | input/output, the P1LCR must be set to                                                 | input                                                    | outputs.                      |  |  |

| P14 (SEG27, INT3)                                     | I/O (I/O)<br>I/O (I/O) | "0" after setting output latch to "1".<br>When used as a LCD segment output,           | External interrupt 3 input<br>External interrupt 2 input |                               |  |  |

| P13 (SEG28, INT2)<br>P12 (SEG29, INT1)                | I/O (I/O)              | the P1LCR must be set to "1".                                                          | External interrupt 1 input                               |                               |  |  |

| P11 (SEG30)                                           | I/O (Output)           |                                                                                        |                                                          |                               |  |  |

| P10 (SEG31)                                           | I/O (Output)           |                                                                                        |                                                          |                               |  |  |

| P22 (XTOUT)                                           | I/O (Output)           |                                                                                        | Resonator connecting pins                                | (32.768 kHz)                  |  |  |

| P21 (XTIN)                                            | I/O (Input)            | 3-bit input/output port with latch. When used as an input port, the output latch       | For inputting external clock,<br>XOUT is opened.         | XTIN is used and              |  |  |

| P20 ( INT5 , STOP )                                   | I/O (Input)            | must be set to "1".                                                                    | External interrupt input 5 or                            | STOP mode                     |  |  |

| P33 ( PWM6 , PDO6                                     | × 1 - 7                |                                                                                        | release signal input                                     |                               |  |  |

| PPG6 , TC6)                                           | I/O (I/O)              | 4-bit programmable input/output port (Nch high current output).                        | Timer counter 6 input/outpu                              | t                             |  |  |

| P32 ( <u>PWM4</u> , <u>PDO4</u><br><u>PPG4</u> , TC4) | I/O (I/O)              | When used as a timer/counter output or divider output, the output latch must be        | Timer counter 4 input/output                             |                               |  |  |

| P31 ( PWM3 , PDO3 ,                                   | I/O (I/O)              | set to "1". When used as an input port or timer/counter input, the P3OUTCR             | Timer counter 3 input/output                             |                               |  |  |

| TC3)<br>P30 ( DVO )                                   | I/O (Output)           | must be set to "0" after P3DR is set to "1".                                           | Divider output                                           |                               |  |  |

|                                                       |                        | 8-bit input/output port with latch.                                                    |                                                          |                               |  |  |

| P57 (SEG16) to                                        | I/O (Output)           | When used as a LCD segment output,                                                     | LCD segment outputs                                      |                               |  |  |

| P50 (SEG23)                                           | 、 <b>·</b> /           | the P5LCR must be set to "1".                                                          | 5 1                                                      |                               |  |  |

| P67 (AIN7, STOP5)                                     | I/O (Input)            | 8-bit programmable input/output port                                                   | STOP 5 input                                             |                               |  |  |

| P66 (AIN6, STOP4)                                     | I/O (Input)            | (tri-state). Each bit of this port can be                                              | STOP 4 input                                             |                               |  |  |

| P65 (AIN5, STOP3)                                     | I/O (Input)            | individually configured as an input or an output under software control. When          | STOP 3 input                                             |                               |  |  |

| P64 (AIN4, STOP2)                                     | I/O (Input)            | used as an analog input, the P6CR                                                      | STOP 2 input                                             |                               |  |  |

| P63 (AIN3, INTO)                                      | I/O (Input)            | must be set to "0" after setting output                                                | External interrupt 0 input                               | AD converter<br>analog inputs |  |  |

| · · ·                                                 | ,                      | latch to "0". When used as an input                                                    |                                                          | analog inputs                 |  |  |

| P62 (AIN2, ECNT)                                      | I/O (Input)            | port, a key on wake up input, an external interrupt input and timer/                   | Timer/Counter 1 input                                    |                               |  |  |

| P61 (AIN1, ECIN)                                      | I/O (Input)            | counter input, the P6CR must be set to                                                 |                                                          |                               |  |  |

| P60 (AIN0)                                            | I/O (Input)            | "0" after setting output latch to "1".                                                 |                                                          |                               |  |  |

| P77 (SEG8) to                                         |                        | 8-bit input/output port with latch.                                                    |                                                          |                               |  |  |

| P70 (SEG15)                                           | I/O (Output)           | When used as a LCD segment output,                                                     | LCD segment outputs                                      |                               |  |  |

|                                                       |                        | the P7LCR must be set to "1".                                                          |                                                          |                               |  |  |

| SEG7 to SEG0                                          | Output                 | LCD segment outputs                                                                    |                                                          |                               |  |  |

| COM3 to COM0                                          | •                      | LCD common outputs                                                                     |                                                          |                               |  |  |

| V3 to V1                                              | LCD voltage            | LCD voltage booster pin.                                                               |                                                          |                               |  |  |

| C1 to C0                                              | booster pin            | Capacitors are required between C0 and                                                 | C1 pin and V1/V2/V3 pin an                               | d GND.                        |  |  |

| XIN, XOUT                                             | Input Output           | Resonator connecting pins for high-frequ<br>For inputting external clock, XIN is used  |                                                          |                               |  |  |

| RESET                                                 | I/O                    | Reset signal input or watchdog timer reset output                                      |                                                          | itput/system clock            |  |  |

| TEST                                                  | Input                  | Test pin for out-going test, and the serial PROM mode control pin. Usually be fixed to |                                                          |                               |  |  |

|                                                       | •                      | low level. When the serial PROM mode s                                                 | starts, be fixed to "1".                                 |                               |  |  |

| VDD, VSS                                              |                        | +5 V, 0 (GND)                                                                          |                                                          |                               |  |  |

| VAREF                                                 | Power Supply           | Analog reference voltage inputs (High)                                                 |                                                          |                               |  |  |

| AVDD                                                  |                        | AD circuit power supply                                                                |                                                          |                               |  |  |

# **Operational Description**

# 1. CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller. This section provides a description of the CPU core, the program memory, the data memory, the external memory interface, and the reset circuit.

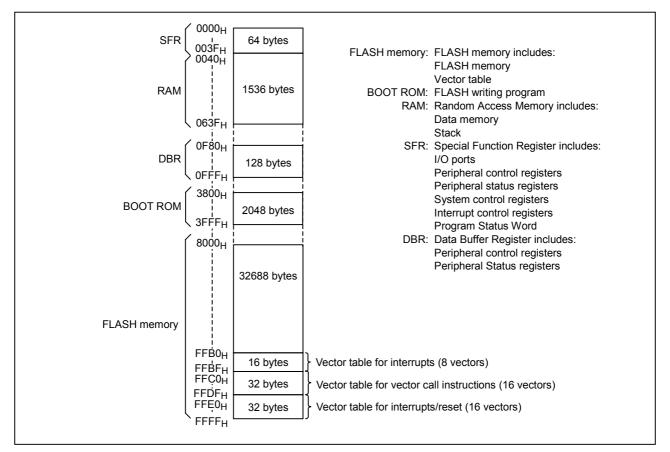

## 1.1 Memory Address Map

The TMP86FM29 memory consists of 5 blocks: FLASH memory, BOOT ROM, RAM, DBR (Data buffer register) and SFR (Special function register). They are all mapped in 64-Kbyte address space. Figure 1.1.1 shows the TMP86FM29 memory address map. The general-purpose registers are not assigned to the RAM address space.

Figure 1.1.1 Memory Address Maps

## 1.2 Program Memory (FLASH)

The TMP86FM29 has a 32 K  $\times$  8 bits (Address 8000H to FFFFH) of Flash memory.

# **Electrical Characteristics**

| Parameter                       | Symbol            | Pins                     | Rating                        | Unit |

|---------------------------------|-------------------|--------------------------|-------------------------------|------|

| Supply voltage                  | V <sub>DD</sub>   |                          | -0.3 to 4.0                   |      |

| Supply voltage                  | V <sub>LCD</sub>  | V3 pin                   | –0.3 to 4.0                   | v    |

| Input voltage                   | V <sub>IN</sub>   |                          | –0.3 to V <sub>DD</sub> + 0.3 | v    |

| Output voltage                  | V <sub>OUT1</sub> |                          | –0.3 to V <sub>DD</sub> + 0.3 |      |

|                                 | I <sub>OUT1</sub> | P3, P6 ports             | -1.8                          |      |

| Output current (Per 1 pin)      | IOUT2             | P1, P2, P5, P6, P7 ports | 3.2                           |      |

|                                 | I <sub>OUT3</sub> | P3 ports                 | 30                            | mA   |

| Output ourrent (Total)          | $\Sigma I_{OUT2}$ | P1, P2, P5, P6, P7 ports | 60                            |      |

| Output current (Total)          | ΣΙΟυτ3            | P3 ports                 | 80                            |      |

| Power dissipation [Topr = 85°C] | PD                |                          | 350                           | mW   |

| Soldering temperature (Time)    | Tsld              |                          | 260 (10 s)                    |      |

| Storage temperature             | Tstg              |                          | -55 to 125                    | °C   |

| Operating temperature           | Topr              |                          | -40 to 85                     |      |

Absolute Maximum Ratings  $(V_{SS} = 0 V)$

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

| Parameter                        | Symbol           | Pins                    | Con                                             | dition            | Min                  | Max                                                                                                                                                                                                                                                   | Unit |

|----------------------------------|------------------|-------------------------|-------------------------------------------------|-------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                  |                  |                         | fc = 16 MHz NORMAL1, 2 mode<br>IDLE0, 1, 2 mode |                   | 2.7                  | 2.7                                                                                                                                                                                                                                                   |      |

|                                  |                  |                         | fc = 8 MHz<br>(In case of connecting            | NORMAL1, 2 mode   |                      |                                                                                                                                                                                                                                                       |      |

|                                  |                  |                         | the resonator)                                  | IDLE0, 1, 2 mode  | 1.8                  |                                                                                                                                                                                                                                                       |      |

| Supply voltage V <sub>DI</sub>   | $V_{DD}$         |                         | fc = 4.2 MHz<br>(In case of external            | NORMAL1, 2 mode   | 1.0                  | 3.6                                                                                                                                                                                                                                                   |      |

|                                  |                  |                         | clock input)                                    | IDLE0, 1, 2 mode  |                      |                                                                                                                                                                                                                                                       |      |

|                                  |                  |                         | fs =                                            | SLOW1, 2 mode     |                      |                                                                                                                                                                                                                                                       |      |

|                                  |                  |                         | 32.768 kHz                                      | SLEEP0, 1, 2 mode | 1.8                  |                                                                                                                                                                                                                                                       | V    |

|                                  |                  |                         |                                                 | STOP mode         |                      |                                                                                                                                                                                                                                                       |      |

|                                  | V <sub>IH1</sub> | Except Hysteresis input | $V_{DD} \ge 2.7 V$<br>$V_{DD} < 2.7 V$          |                   | $V_{DD} \times 0.70$ |                                                                                                                                                                                                                                                       |      |

| Input high level V               | V <sub>IH2</sub> | Hysteresis input        |                                                 |                   | $V_{DD} \times 0.75$ | V <sub>DD</sub>                                                                                                                                                                                                                                       |      |

|                                  | V <sub>IH3</sub> |                         |                                                 |                   | $V_{DD} \times 0.90$ |                                                                                                                                                                                                                                                       |      |

|                                  | V <sub>IL1</sub> | Except Hysteresis input | $V_{DD} \ge 2.7 \text{ V}$                      |                   | 0                    | $V_{DD} \times 0.30$                                                                                                                                                                                                                                  |      |

| Input low level                  | V <sub>IL2</sub> | Hysteresis input        |                                                 |                   |                      | $V_{DD} \times 0.25$                                                                                                                                                                                                                                  |      |

|                                  | V <sub>IL3</sub> |                         | $V_{DD}$ < 2.7 V                                |                   |                      | $\begin{array}{c} 3 \\ 3 \\ 3 \\ 3 \\ 3 \\ 3 \\ 3 \\ 3 \\ 3 \\ 3 $                                                                                                                                                                                    |      |

| Clock frequency                  | fc               | XIN, XOUT               | $V_{DD} = 1.8$ to 3.6                           | V                 | 1.0                  | 8.0                                                                                                                                                                                                                                                   | MHz  |

| (In case of connecting           | ic               |                         | $V_{DD} = 2.7$ to 3.6                           | V                 | 1.0                  | $ \begin{array}{c} 0\\ 5\\ 5\\ 0\\ \hline 0\\ \hline \\ V_{DD} \times 0.30\\ \hline \\ V_{DD} \times 0.25\\ \hline \\ V_{DD} \times 0.10\\ \hline \\ 8.0\\ \hline 16.0\\ \hline 34.0\\ \hline 4.2\\ \hline 16.0\\ \hline 34.0\\ \hline 1.2\\ \hline $ |      |

| the resonator)                   | fs               | XTIN, XTOUT             | $V_{DD} = 1.8$ to 3.6                           | V                 | 30.0                 | 34.0                                                                                                                                                                                                                                                  | kHz  |

| Clock frequency                  | fc               | XIN, XOUT               | V <sub>DD</sub> = 1.8 to 3.6 V                  |                   | 1.0                  | 4.2                                                                                                                                                                                                                                                   | MHz  |

| (In case of external             | IC               |                         | $V_{DD} = 2.7$ to 3.6                           | V                 | 1.0                  | 16.0                                                                                                                                                                                                                                                  |      |

| clock input)                     | fs               | XTIN, XTOUT             | $V_{DD} = 1.8$ to 3.6                           | V                 | 30.0                 | 34.0                                                                                                                                                                                                                                                  | kHz  |

| LCD reference                    | V1               |                         | Booster circuit is enable $(V3 \ge V_{DD})$     |                   | 0.8                  | 1 0                                                                                                                                                                                                                                                   | V    |

| voltage                          | VI               |                         |                                                 |                   | 0.0                  | 1.2                                                                                                                                                                                                                                                   | v    |

| Capacity for LCD booster circuit | C <sub>LCD</sub> |                         | LCD booster circ<br>(V3 ≥ V <sub>DD</sub> )     | uit is enable     | 0.1                  | 0.47                                                                                                                                                                                                                                                  | μF   |

Recommended Operating Condition-1 (MCU mode)  $(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

Note: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (Supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

| Recommended Operating Condition-2 (Serial PROM mode) | $(V_{SS} = 0 V, Topr = 25^{\circ}C \pm 5^{\circ}C)$ |

|------------------------------------------------------|-----------------------------------------------------|

|------------------------------------------------------|-----------------------------------------------------|

| Parameter       | Symbol | Pins      | Condition                                        | Min | Max  | Unit |

|-----------------|--------|-----------|--------------------------------------------------|-----|------|------|

| Supply voltage  | VDD    |           | $2 \text{ MHz} \le \text{fc} \le 16 \text{ MHz}$ | 2.7 | 3.6  | V    |

| Clock frequency | fc     | XIN, XOUT | VDD = 2.7 to 3.6 V                               | 2.0 | 16.0 | MHz  |

Note: The operating temperature area of serial PROM mode is  $25^{\circ}C \pm 5^{\circ}C$  and the operating area of high frequency of serial PROM mode is different from MCU mode.

| Parameter                           | Symbol              |                            | Pir       | าร                                                       | Cond                                                                     | Condition               |     | Тур.   | Max  | Unit   |

|-------------------------------------|---------------------|----------------------------|-----------|----------------------------------------------------------|--------------------------------------------------------------------------|-------------------------|-----|--------|------|--------|

| Hysteresis voltage                  | V <sub>HS</sub>     | Hyste                      | eresis in | out                                                      | V <sub>DD</sub> = 3.3 V                                                  | V <sub>DD</sub> = 3.3 V |     | 0.4    | -    | V      |

|                                     | I <sub>IN1</sub>    | TEST                       | -         |                                                          | $V_{DD} = 3.6 \text{ V}, \text{ V}_{IN}$                                 | = 0 V                   | -   | -      | -5   |        |

| Input current                       | I <sub>IN2</sub>    | Sink                       | open dra  | ain, Tri-state                                           | $V_{DD} = 3.6 \text{ V}, \text{ V}_{IN}$                                 | = 3.6 V/0 V             | _   | -      | ±5   | μA     |

|                                     | I <sub>IN3</sub>    | RESE                       | T         |                                                          | V <sub>DD</sub> = 3.6 V, V <sub>IN</sub>                                 | = 3.6 V                 | -   | -      | +5   |        |

|                                     | R <sub>IN1</sub>    | TEST                       | pull do   | wn                                                       | $V_{DD}=3.6\ V,\ V_{IN}$                                                 | = 3.6 V                 | -   | 70     | -    | ko     |

| Input resistance                    | R <sub>IN2</sub>    | RESE                       | T pull u  | ıp                                                       | $V_{DD} = 3.6 \text{ V}, \text{ V}_{IN}$                                 | = 0 V                   | 100 | 220    | 450  | kΩ     |

| High frequency<br>feedback resistor | R <sub>FB</sub>     | XOU                        | Т         |                                                          | V <sub>DD</sub> = 3.6 V                                                  |                         | -   | 3      | -    | MΩ     |

| Low frequency<br>feedback resistor  | R <sub>FBT</sub>    | ΧΤΟΙ                       | JT        |                                                          | $V_{DD} = 3.6 V$                                                         |                         | _   | 20     | I    | 1012 2 |

| Output leakage<br>current           | I <sub>LO</sub>     | Sink open drain, Tri-state |           | V <sub>DD</sub> = 3.6 V<br>V <sub>OUT</sub> = 3.4V/0.2 V |                                                                          | -                       | -   | ±10    | μA   |        |

| Output high voltage                 | VOH                 | CMOS, Tri-state            |           | $V_{DD} = 3.6 \text{ V}, I_{OH} = -0.6 \text{ mA}$       |                                                                          | 3.2                     | -   | -      | v    |        |

| Output low voltage                  | V <sub>OL</sub>     | Except XOUT, P3 port       |           | $V_{DD} = 3.6 \text{ V}, I_{OL} = 0.9 \text{ mA}$        |                                                                          | -                       | -   | 0.4    | V    |        |

| Output low current                  | I <sub>OL</sub>     | P3 pc                      | ort       |                                                          | $V_{DD} = 3.6 \text{ V}, V_{OL} = 1.0 \text{ V}$                         |                         | -   | 6      | ١    | mA     |

| LCD output voltage                  |                     | V2 pi                      | n         |                                                          | V3 ≥ V <sub>DD</sub><br>Reference supply pin: V1<br>SEG/COM pin: No load |                         | _   | V1 x 2 | _    |        |

| (LCD booster is enable)             | V <sub>2-3OUT</sub> | V3 pi                      | n         |                                                          |                                                                          |                         | -   | V1 x 3 | _    | V      |

| Supply current in                   |                     |                            | Fetch     | Flash area                                               | V <sub>DD</sub> = 3.6 V                                                  | MNP = "1"               | -   | 5.3    | 7.3  |        |

| NORMAL 1, 2 mode                    |                     |                            | area      | RAM area                                                 | $V_{IN} = 3.4 \text{ V}/0.2 \text{ V}$                                   | MNP = "0"               | -   | 3.4    | 5.2  | mA     |

| Supply current in                   |                     |                            |           |                                                          | fc = 16 MHz                                                              | MNP•ATP = "1"           | -   | 3.1    | 5.2  |        |

| IDLE 0, 1, 2 mode                   |                     |                            |           | n                                                        | fs = 32.768 kHz                                                          | MNP•ATP = "0"           | -   | 2.2    | 4.2  |        |

| Supply current in                   |                     |                            | Fetch     | Flash area                                               | -                                                                        | MNP = "1"               | -   | 850    | 1200 |        |

| SLOW 1 mode                         |                     |                            | area      | RAM area                                                 | V <sub>DD</sub> = 3.0 V                                                  | MNP = "0"               | -   | 7      | 19   |        |

| Supply current in                   |                     |                            |           |                                                          | $V_{\rm IN} = 2.8  \rm V/0.2  \rm V$                                     | MNP•ATP = "1"           | -   | 850    | 1200 | μA     |

| SLEEP 1 mode                        |                     |                            |           |                                                          | fs = 32.768 kHz                                                          | MNP•ATP = "0"           | -   | 5.5    | 17   |        |

| Supply current in                   |                     |                            |           |                                                          |                                                                          | MNP•ATP = "1"           | -   | 850    | 1200 |        |

| SLEEP 0 mode                        | -                   |                            |           |                                                          |                                                                          | MNP•ATP = "0"           | -   | 4.5    | 15   |        |

| Supply current in<br>STOP mode      |                     |                            |           |                                                          | V <sub>DD</sub> = 3.6 V<br>V <sub>IN</sub> = 3.4 V/0.2 V                 |                         | -   | 0.5    | 10   |        |

DC Characteristics  $(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

Note 1: Typical values show those at Topr =  $25^{\circ}$ C.

Note 2: Input current ( $I_{IN1}$ ,  $I_{IN2}$ ): The current through pull-up or pull-down resistor is not included.

Note 3:  $I_{DD}$  does not include  $I_{REF}$  current.

- Note 4: The supply currents of SLOW2 and SLEEP2 modes are equivalent to IDLE0, IDLE1, IDLE2.

- Note 5: MNP (MNPWDW) shows bit0 in EEPCR register and ATP (ATPWDW) shows bit1 in EEPCR register.

- Note 6: "Fetch" means reading operation of FLASH data as an instruction by CPU.

(V\_{SS} = 0.0 V, 2.7 V  $\leq$  V\_{DD}  $\leq$  3.6 V, Topr = -40 to 85°C)

| Parameter                                         | Symbol            | Condition                                              | Min                    | Тур.            | Max               | Unit |

|---------------------------------------------------|-------------------|--------------------------------------------------------|------------------------|-----------------|-------------------|------|

| Analog reference voltage                          | VAREF             |                                                        | A <sub>VDD</sub> - 1.0 | -               | A <sub>VDD</sub>  |      |

| Power supply voltage of analog<br>control circuit | A <sub>VDD</sub>  |                                                        |                        | V <sub>DD</sub> |                   | V    |

| Analog reference voltage range<br>(Note 4)        | $\Delta V_{AREF}$ |                                                        | 2.5                    | _               | -                 | V    |

| Analog input voltage                              | V <sub>AIN</sub>  |                                                        | V <sub>SS</sub>        | -               | V <sub>AREF</sub> |      |

| Power supply current of analog reference voltage  | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 3.6 V$ $V_{SS} = 0.0 V$ | _                      | 0.35            | 0.61              | mA   |

| Non linearity error                               |                   | V <sub>DD</sub> = A <sub>VDD</sub> = 2.7 V             | _                      | I               | ±2                |      |

| Zero point error                                  |                   |                                                        | _                      | I               | ±2                | LSB  |

| Full scale error                                  |                   | $V_{SS} = 0.0 V$                                       | _                      | -               | ±2                | LOD  |

| Total error                                       |                   | V <sub>AREF</sub> = 2.7 V                              | -                      | -               | ±2                |      |

$(V_{SS} = 0.0 \text{ V}, 2.0 \text{ V} \le V_{DD} < 2.7 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                        | Symbol            | Condition                                                | Min                    | Тур.            | Max              | Unit |

|--------------------------------------------------|-------------------|----------------------------------------------------------|------------------------|-----------------|------------------|------|

| Analog reference voltage                         | VAREF             |                                                          | A <sub>VDD</sub> - 0.6 | _               | A <sub>VDD</sub> |      |

| Power supply voltage of analog control circuit   | A <sub>VDD</sub>  |                                                          |                        | V <sub>DD</sub> |                  | V    |

| Analog reference voltage range<br>(Note 4)       | $\Delta V_{AREF}$ |                                                          | 2.0                    | _               | -                | v    |

| Analog input voltage                             | V <sub>AIN</sub>  |                                                          | V <sub>SS</sub>        | _               | VAREF            |      |

| Power supply current of analog reference voltage | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 2.0V$<br>$V_{SS} = 0.0 V$ | -                      | 0.20            | 0.34             | mA   |

| Non linearity error                              |                   | VD = AVD = 2.0 V                                         | _                      | _               | ±4               |      |

| Zero point error                                 |                   | 55 155                                                   | -                      | -               | ±4               | LSB  |

| Full scale error                                 |                   | $V_{SS} = 0.0 V$                                         | -                      | _               | ±4               | LOD  |

| Total error                                      |                   | V <sub>AREF</sub> = 2.0 V                                | -                      | -               | ±4               |      |

#### $(V_{SS}=0.0$ V, 1.8 V $\leq V_{DD} < 2.0$ V, Topr = -10 to 85°C) (Note 5)

| Parameter                                        | Symbol                           | Condition                                              | Min             | Тур. | Max              | Unit |  |

|--------------------------------------------------|----------------------------------|--------------------------------------------------------|-----------------|------|------------------|------|--|

| Analog reference voltage                         | V <sub>AREF</sub>                |                                                        | $A_{VDD} - 0.1$ | _    | A <sub>VDD</sub> |      |  |

| Power supply voltage of analog control circuit   | A <sub>VDD</sub> V <sub>DI</sub> |                                                        |                 |      | V <sub>DD</sub>  |      |  |

| Analog reference voltage<br>range (Note 4)       | $\Delta V_{AREF}$                |                                                        | 1.8             | _    | -                | V    |  |

| Analog input voltage                             | V <sub>AIN</sub>                 |                                                        | V <sub>SS</sub> | _    | VAREF            |      |  |

| Power supply current of analog reference voltage | I <sub>REF</sub>                 | $V_{DD} = A_{VDD} = V_{AREF} = 1.8 V$ $V_{SS} = 0.0 V$ | -               | 0.18 | 0.31             | mA   |  |

| Non linearity error                              |                                  | V <sub>D</sub> = A <sub>VD</sub> = 1.8 V               | -               | -    | ±4               |      |  |

| Zero point error                                 |                                  | 55 155                                                 | -               | -    | ±4               | LSB  |  |

| Full scale error                                 |                                  | $V_{SS} = 0.0 V$                                       | -               | _    | ±4               | LOD  |  |

| Total error                                      |                                  | V <sub>AREF</sub> = 1.8 V                              | _               | -    | <u>+</u> 4       |      |  |

Note 1: The total error includes all errors except a quantization error, and is defined as a maximum deviation from the ideal conversion line.

Note 2: Conversion time is different in recommended value by power supply voltage. About conversion time, please refer to "2.15.2 Register configration".

Note 3: Please use input voltage to AIN input Pin in limit of VAREF – VSS. When voltage of range outside is input, conversion value becomes unsettled and gives affect to other channel conversion value.

- Note 4: Analog Reference Voltage Range:  $\triangle VAREF = VAREF VSS$

- Note 5: When AD is used with VDD < 2.0 V, the guaranteed temperature range varies with the operating voltage.

- Note 6: When AD converter is not used, fix the AVDD pin and VAREFpin on the  $V_{DD}$  level.

### AC Characteristics $(V_{SS} = 0 \text{ V}, V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                                   | Symbol       | Condition                                                  | Min   | Тур.  | Max         | Unit |

|-------------------------------------------------------------|--------------|------------------------------------------------------------|-------|-------|-------------|------|

| Machine cycle time                                          | tcy          | NORMAL1, 2 mode<br>IDLE1, 2 mode                           | 0.25  | -     | 4           |      |

|                                                             |              | SLOW1, 2 mode<br>SLEEP1, 2 mode                            | 117.6 | _     | μs<br>133.3 |      |

| High Level clock pulse width<br>Low level clock pulse width | twcH<br>twcL | For external clock operation (XIN input), fc = 16 MHz      | -     | 31.25 | _           | ns   |

| High level clock pulse width<br>Low level clock pulse width | twcH<br>twcL | For external clock operation (XTIN input), fs = 32.768 kHz | _     | 15.26 | _           | μS   |

#### $(V_{SS} = 0 \text{ V}, V_{DD} = 1.8 \text{ to } 3.6 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                                   | Symbol       | Condition                                                  | Min   | Тур.                 | Max | Unit |

|-------------------------------------------------------------|--------------|------------------------------------------------------------|-------|----------------------|-----|------|

| Machine cycle time                                          | tcy          | NORMAL1, 2 mode<br>IDLE1, 2 mode                           | 0.5   | _                    | 4   |      |

|                                                             |              | SLOW1, 2 mode<br>SLEEP1, 2 mode                            | 117.6 | – 133.3 <sup>µ</sup> | μS  |      |

| High level clock pulse width<br>Low level clock pulse width | twcH<br>twcL | For external clock operation (XIN input), fc = 4.2 MHz     | _     | 119.04               | _   | ns   |

| High level clock pulse width<br>Low level clock pulse width | twcH<br>twcL | For external clock operation (XTIN input), fs = 32.768 kHz | -     | 15.26                | -   | μS   |

Timer Counter 1 input (ECIN) Characteristics (V<sub>SS</sub> = 0 V, Topr = -40 to 85°C)

| Parameter                               | Symbol                | Condition                    |                   | Min | Тур. | Max | Unit |

|-----------------------------------------|-----------------------|------------------------------|-------------------|-----|------|-----|------|

| TC1 input (ECIN input) t <sub>TC1</sub> | Frequency measurement | Single edge count            | _                 | _   | 16   |     |      |

|                                         | t <sub>TC1</sub>      | mode $V_{DD}$ = 2.7 to 3.6 V | Both edge count   |     |      | 10  | MHz  |

|                                         |                       | Frequency measurement        | Single edge count | _   | _    | 8   |      |

|                                         |                       | mode $V_{DD}$ = 1.8 to 2.7 V | Both edge count   |     |      |     |      |

Flash Characteristics  $| (V_{SS} = 0 V) |$

| Parameter                                                                            | Condition                                                                                                        | Min | Тур. | Max             | Unit  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|------|-----------------|-------|

| Number of guaranteed writes (page<br>writing) to Flash memory in serial PROM<br>mode | $V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, 2 \text{ MHz} \le \text{fc} \le 16 \text{ MHz}$ (Topr = 25°C $\pm$ 5°C) | -   | -    | 10 <sup>5</sup> | Times |

Recommended Oscillating Conditions

- Note 1: An electrical shield by metal shield plate on the surface of IC package is recommended in order to protect the device from the high electric field stress applied from CRT (Cathodic Ray Tube) for continuous reliable operation.

- Note 2: The product numbers and specifications of the resonators by Murata Manufacturing Co., Ltd. are subject to change. For up-to-date information, please refer to the following http://www.murata.co.jp/search/index.html